Method for manufacturing gate oxide layer of EEPROM and gate oxide layer manufactured thereby

A technology of gate oxide layer and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of long time required, many process steps, high manufacturing cost, etc., speed up the speed and reduce the manufacturing cost Effect of reducing cost and manufacturing time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The manufacture method of the gate oxide layer of EEPROM of the present invention comprises the steps:

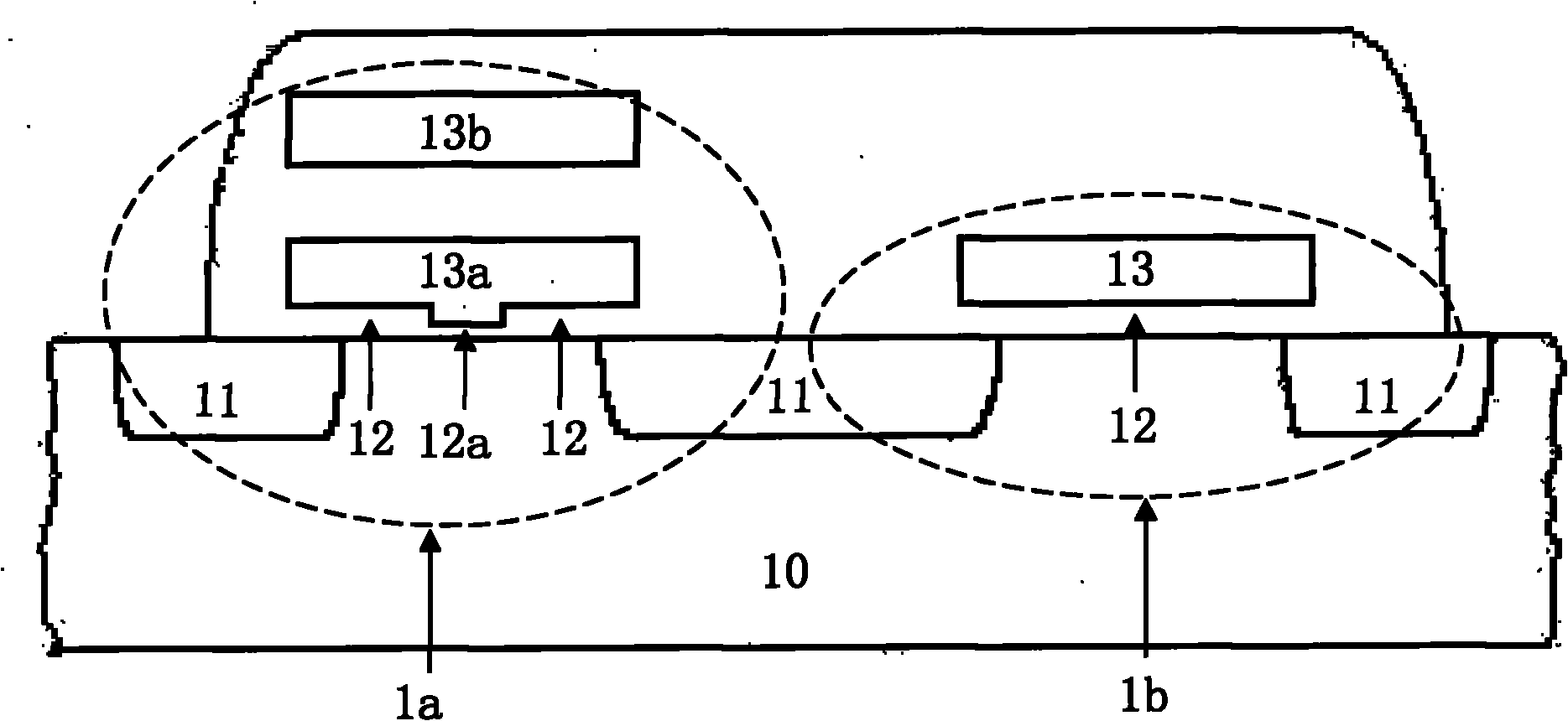

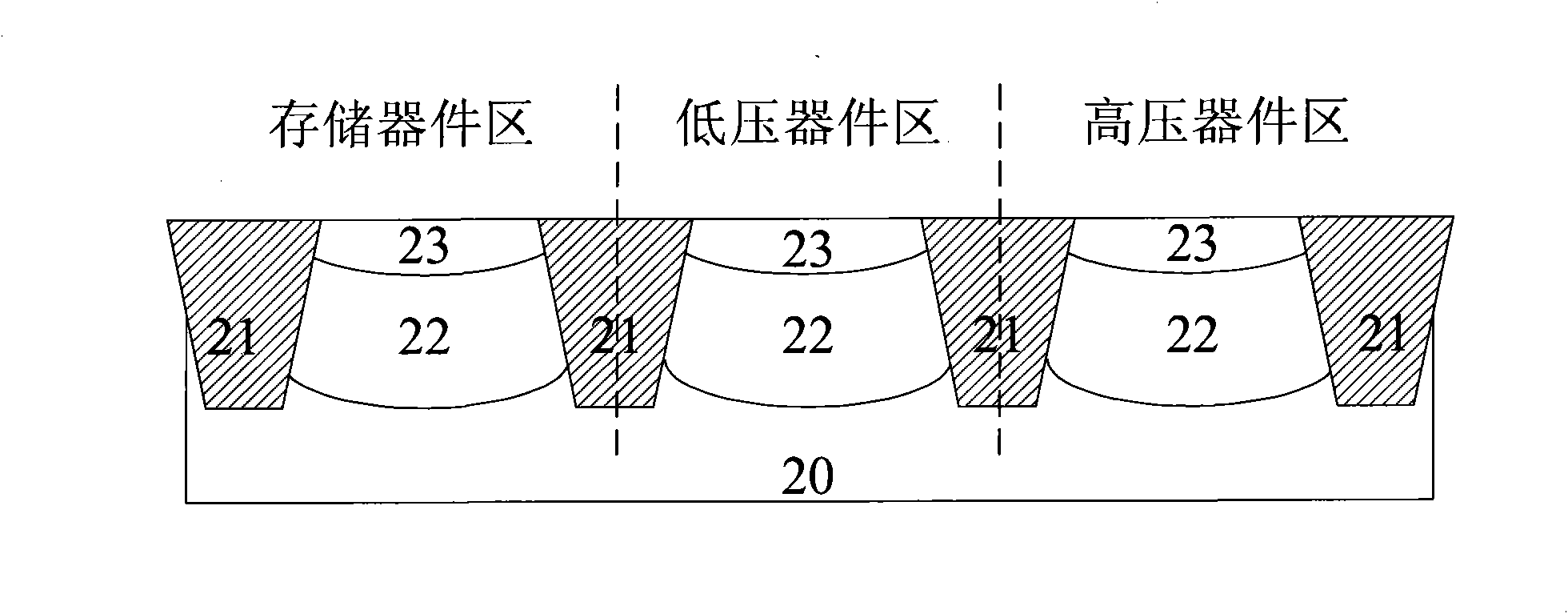

[0031] The initial state of the silicon wafer is: an isolation region 21 has been formed in the silicon substrate 20 by a field oxygen isolation (LOCOS) or shallow trench isolation (STI) process, and a p-well 22 is also formed in the silicon substrate 20 by an ion implantation process, Multiple p-wells 22 are isolated by multiple isolation regions 21 .

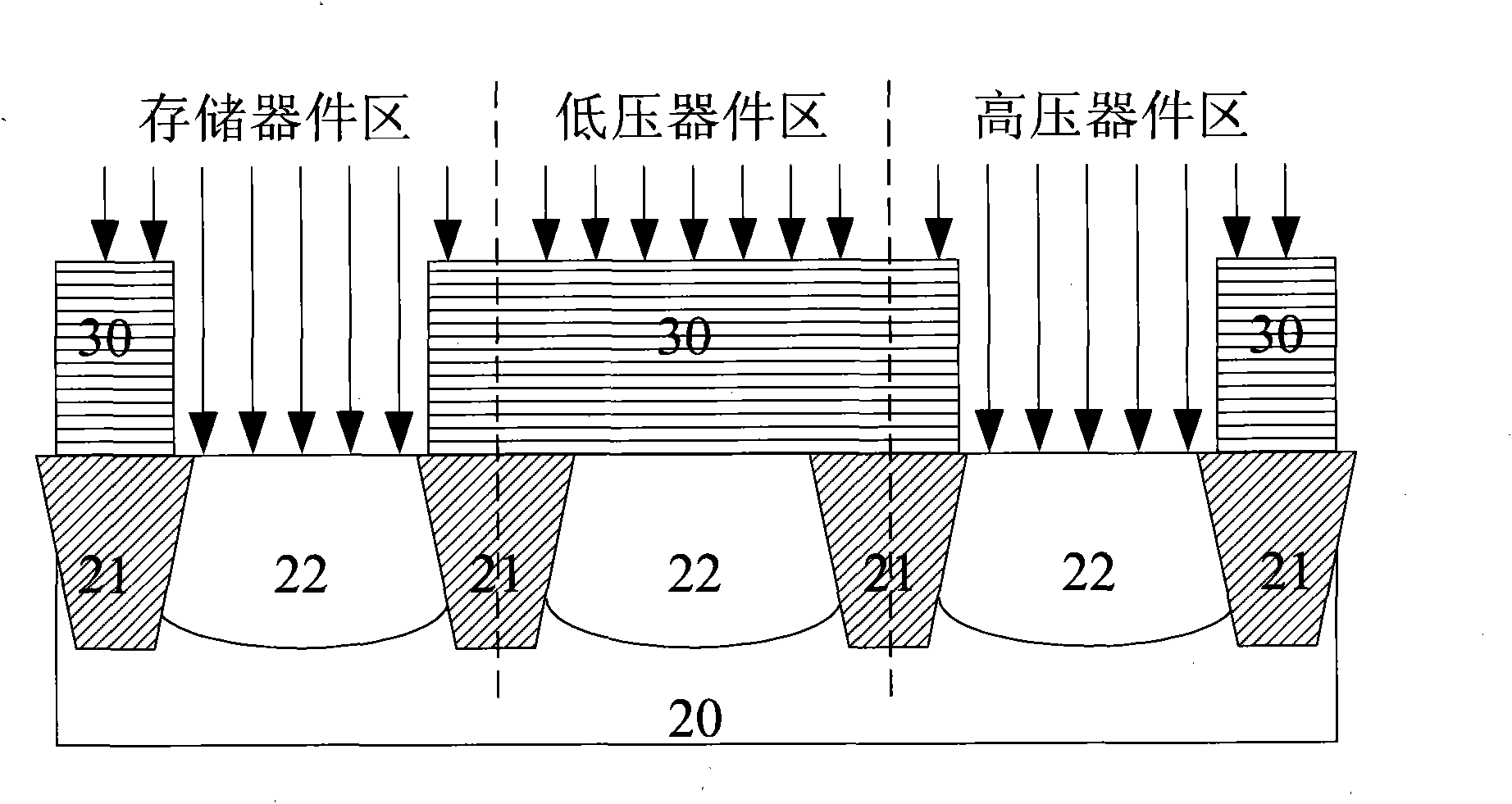

[0032] Step 1, see Figure 3a Spin-coat a layer of photoresist 30 on the surface of the silicon wafer. After exposure and development, the photoresist 30 only covers the low-voltage device region and the region where the tunnel oxide layer will be formed. In the storage device region, the region other than the tunnel oxide layer is exposed. , the high-voltage device area is fully exposed. Ion (atom) implantation is performed on the surface of the silicon wafer, and the photoresist 30 serves as a barrier layer for i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More