Patents

Literature

108results about How to "Simple manufacturing process steps" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

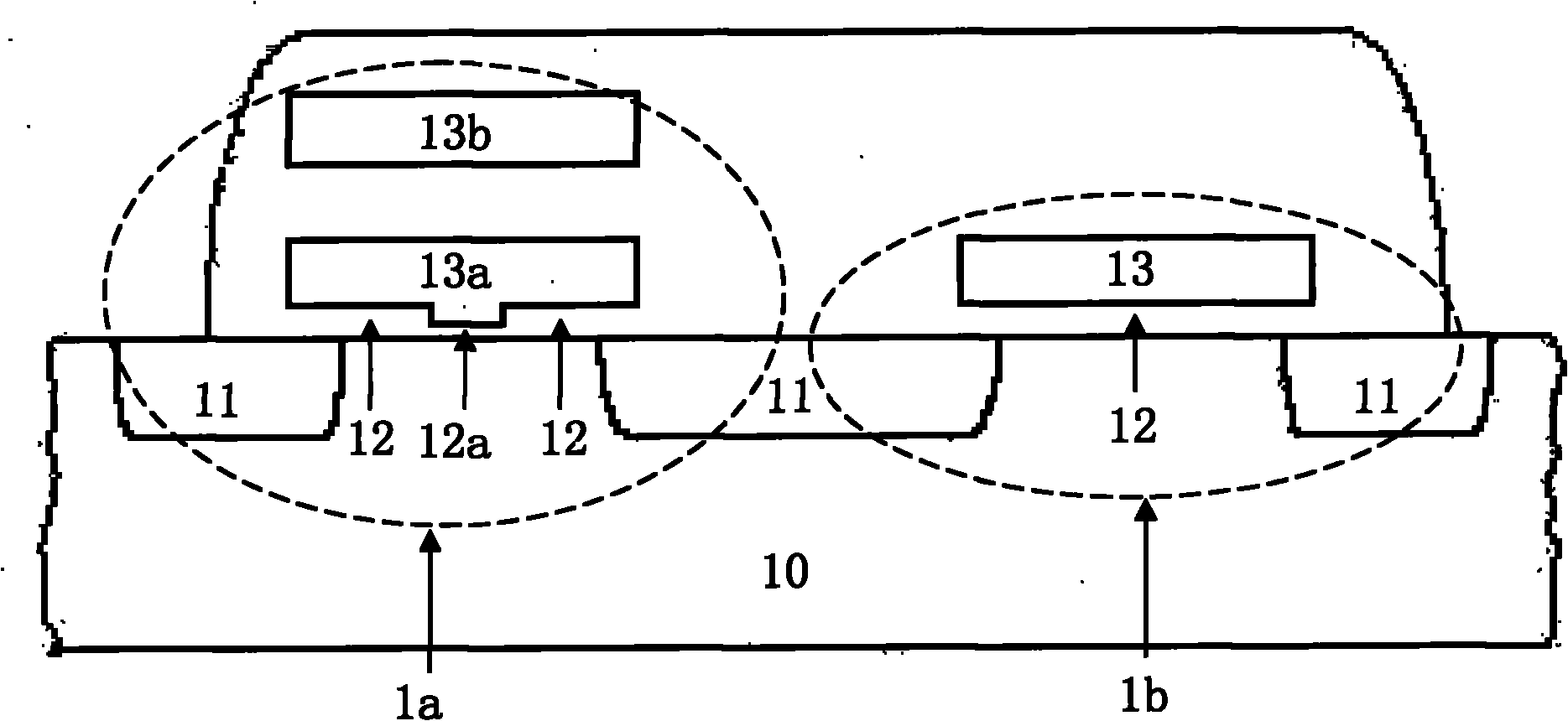

Process for making tripolar carbon nanotube field emission display having self-aligning technique

InactiveCN1700389AGood device performanceReduce manufacturing costImage/pattern display tubesCold cathode manufactureCarbon nanotubeControl grid

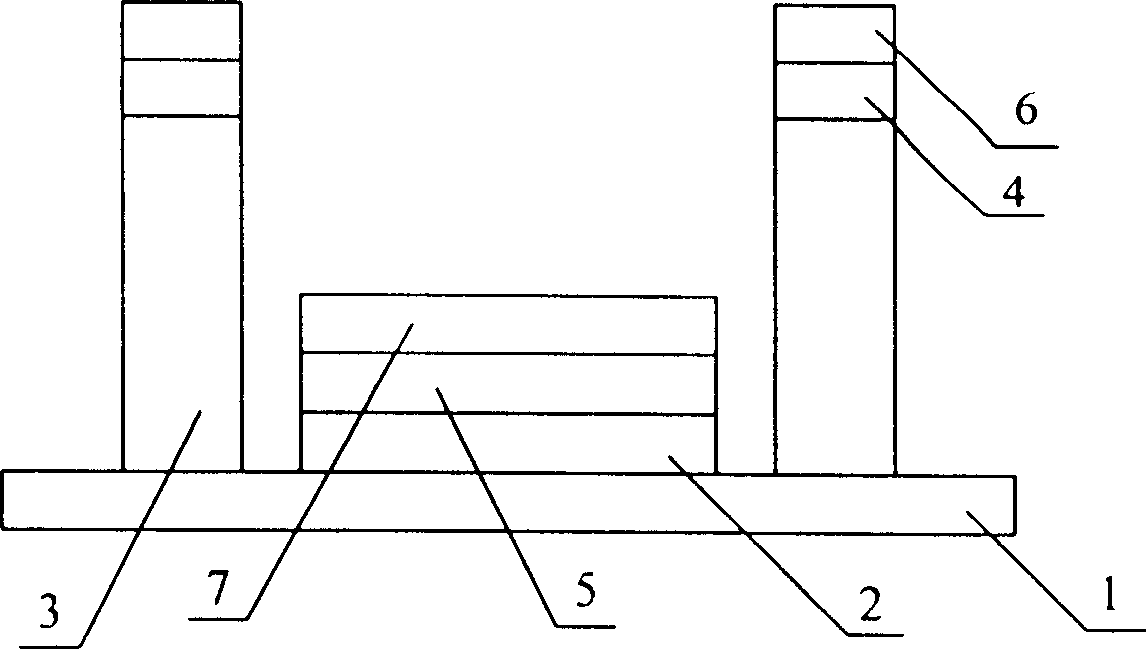

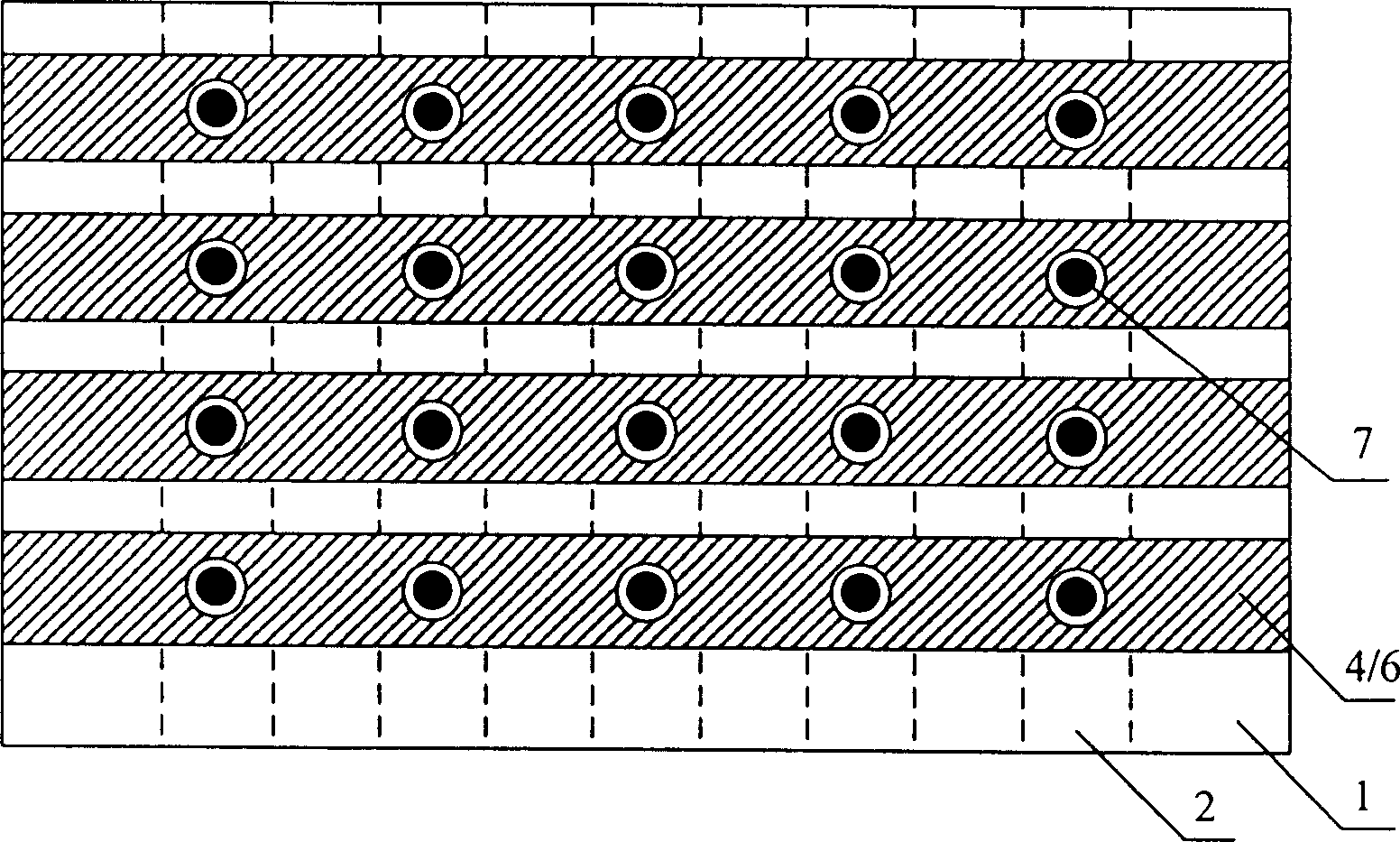

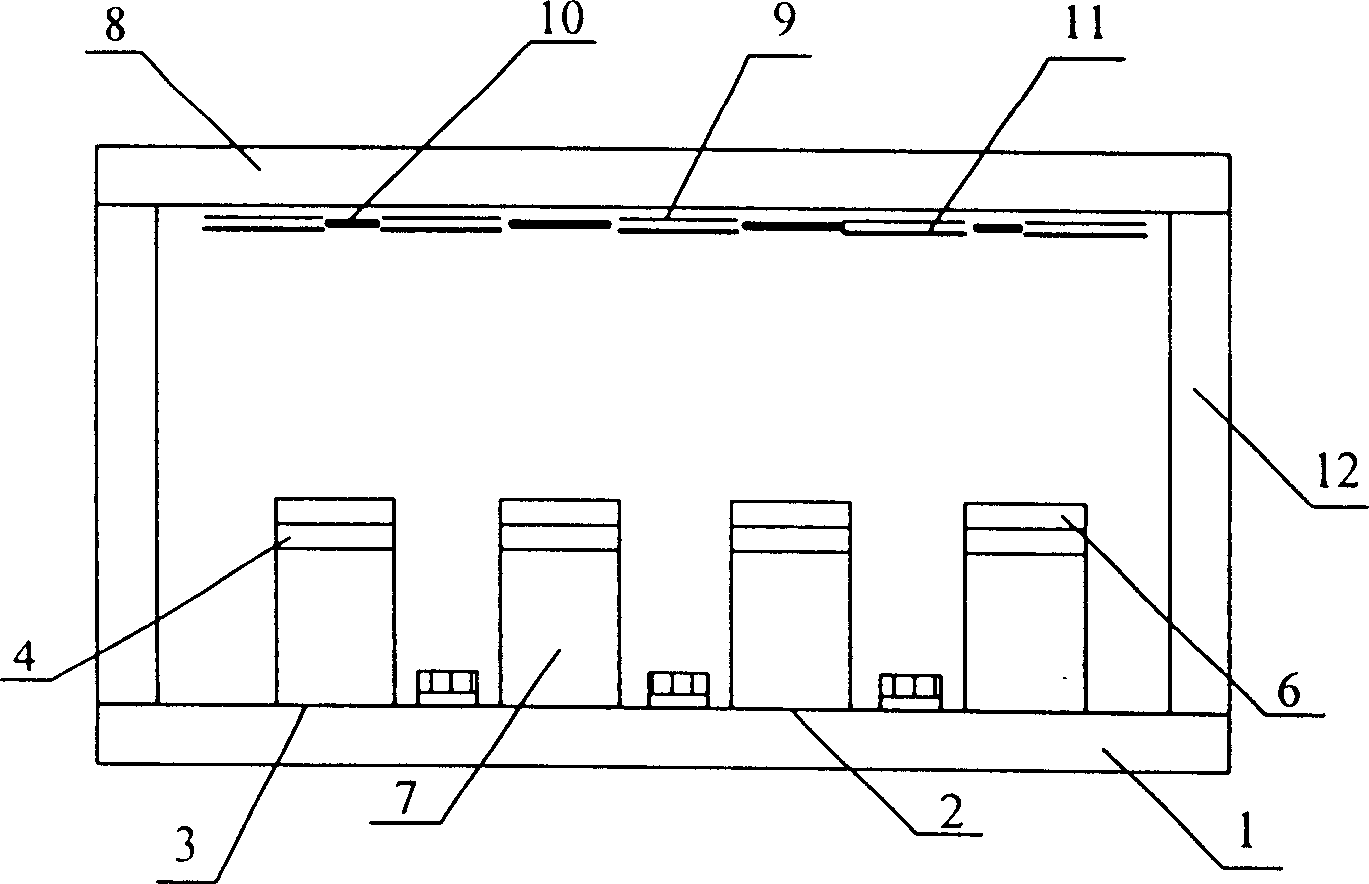

This invention relates to carbon nanometer tube negative electrode structure eradiation display device, wherein, the display comprises negative panel, positive panel and glass closure frame formed sealed vacuum chamber, wherein, the positive panel is grown with carbon nanometer negative electrode located on the top of the negative electrode to control the electron eradiation control grid electrode and adopts self-aligning process.

Owner:ZHONGYUAN ENGINEERING COLLEGE

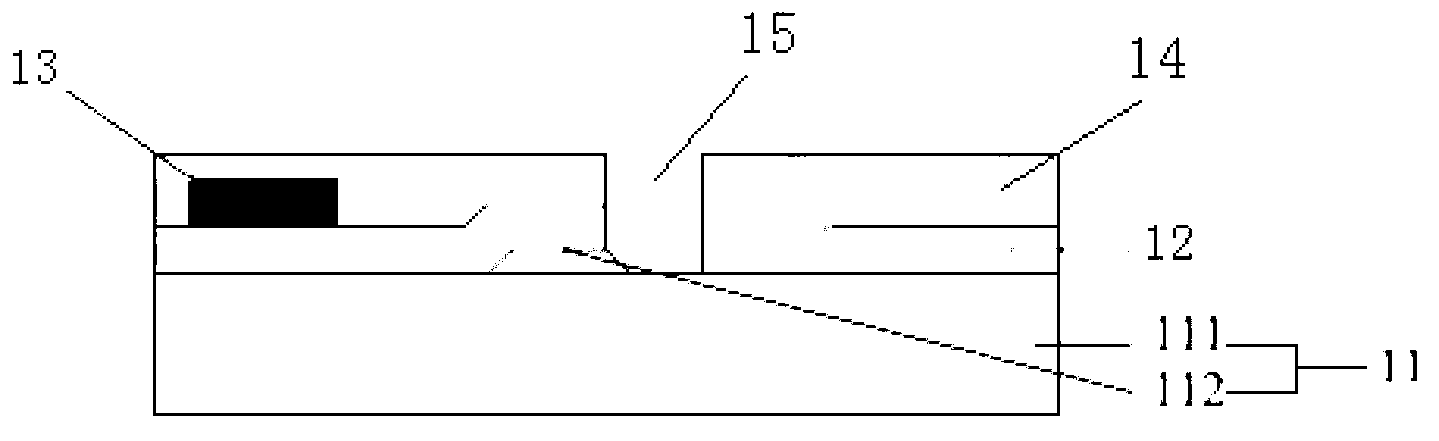

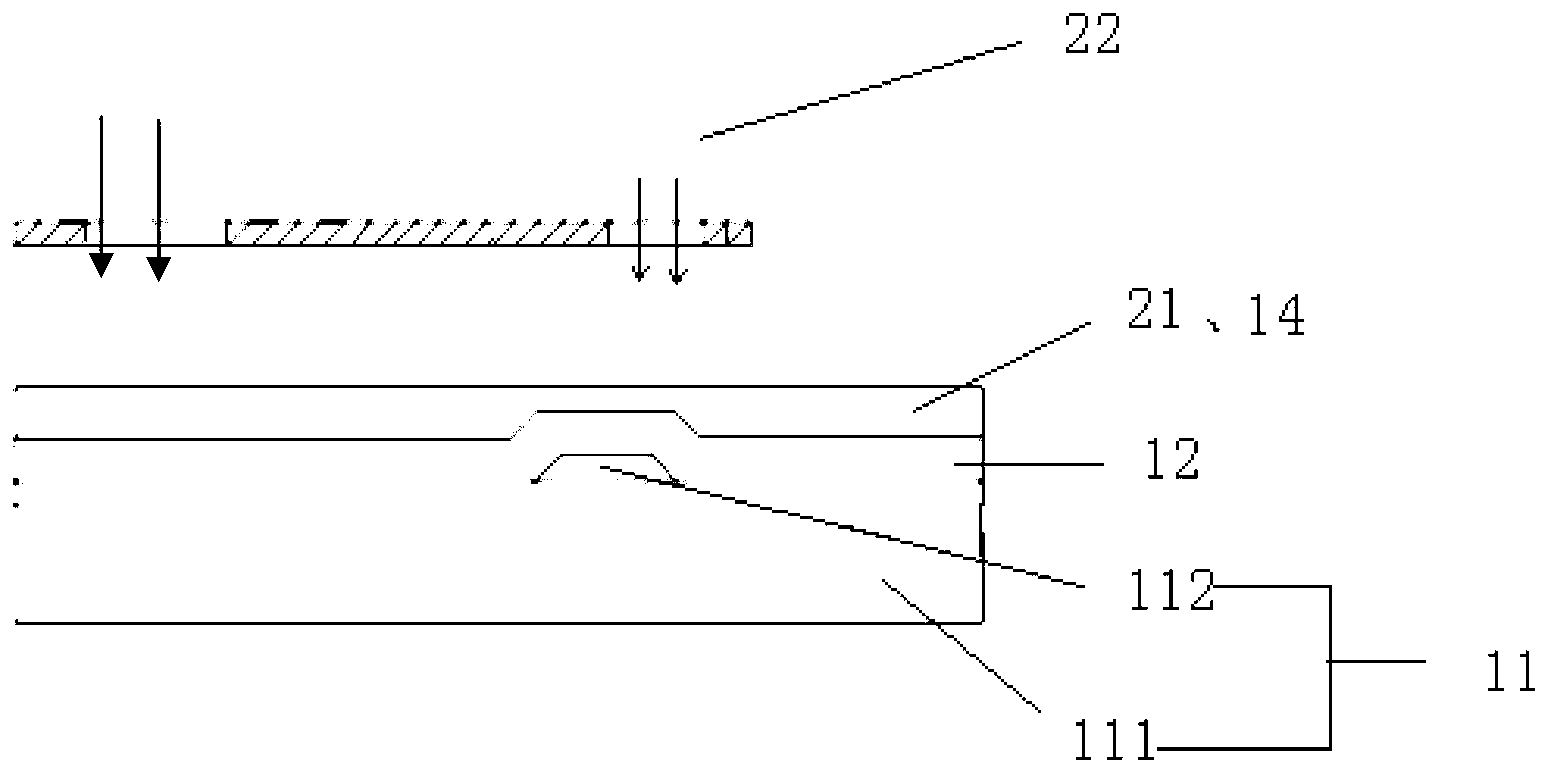

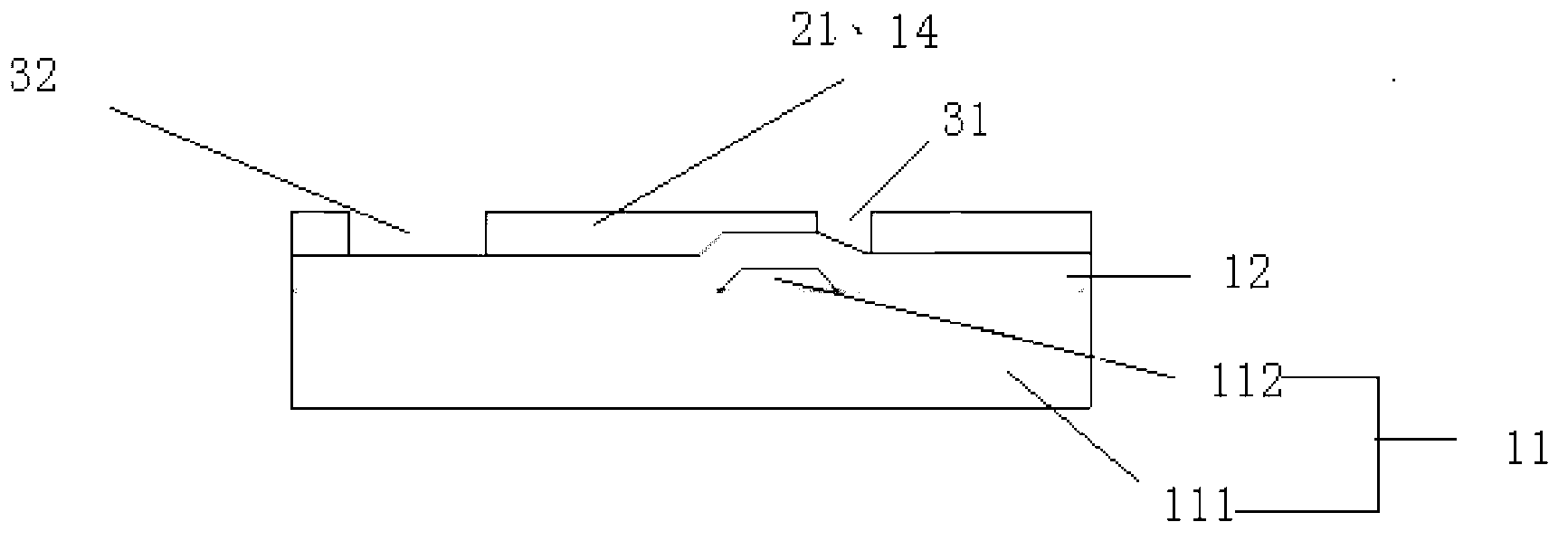

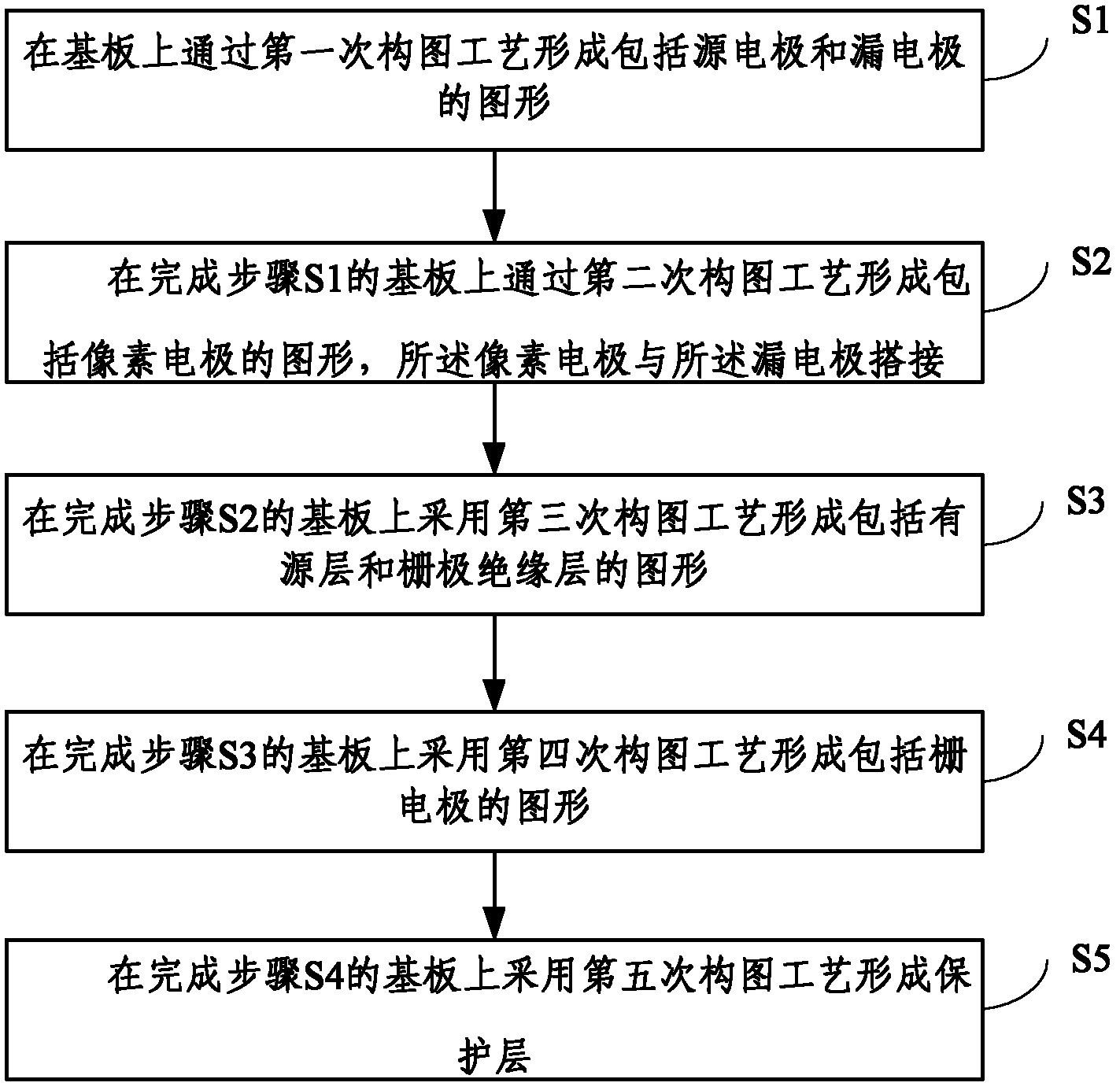

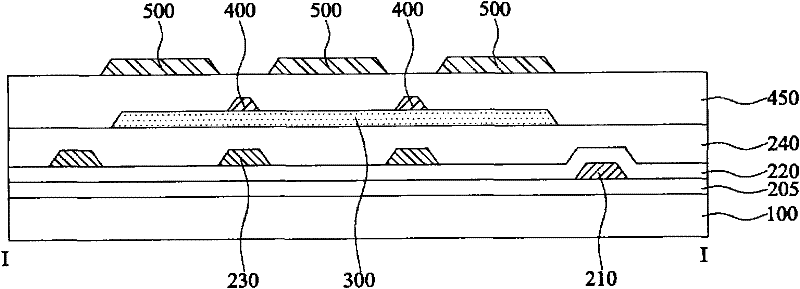

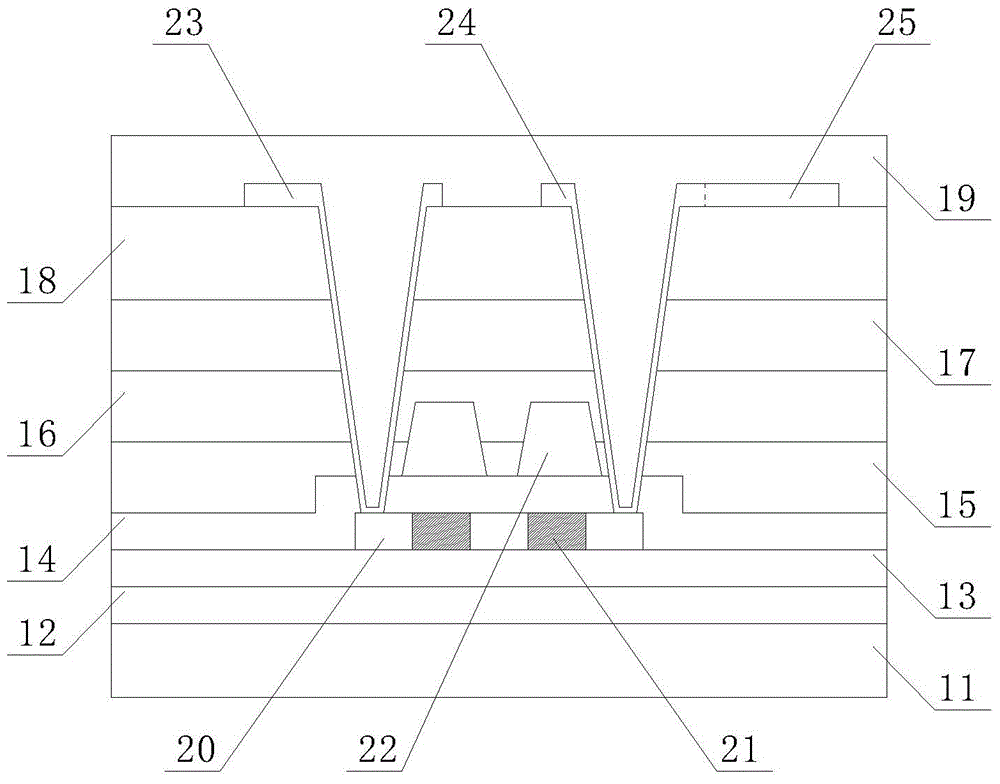

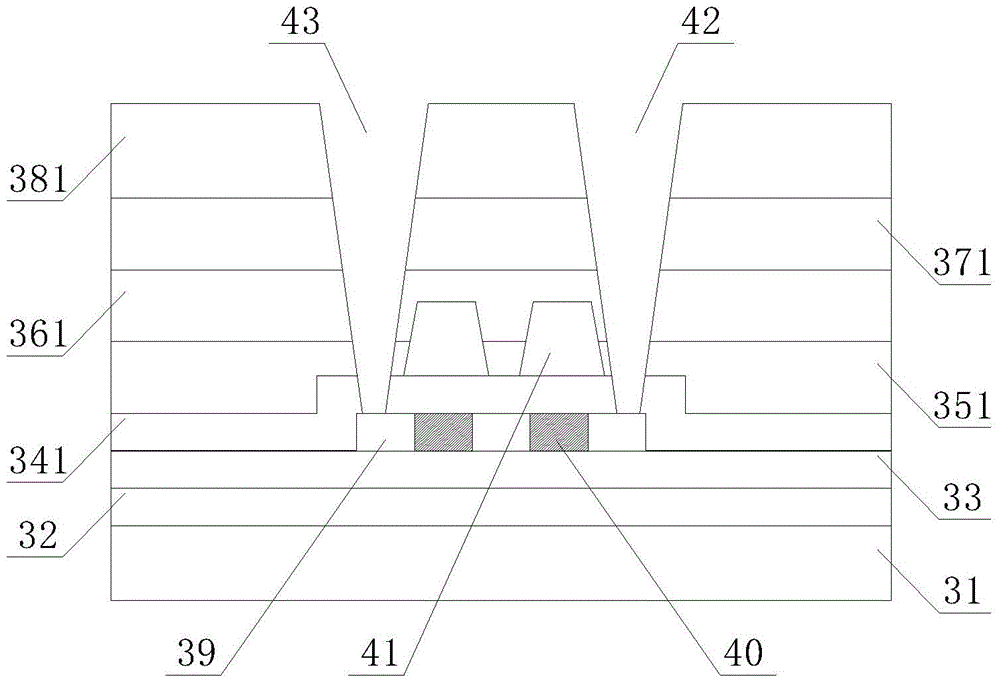

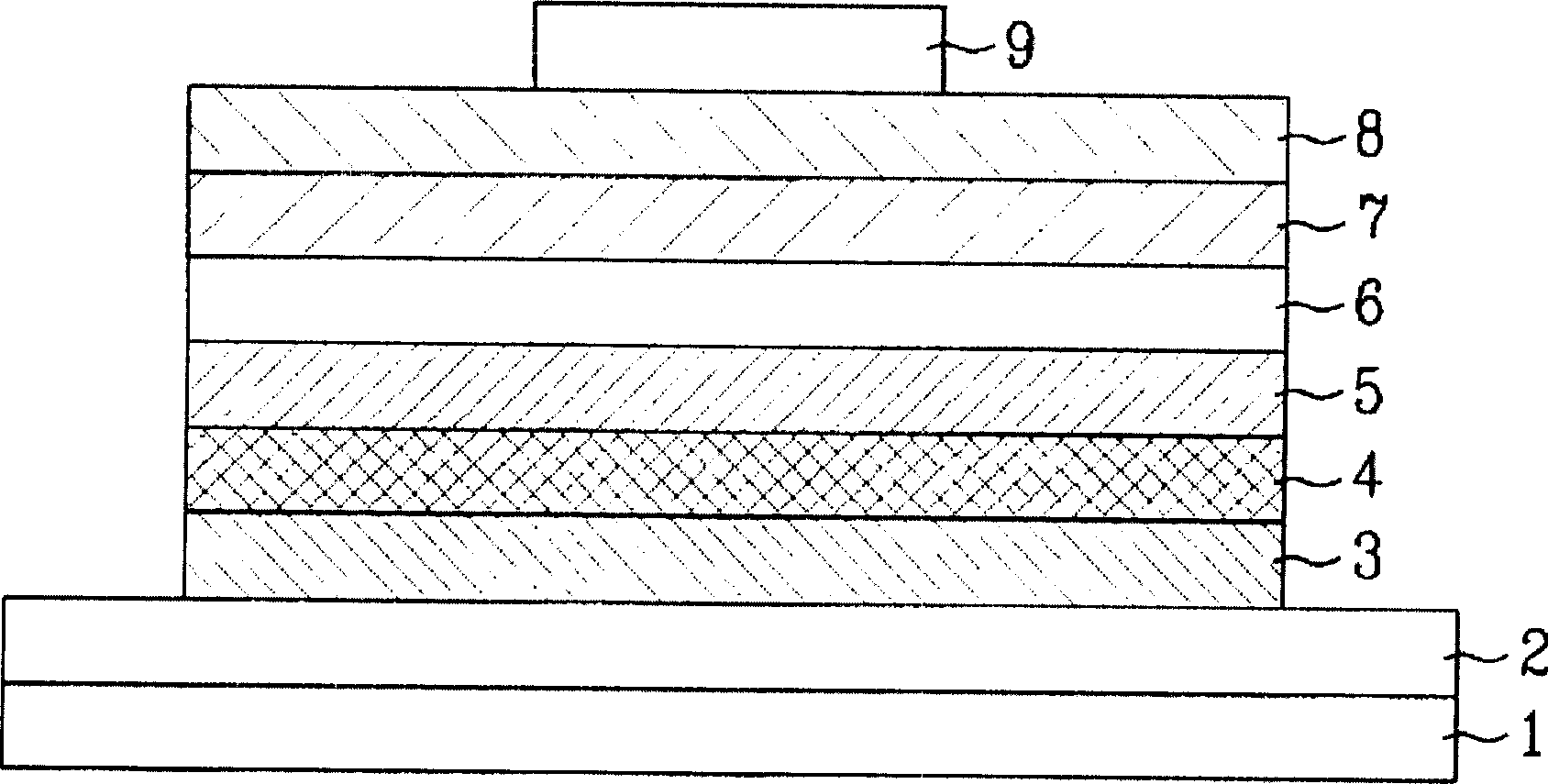

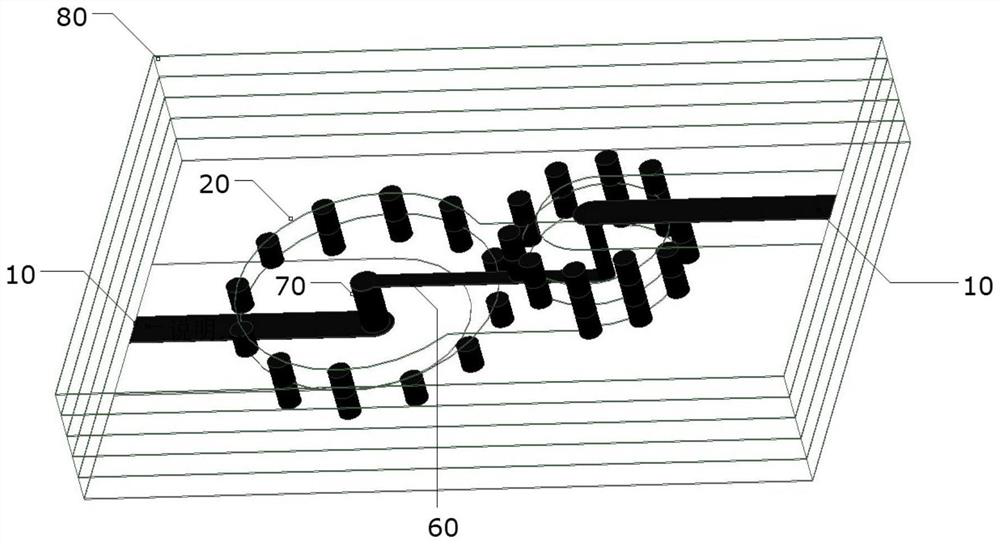

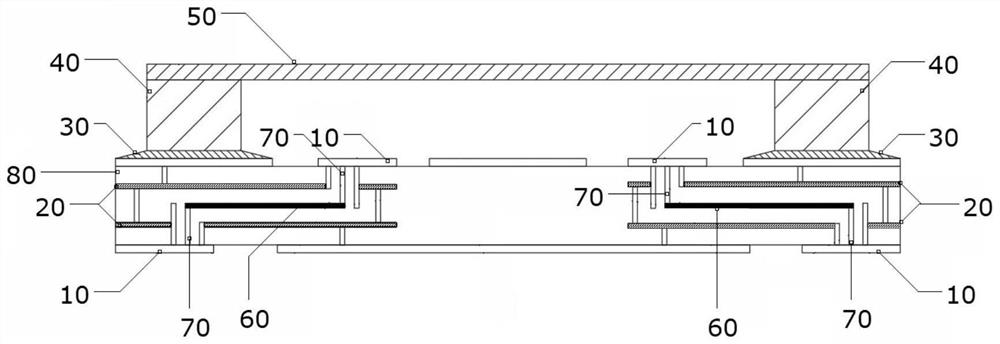

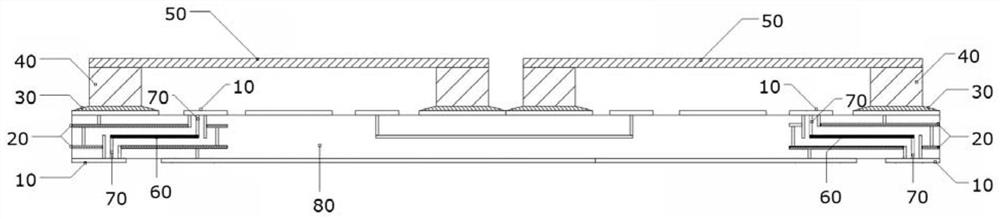

Dual-gate thin film transistor and preparation method therefor, array substrate and display apparatus

ActiveCN106684155ASimple structureSimple manufacturing process stepsTransistorSemiconductor/solid-state device manufacturingPhysicsLithography process

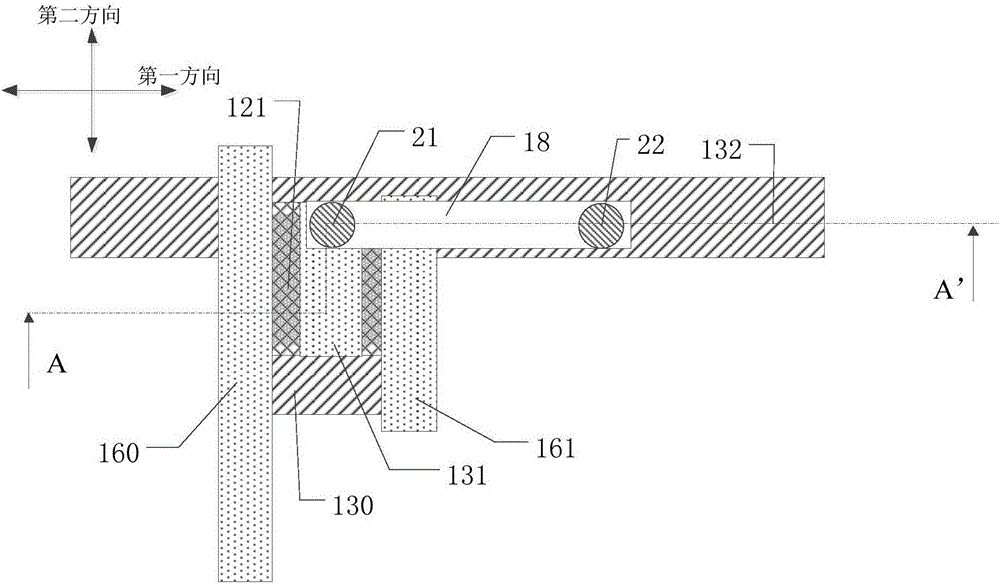

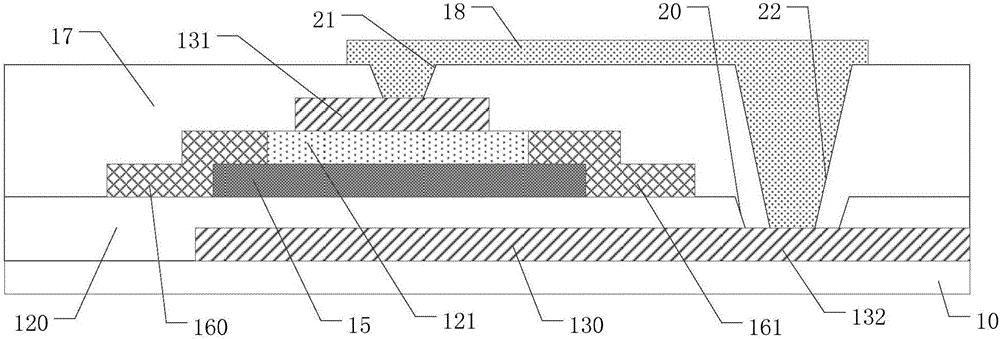

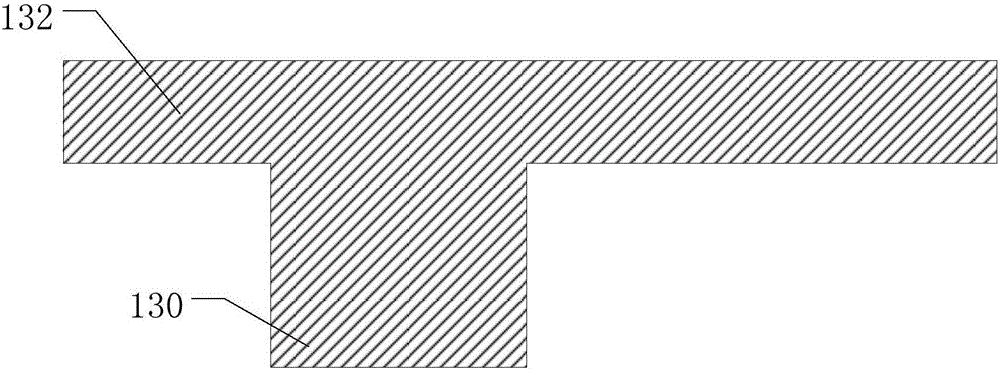

The invention discloses a dual-gate thin film transistor and a preparation method therefor, an array substrate and a display apparatus. The dual-gate thin film transistor comprises a substrate and a first gate, a first gate insulating layer, an active layer, a second gate insulating layer, a first electrode, a second electrode, a second gate and a connecting electrode which are arranged on the substrate in sequence, wherein the second gate and the first electrode and the second electrode are formed on the same layer; the first gate insulating layer comprises a first via hole for exposing a part of the first gate; and the connecting electrode is electrically connected with the second gate and electrically connected with the first gate through the first via hole. According to the dual-gate thin film transistor, the first electrode, the second electrode and the second gate are formed through a photolithography technique at the same time; by virtue of electric connection between the transparent connecting electrode and the first gate and the second gate, the dual-gate structure is realized, so that the number of film layers and masks is reduced, the production time is shortened, the production cost is lowered, capacity is effectively improved, the stability of the thin film transistor is improved, and response speed of the thin film transistor is optimized.

Owner:BOE TECH GRP CO LTD +1

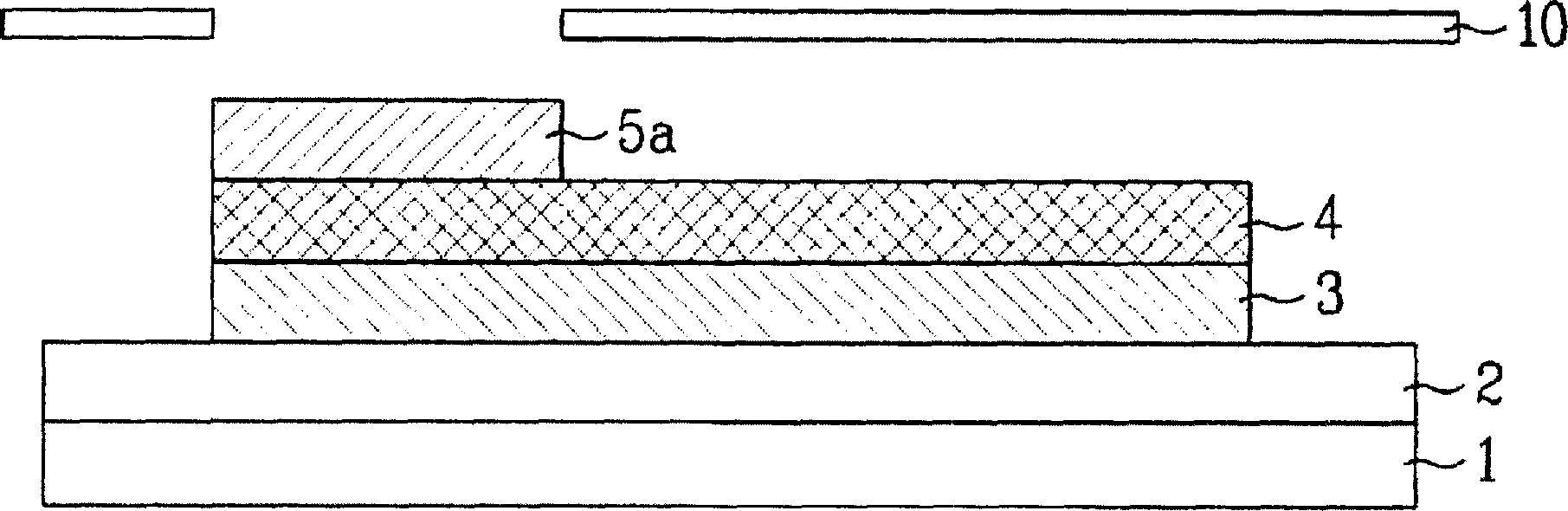

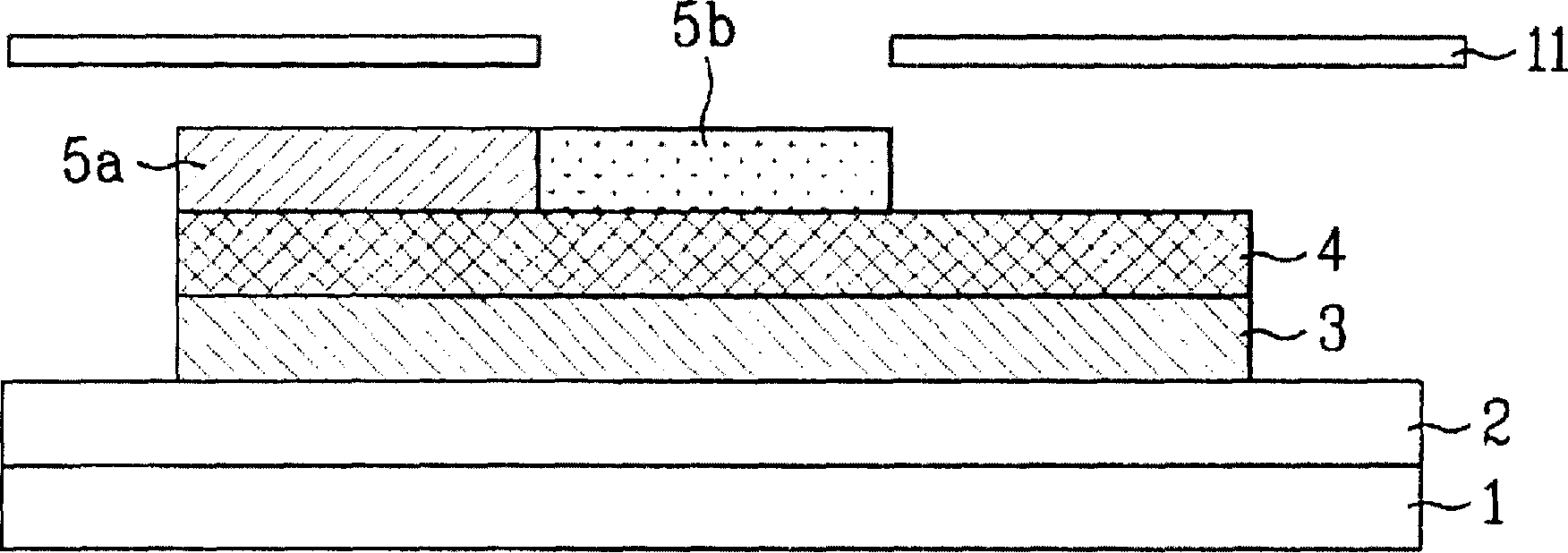

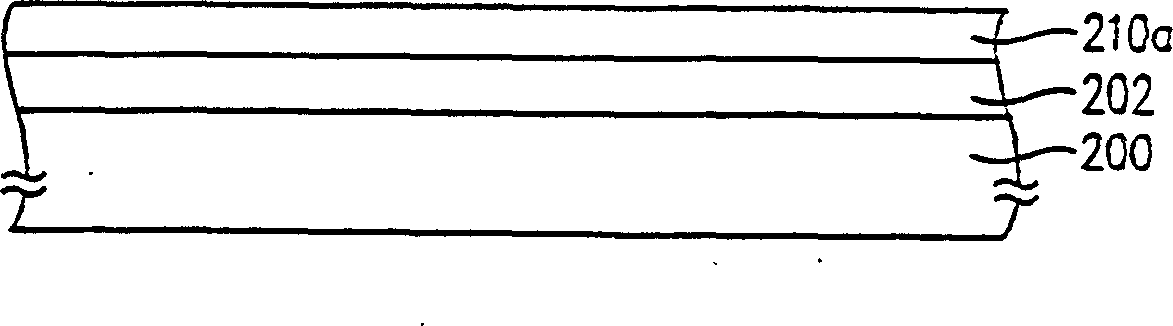

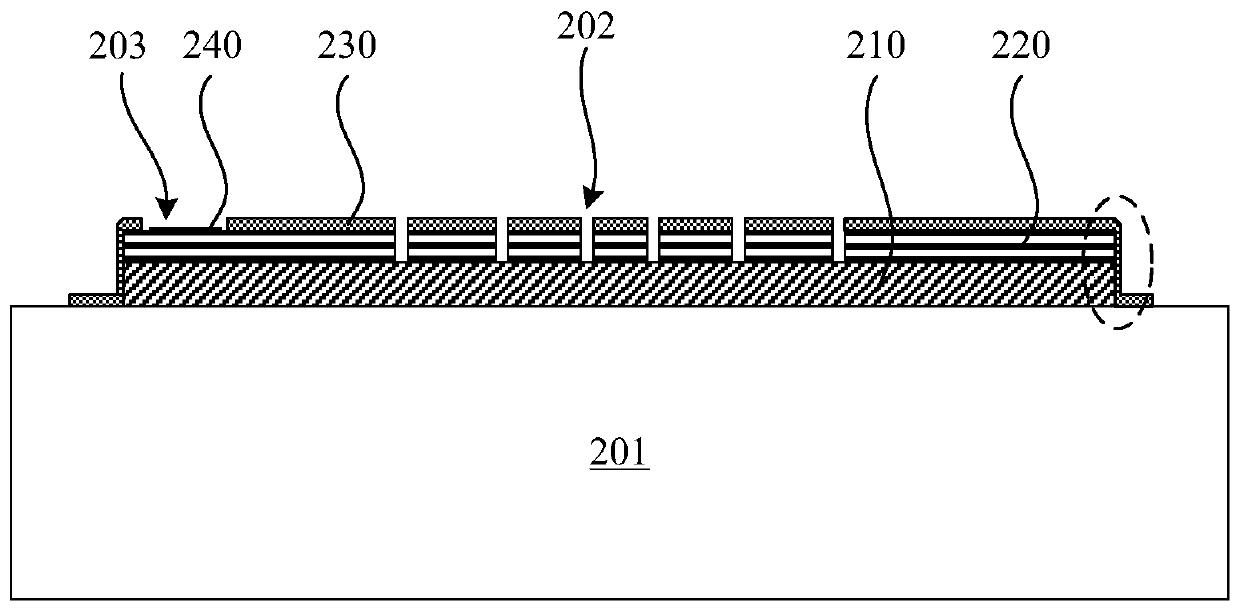

Method for separating base plate and semiconductor layer

InactiveCN101866880ASimple manufacturing process stepsLow technical costSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingSemiconductor components

The invention relates to a method for separating a base plate and a semiconductor layer. The method is characterized in that a pattern silicon dioxide layer is formed between a temporary base plate and the semiconductor layer; then, the temporary base plate is separated from the pattern silicon dioxide layer by a secondary wet type etching way. The temporary base plate is removed by using the secondary wet type etching way, thereby avoiding damaging the structure of the semiconductor layer by using a the laser lift off (LLO) method. In addition, by utilizing the secondary wet type etching method, the manufacture process step is simpler, and the technical cost is decreased. On a vertical semiconductor element, the light emitting benefit of the element is increased due to the irregular surface formed by a manufacture process. In addition, by utilizing the wet type etching in the manufacture process, the batch amplification can be increased, and the cost of the manufacture process is decreased.

Owner:ZHANJING TECH SHENZHEN +1

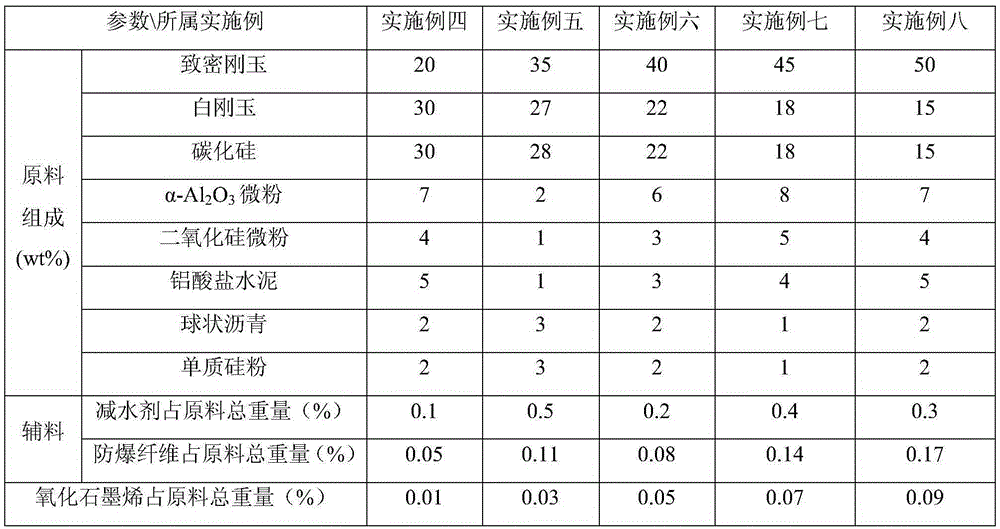

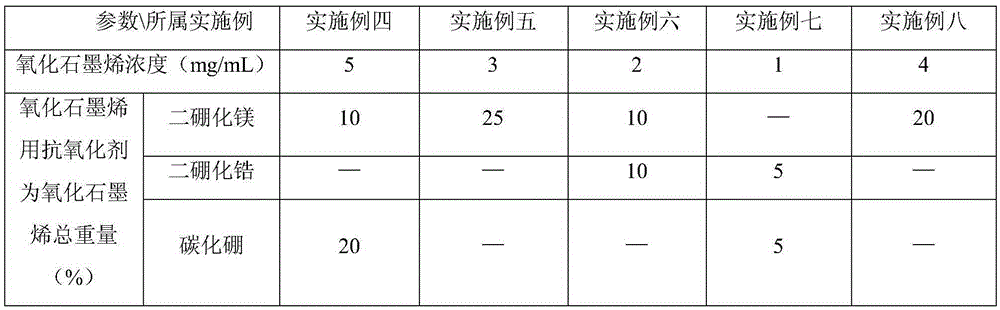

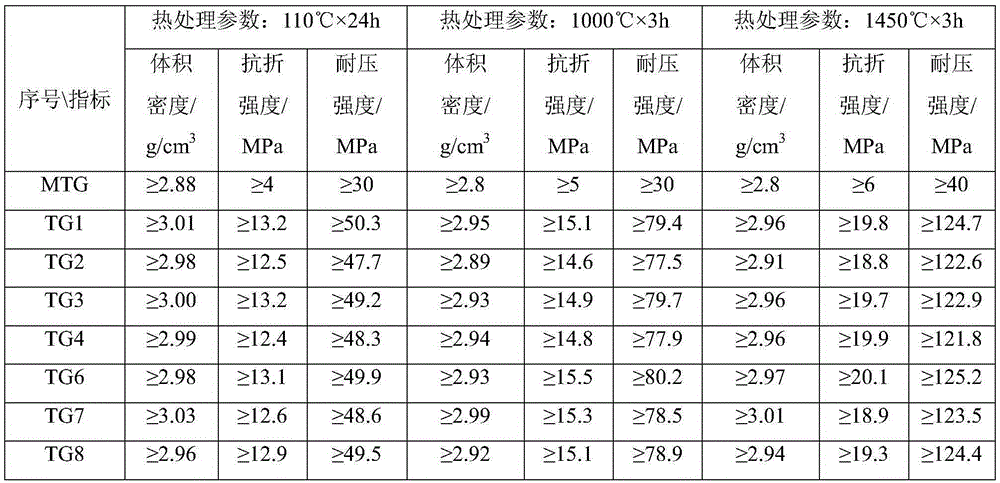

Preparation method of iron runner castable containing graphene oxide

ActiveCN105294134ASimple manufacturing process stepsProcess parameters are easy to controlFiberPorosity

The invention provides a preparation method of an iron runner castable containing graphene oxide, comprising the following steps: step 1: premixing materials, and mixing raw materials and auxiliary materials evenly, wherein the raw materials contain dense corundum, white corundum, carborundum, alpha-Al2O3 micropowder, silicon dioxide micropowder, aluminate cement, ball pitch and monatomic silicon powder, and the auxiliary materials comprise a water reducer and explosion-proof fiber; step 2, adding graphene oxide solution and an antioxidant for the graphene oxide. By applying the technical scheme, the preparation method has the following effects: (1) preparation steps are simplified, and are suitable for industrial production; (2) the added graphene oxide can reduce the usage amount of common carbonaceous materials such as the ball pitch, and the production of poisonous and carcinogenic gas can be reduced when the iron runner castable is used in a high temperature environment; (3) the content of carbon in the castable can be effectively increased by the addition of the graphene oxide, the additive quantity of water and the porosity of the iron runner castable can be reduced, and the structural strength, thermal shock resistance and corrosion resistance of the iron runner castable are enhanced.

Owner:CENT SOUTH UNIV

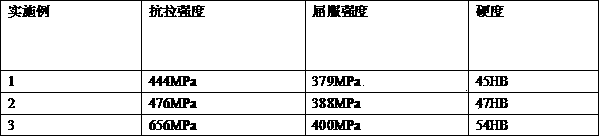

Boron nitride reinforced multi-element heat-resistant magnesium alloy and preparation method thereof

The invention provides a boron nitride reinforced multi-element heat-resistant magnesium alloy which comprises the following components in percentage by weight: 0.5-0.7% of Gd, 3.35-3.6% of Al, 1.7-1.95% of Zn, 4.0-5.0% of Si, 0.9-1.0% of Ca, 1.0-1.1% of Sr, 0.8-1.0% of Nd, 0.1-0.3% of Zr, 1-2% of Sn, 0.15-0.20% of Be, 0.7-1.0% of Mn, 0.1-0.15% of Sb, 0.5-0.8% of Cu, 1-15% of boron nitride nanotube particles and the balance of Mg, wherein the size of the boron nitride nanotube particles is below 100 microns. The invention also provides a preparation method of the alloy. The alloy has good mechanical property.

Owner:宏辉磁电科技(安徽)有限公司

Manufacturing method of COA array substrate, array substrate and display device

InactiveCN103258793ALow costSimple manufacturing process stepsSemiconductor/solid-state device detailsSolid-state devicesLiquid-crystal displayDisplay device

The invention provides a manufacturing method of a COA array substrate, the array substrate and a display device, and belongs to the technical field of liquid crystal display. The manufacturing method of the COA array substrate, the array substrate and the display device can resolve the problems that an existing array substrate is complex in manufacturing method and high in cost. The manufacturing method of the COA array substrate includes the following steps: a photo-etching glue layer is coated on a protective layer on a TFT base, the photo-etching glue layer can be used as a planarization layer at the same time, and the TFT base comprises a base body and a TFT; through a photolithography technique, a colorful-film containing hole is formed in the photo-etching glue layer; a colorful filter layer is manufactured in the colorful-film containing hole. The array substrate comprises the photo-etching glue layer which is located on the protective layer, the photo-etching glue layer can be used as the planarization layer at the same time, the colorful-film containing hole is formed in the photo-etching glue layer, and the colorful filter layer is formed in the colorful-film containing hole. The display device comprises the array substrate.

Owner:BOE TECH GRP CO LTD

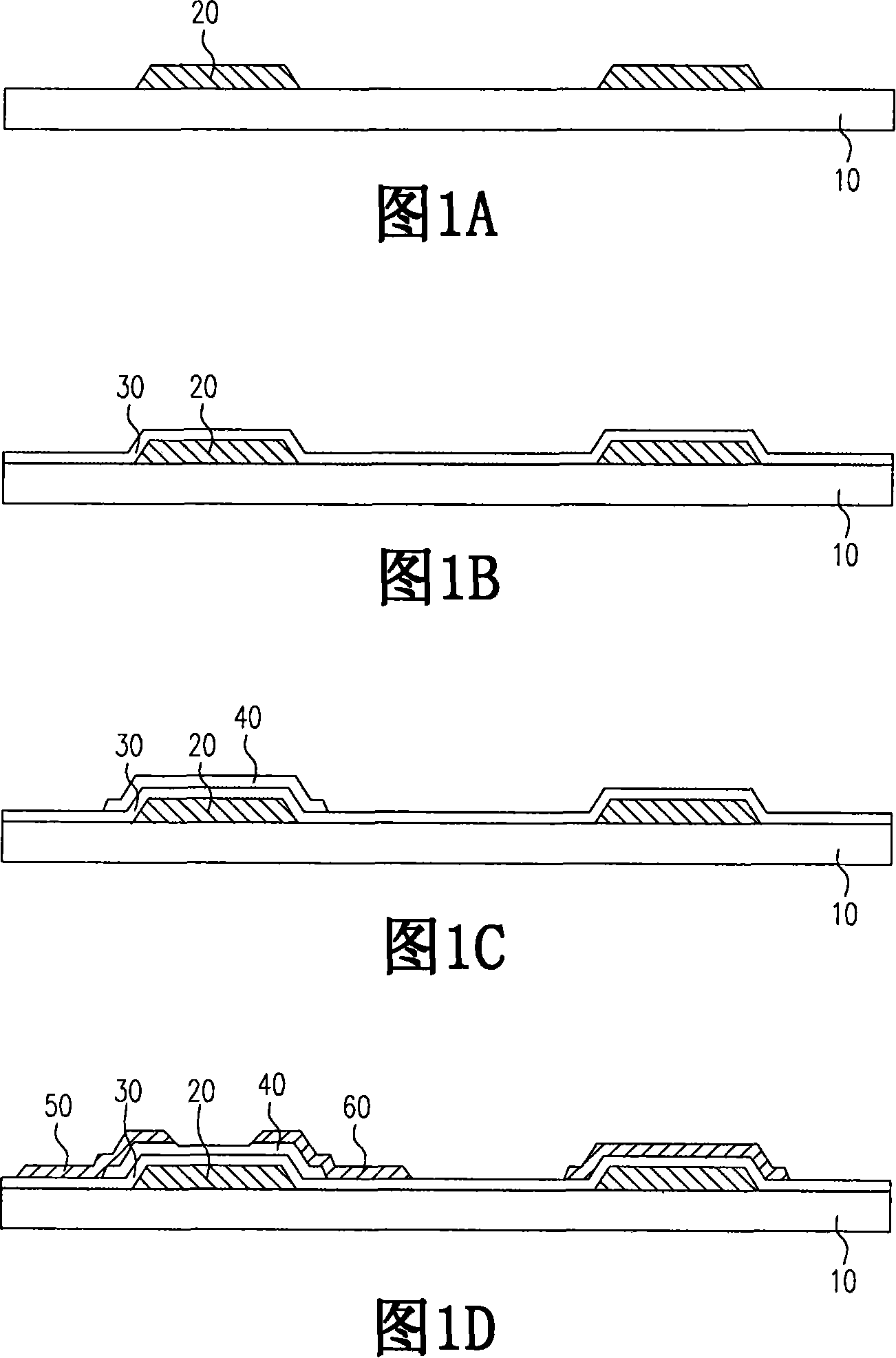

Making method for CMOS thin film transistor

ActiveCN101150092AMask pass count reductionSimple manufacturing process stepsSemiconductor/solid-state device manufacturingCMOSOxide

This invention relates to a manufacturing method for semiconductor elements including: carrying out first micro-image etching to form a first photoetching substratum with at least two diferent thicknesses to define a semiconductor layer of PMOS and NMOS elements by the photoetching substratum and then defining source / drain of the PMOS element by the ashed first substratum and forming a second photoetching substratum by second micro-image etching to define the grid of the PMOS and NMOS elements from the second substratum then to define a LDD of the NMOS element from the ashed second substratum.

Owner:AU OPTRONICS CORP

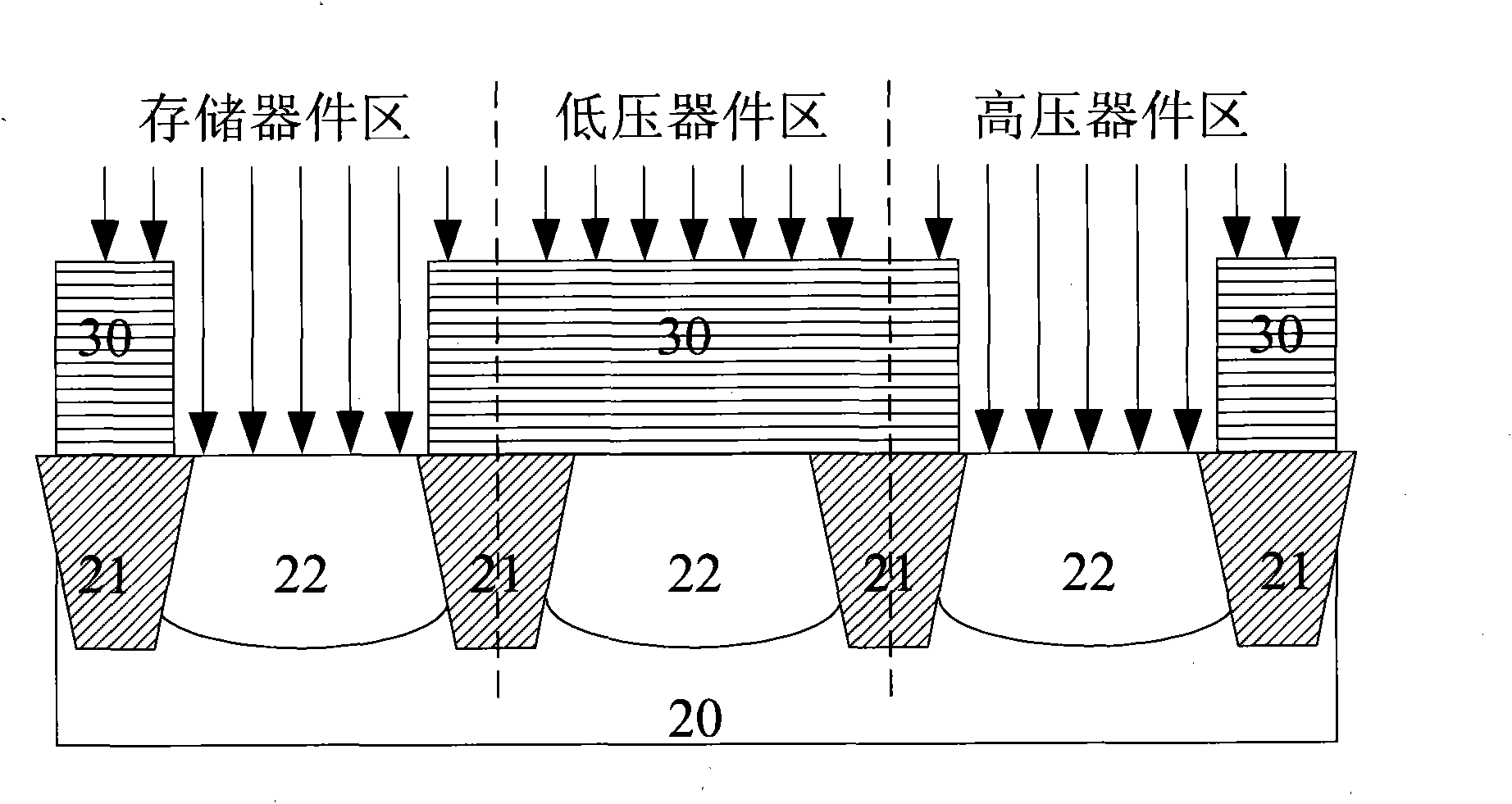

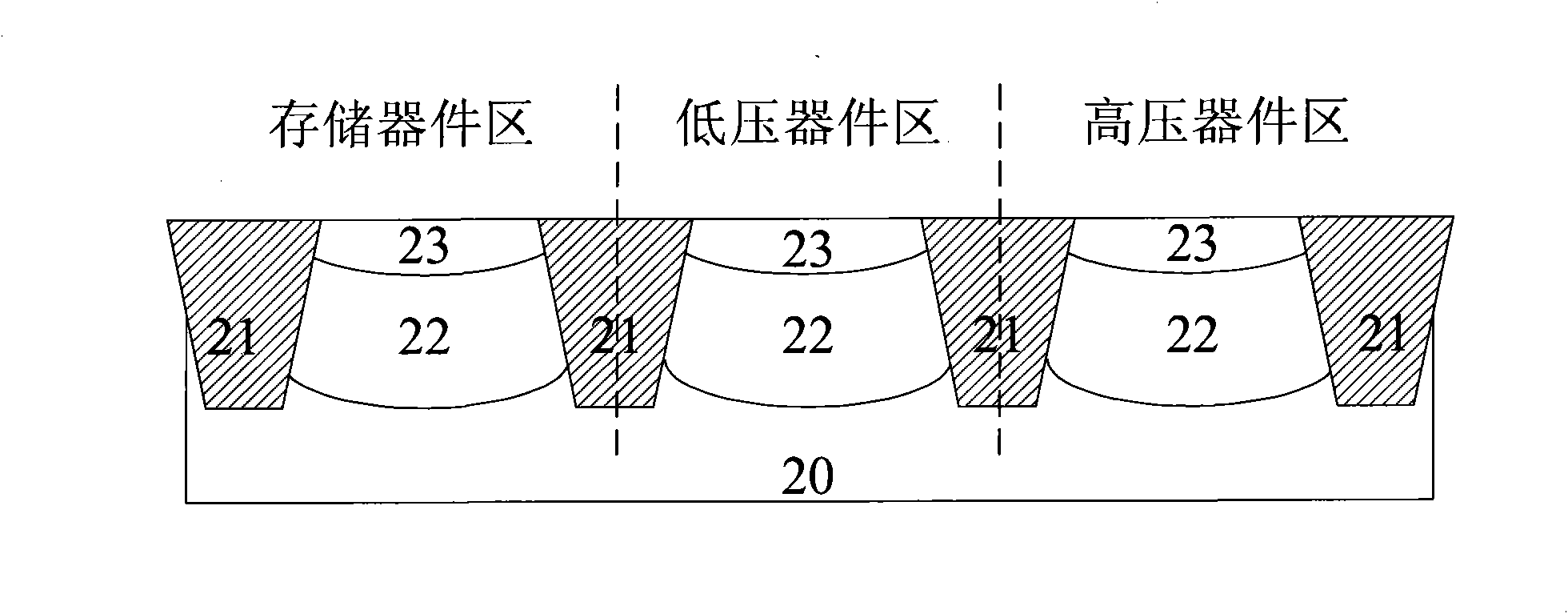

Method for manufacturing gate oxide layer of EEPROM and gate oxide layer manufactured thereby

ActiveCN102104025ASimple manufacturing process stepsShorten production timeSolid-state devicesSemiconductor/solid-state device manufacturingEEPROMAND gate

The present invention discloses a method for manufacturing a gate oxide layer of an EEPROM (Electrically-Erasable Programmable Read-Only Memory). The method comprises the following steps: step 1, spin-coating a layer of photoresist on the surface of a silicon chip, wherein after exposing and developing, the photoresist only covers a low voltage device area and an area on which a tunneling oxide layer will form, wherein a storage device area is fully exposed except the area containing the tunneling oxide and a high pressure device area is also fully exposed; carrying out an ion implantation onthe surface of the silicon chip with the photoresist as a barrier layer of the iron implantation; and forming an ion implantation area in the silicon chip; step 2, removing the photoresist; step 3, making a high voltage oxide layer and a tunneling oxide layer grow on the surface of the silicon chip; and making a high pressure oxide layer grow in the ion implantation area formed in the step 1, wherein the thickness of the tunneling oxide layer is less than the thickness of the high voltage oxide layer. The present invention also discloses a gate oxide layer of an EEPROM manufactured by the above method. The method for manufacturing a gate oxide layer of an EEPROM has the advantages of simple processing steps, short manufacture time and low manufacture cost. Moreover, electrical characteristics of a low voltage device area can be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

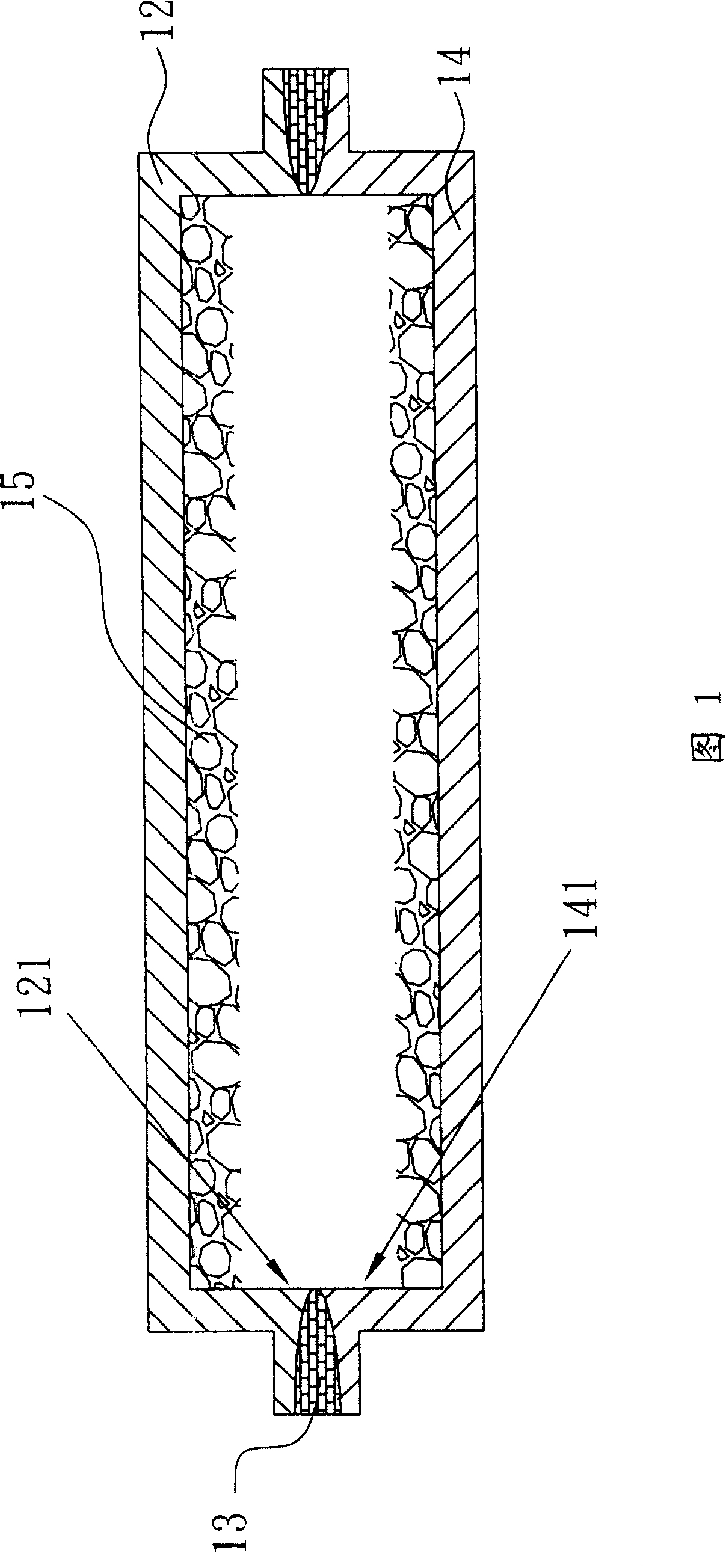

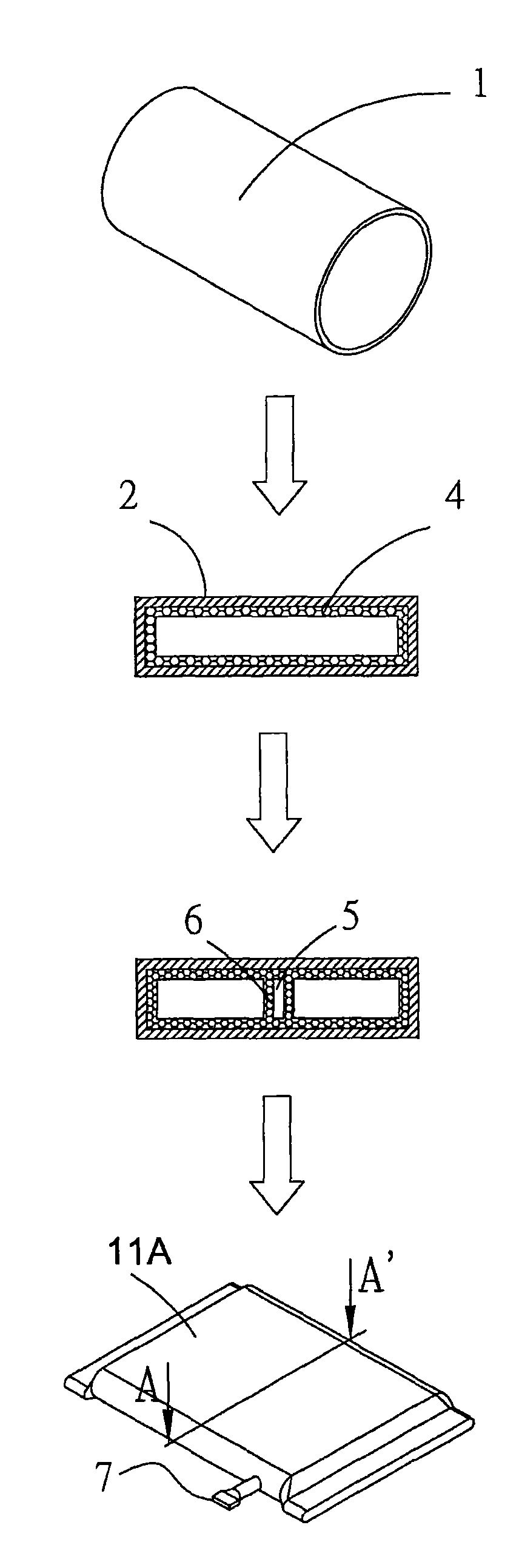

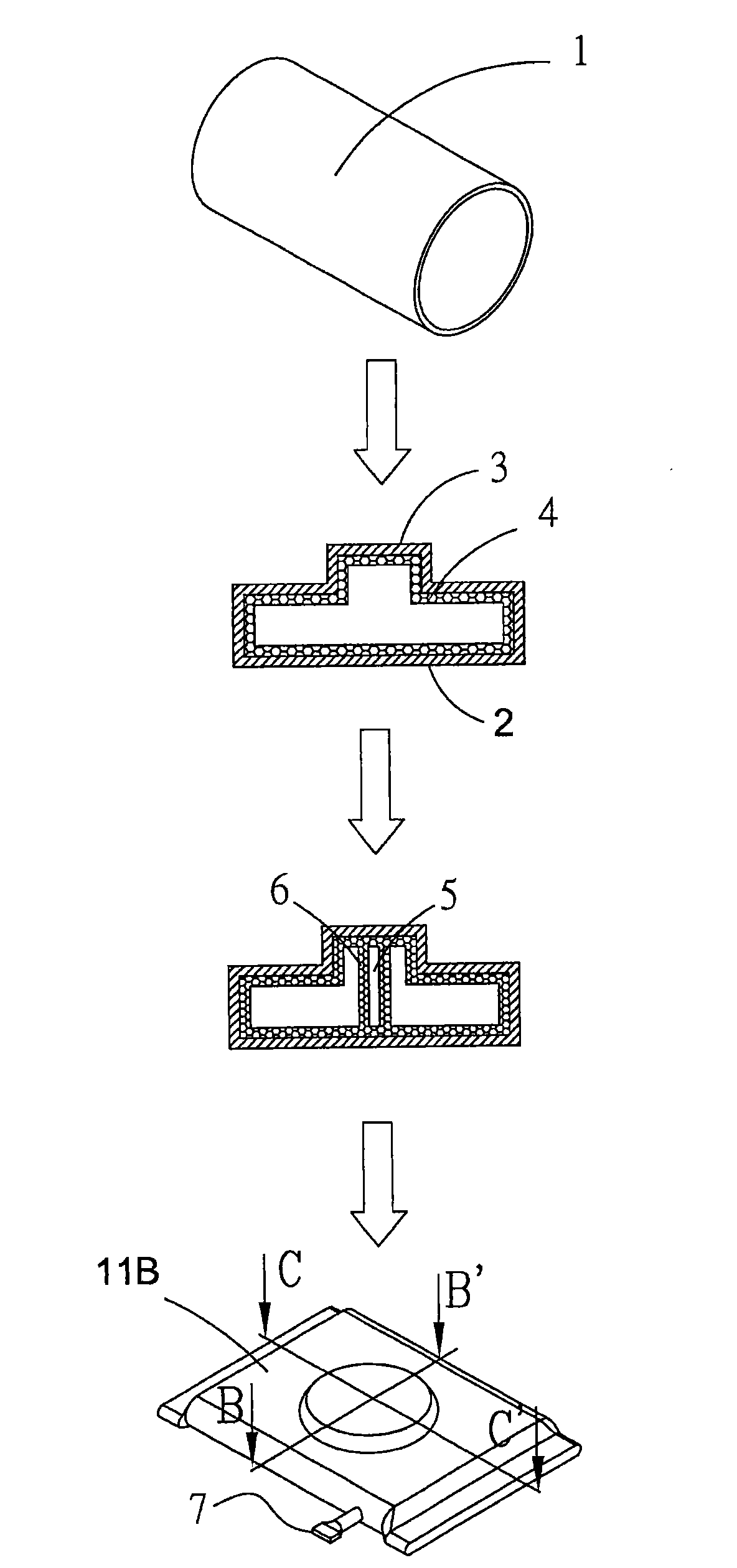

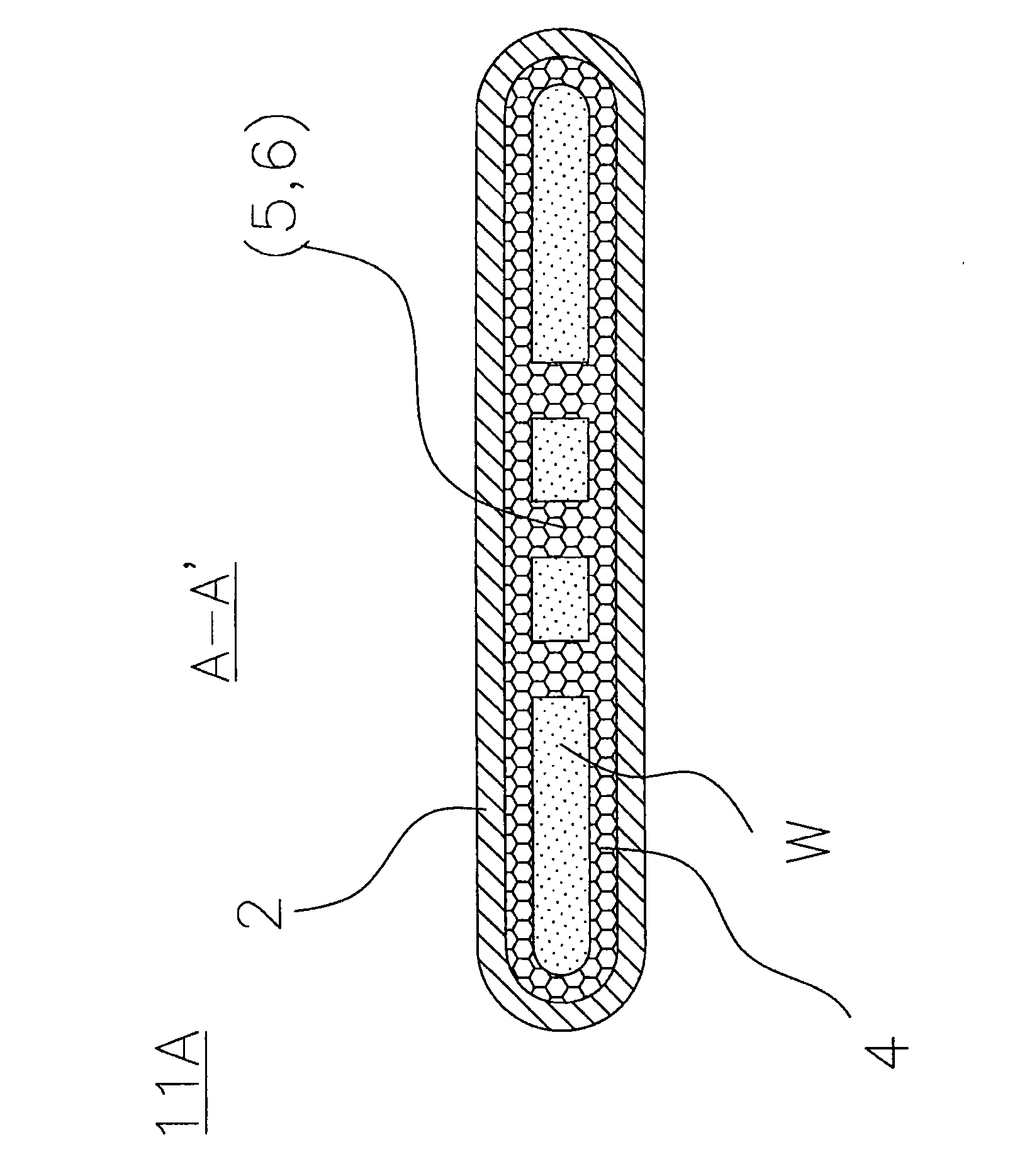

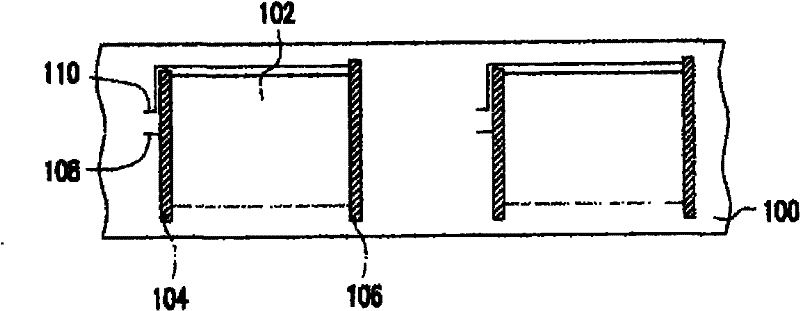

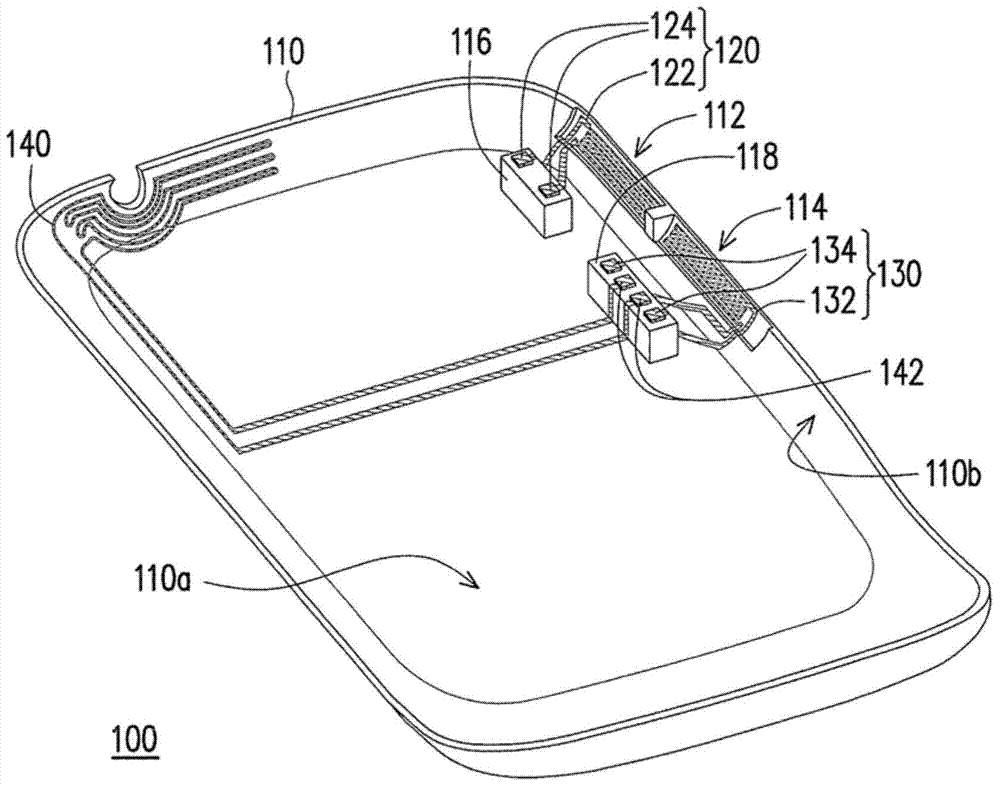

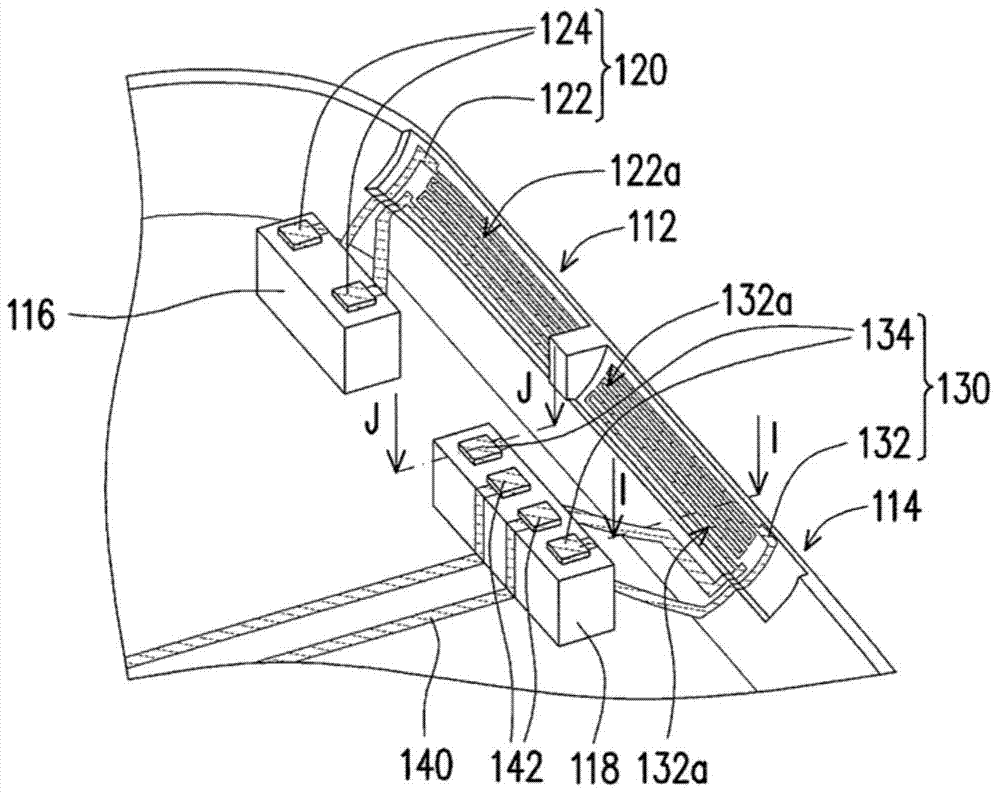

Heat pipe and its manufacturing method

InactiveCN101162134AReduce the numberSimple manufacturing process stepsIndirect heat exchangersWorking fluidEngineering

The invention discloses a plate-type heat tube and a method for manufacturing the same. The plate-type heat tube comprises a flat hollow ring body which is provided with two opening ends, and the surface of the inner wall of the hollow ring body forms a capillary structure, wherein, a bending part is also provided next to the two opening ends and causes the hollow ring body to form airtight space, and working fluid is filled in the airtight space.

Owner:DELTA ELECTRONICS INC

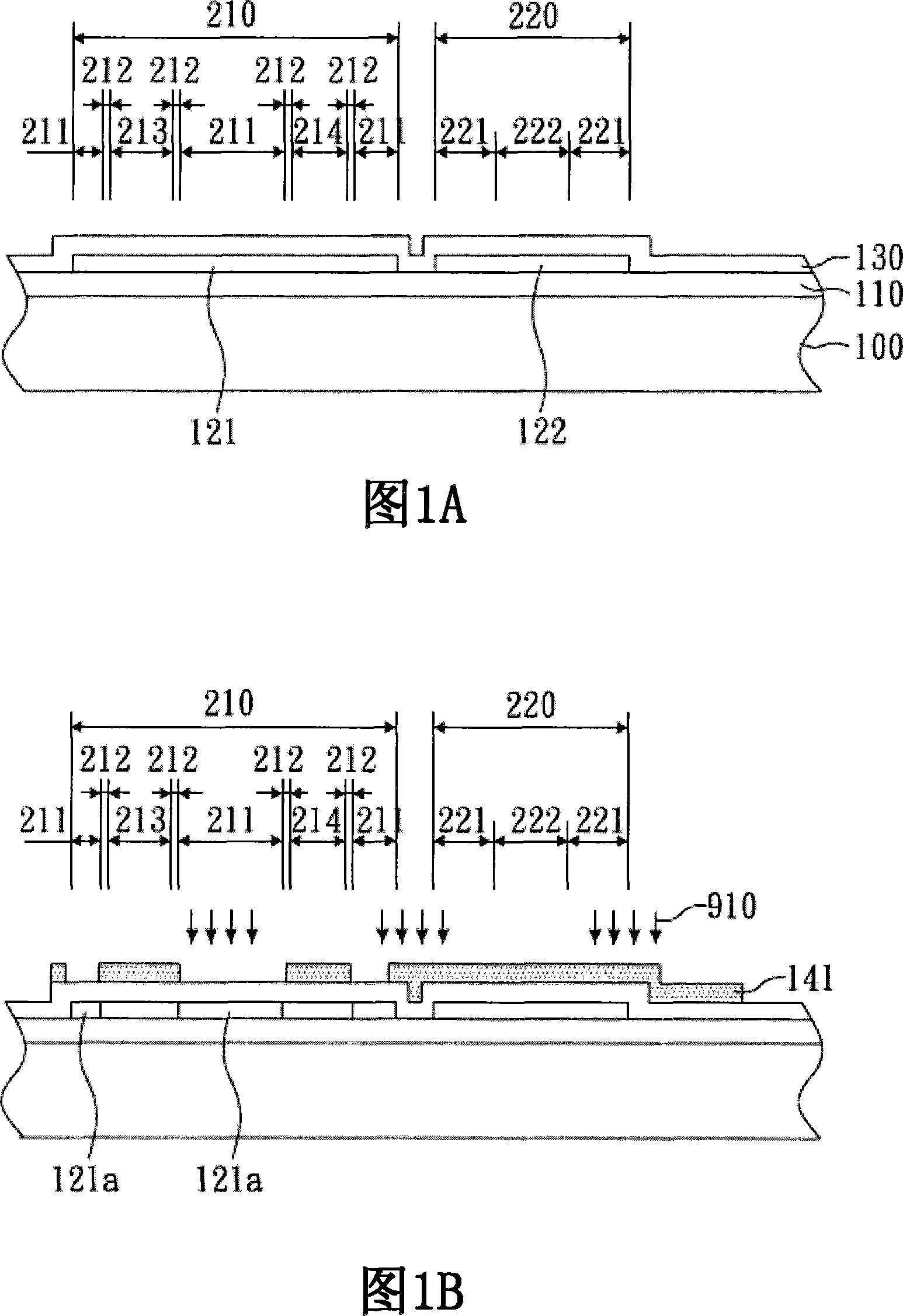

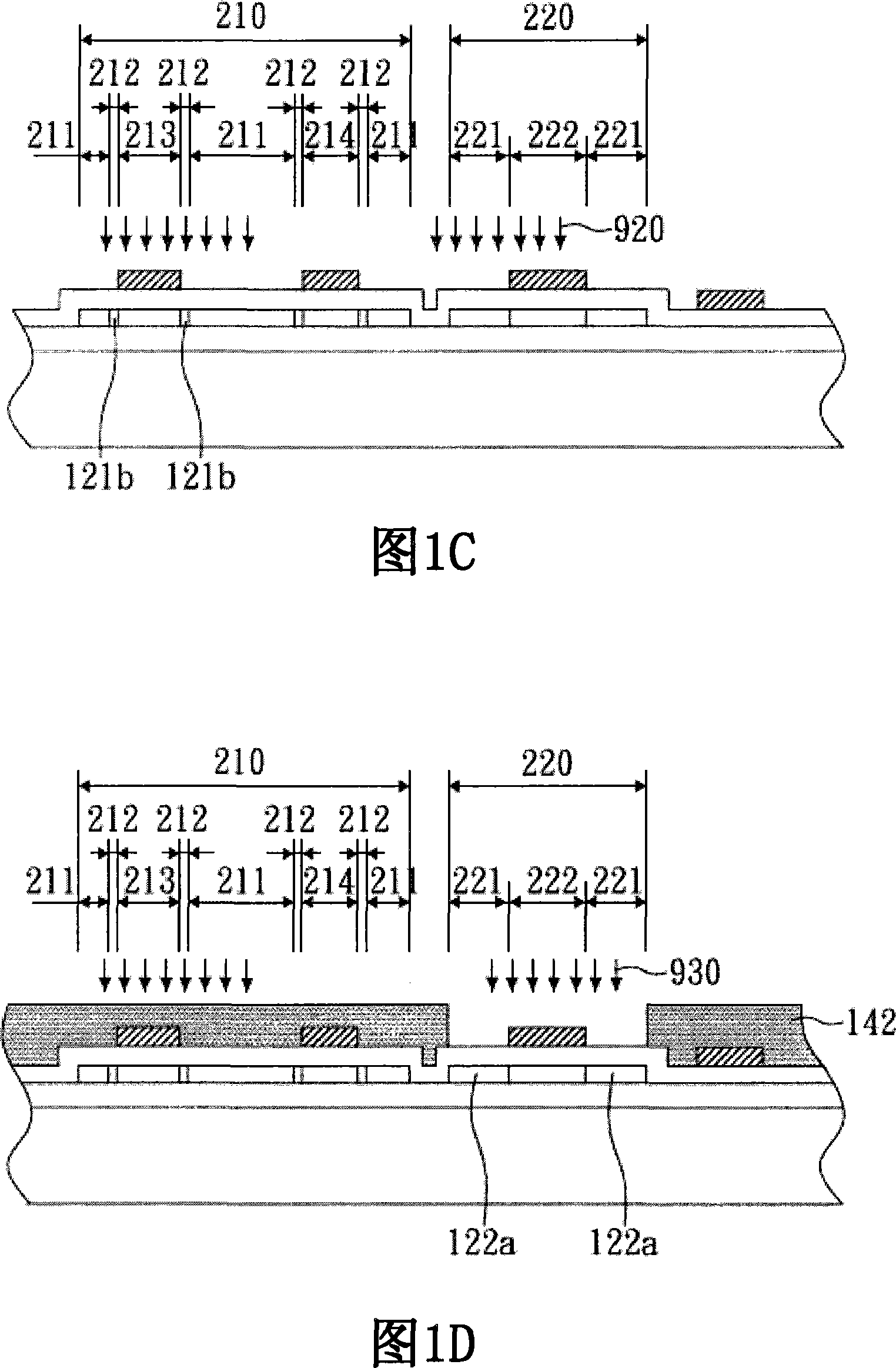

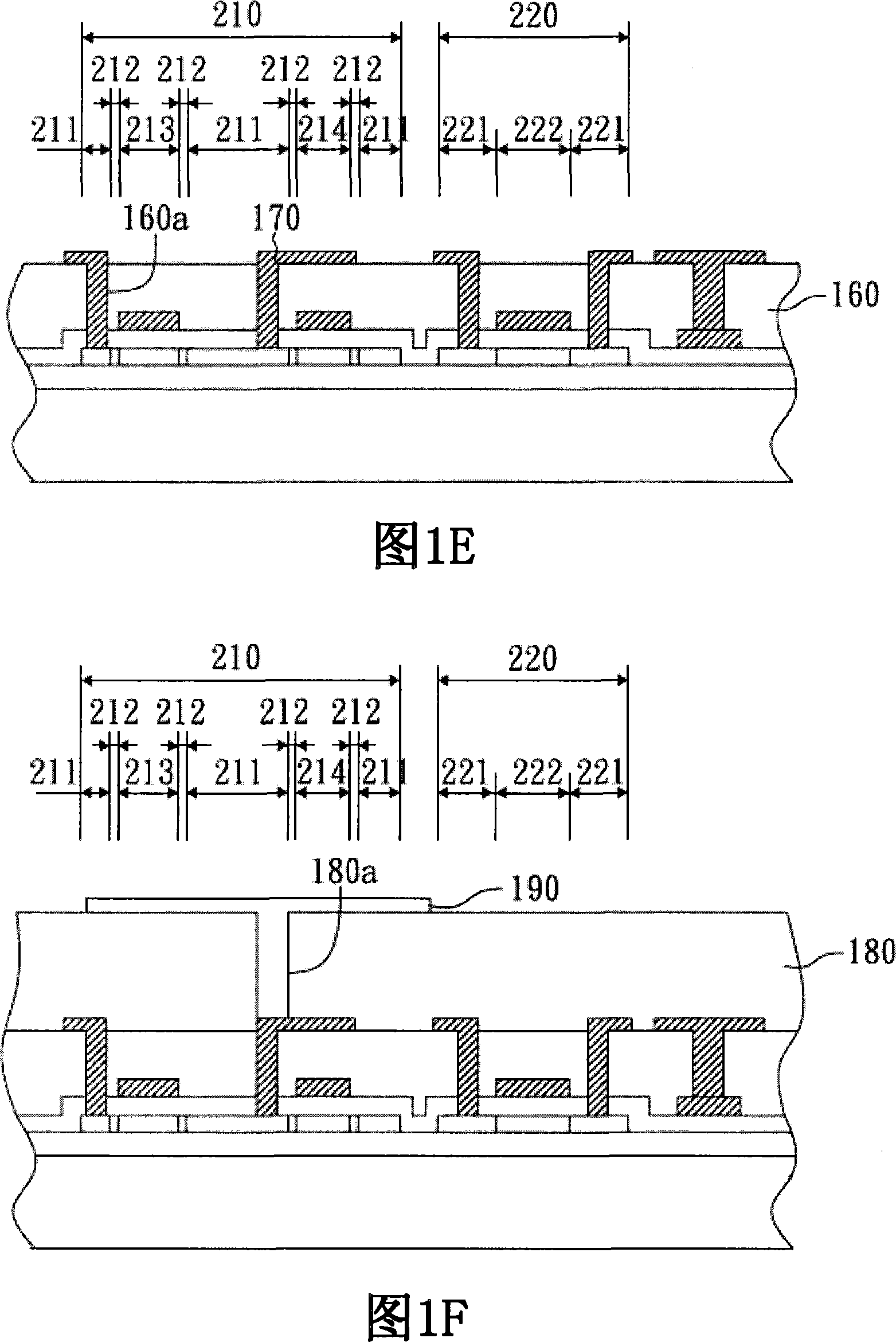

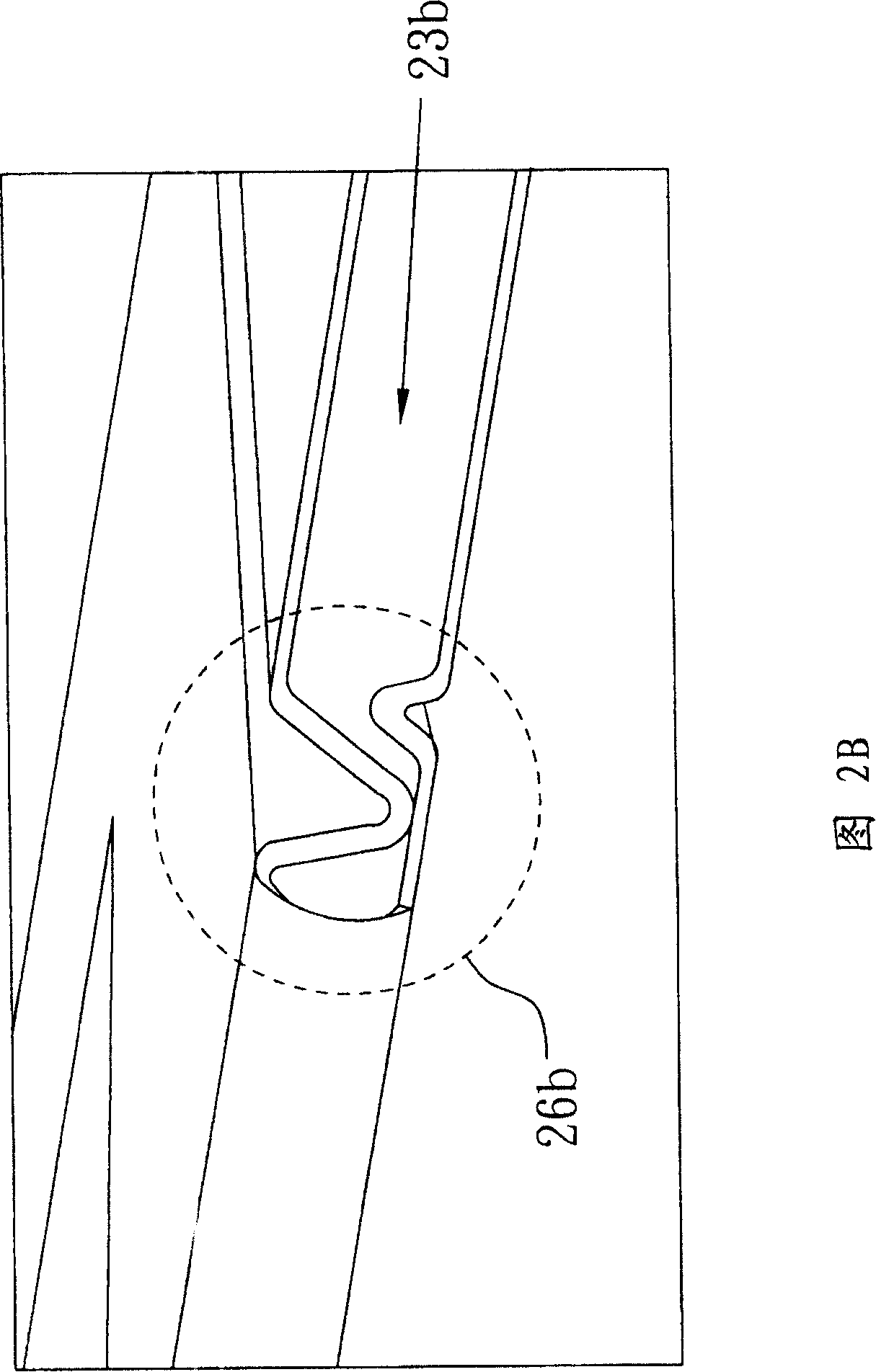

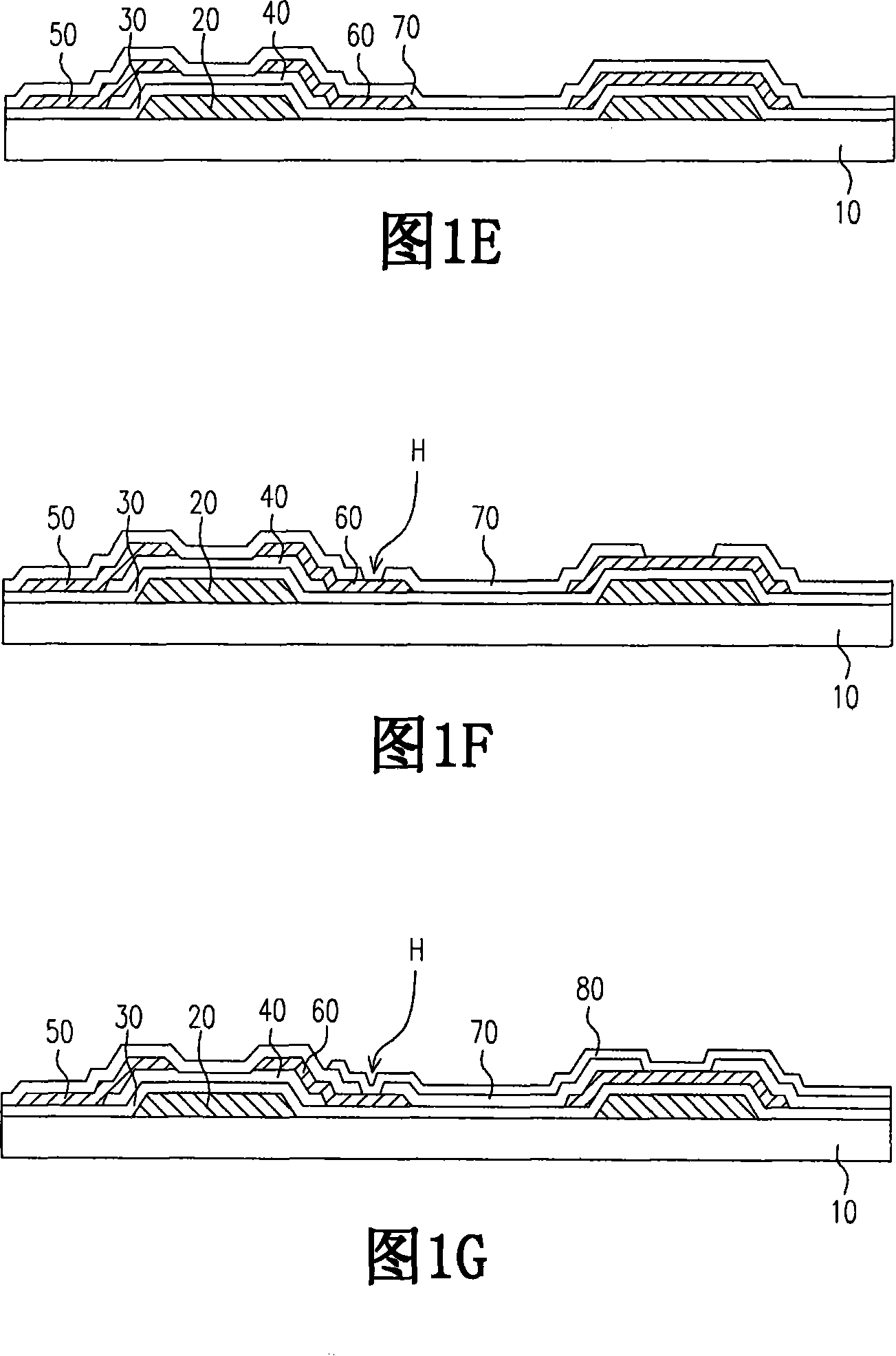

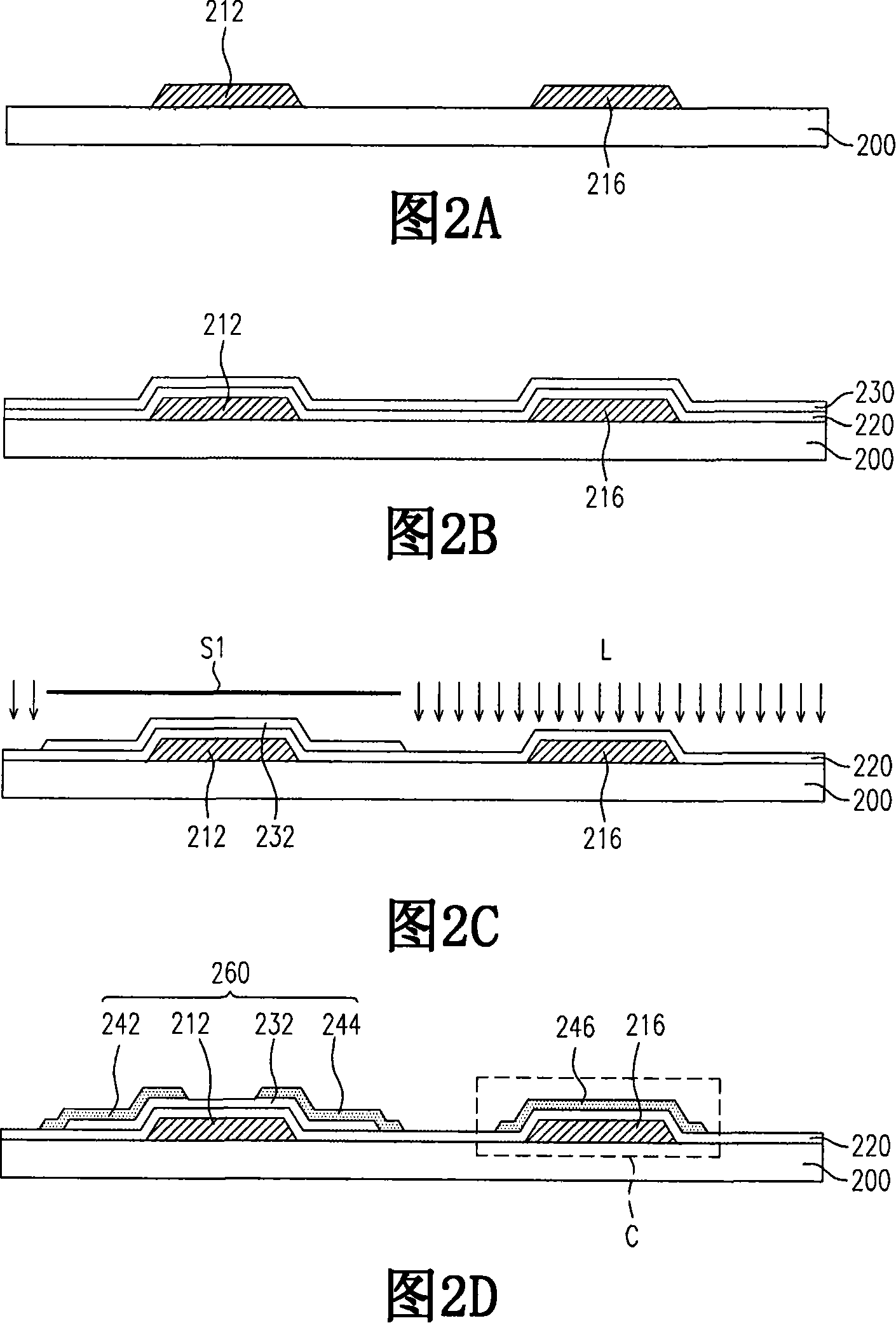

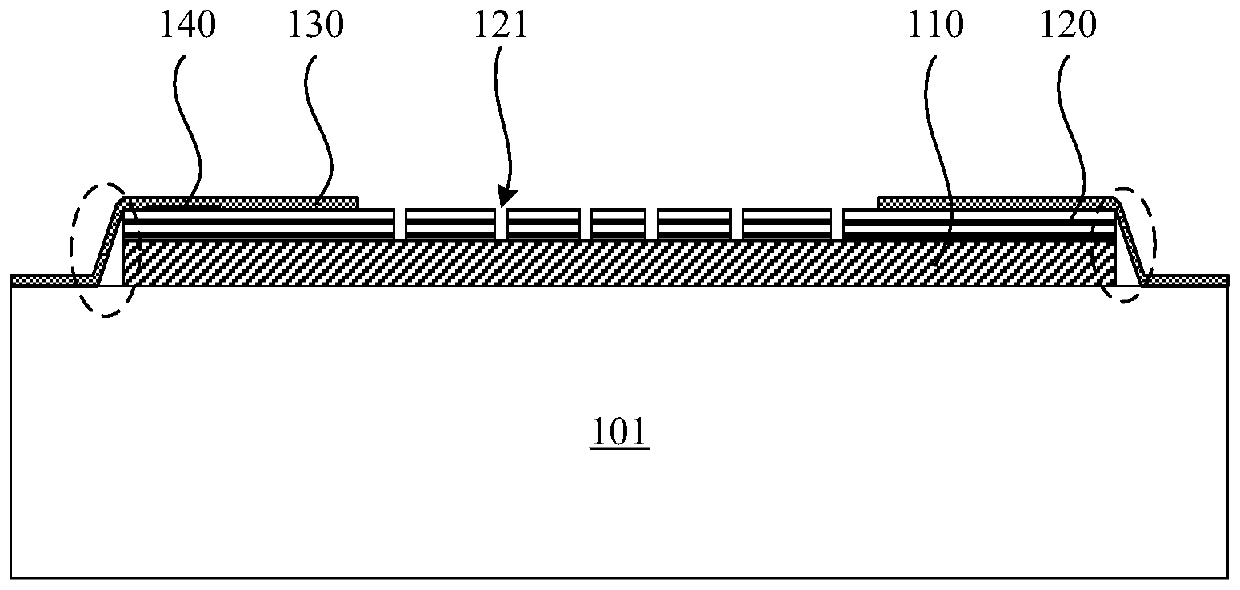

Method for fabricating pixel structure

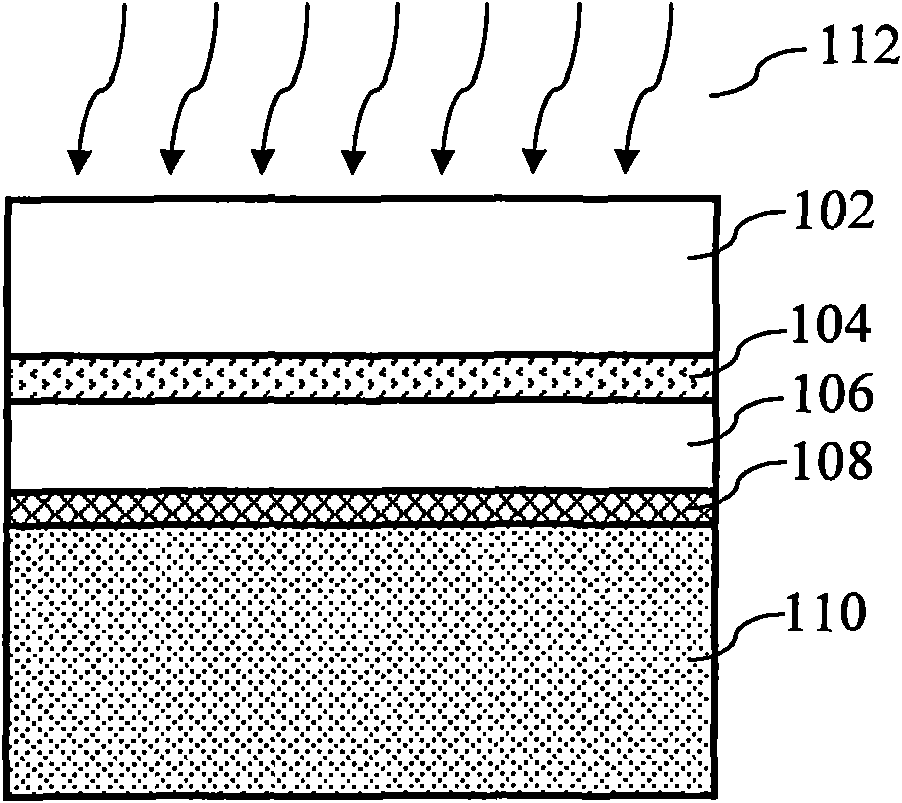

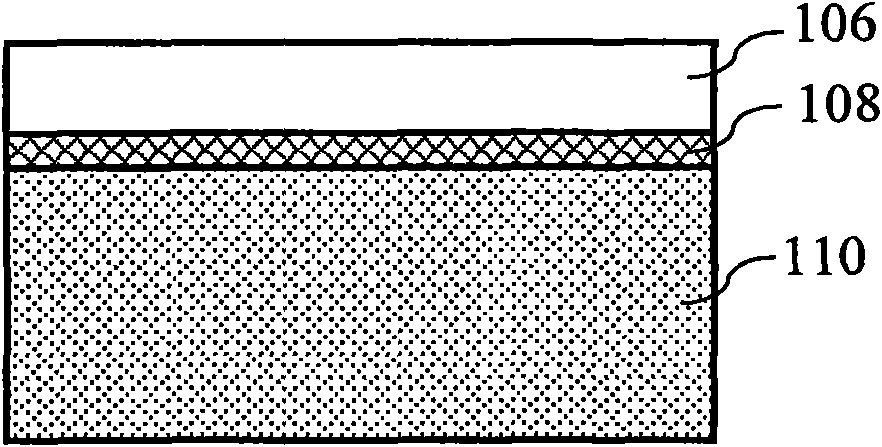

InactiveCN101118881AReduce manufacturing costLow costSemiconductor/solid-state device manufacturingNon-linear opticsEngineeringIrradiation

The present invention relates to a manufacturing method for the image element structure, which comprises the steps below. Firstly, the present invention provides a basal plate and form a grid on the basal plate, and then the a door dielectric layer is formed on the basal plate to cover the grid, and then a semiconductor layer is formed on the door dielectric layer, and the present invention provides a first shield cover extending partial semiconductor layer above the semiconductor layer, and the present invention uses the laser irradiation to remove partial semiconductor layer to form a channel layer, and then the present invention form a source electrode and a drain electrode on the channel layer on two sides of the grid, then the present invention form a design protecting layer to cover the channel and is uncovered from the drain electrode. Finally the present invention form a conductive layer to cover the design protecting layer and the uncovered drain electrode, and the present invention makes the conductive layer designed through the design protecting layer to form the image element electrode.

Owner:AU OPTRONICS CORP

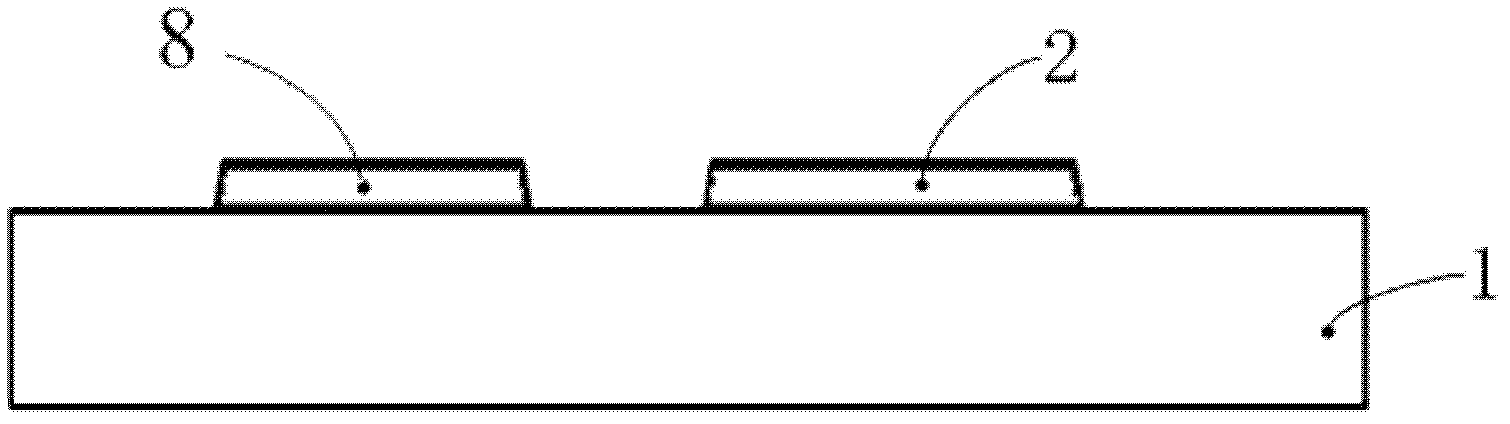

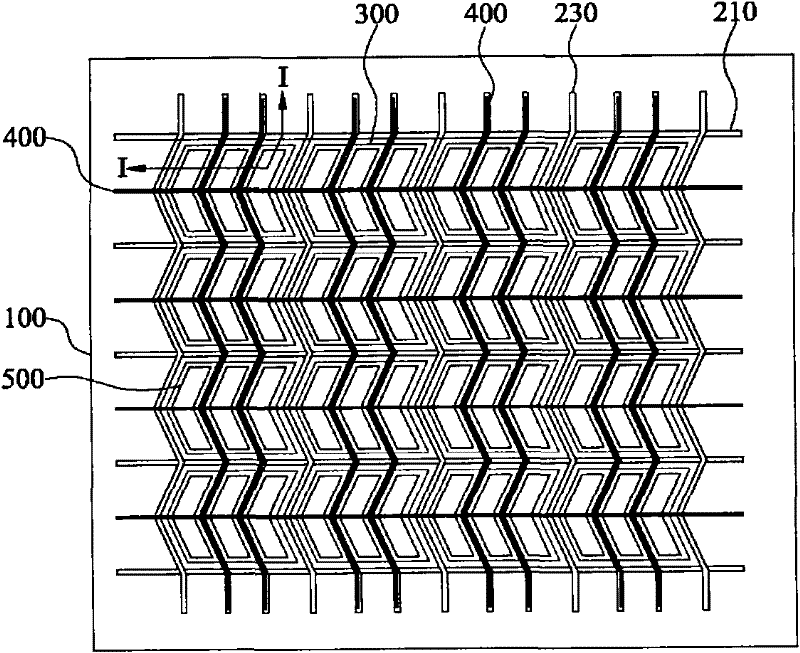

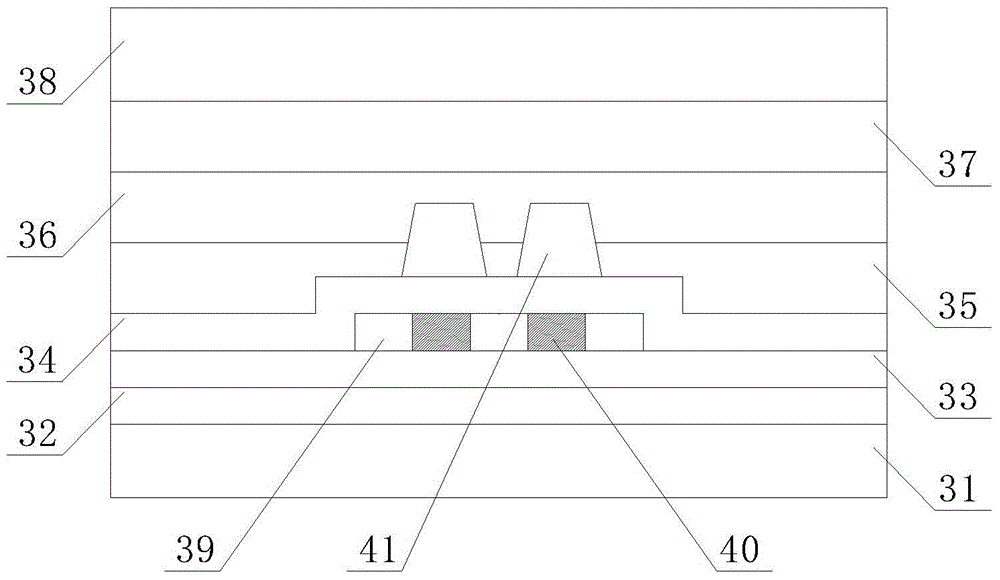

Display device, array substrate and manufacturing method thereof

ActiveCN102629611AAvoid destructionReduce etchingSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOptoelectronics

The invention relates to the technical field of display, in particular to a display device, an array substrate and a manufacturing method thereof. The array substrate comprises a substrate and a plurality of pixel units; each pixel unit comprises a thin film transistor and a pixel electrode; the thin film transistor comprises a source electrode, a drain electrode, an active layer, a grid electrode insulating layer and a grid electrode, wherein the source electrode and the drain electrode are oppositely arranged on the substrate and forms a channel of the thin film transistor; the active layer is positioned above the source / drain electrode and the channel; the grid electrode insulating layer and the grid electrode are arranged above the active layer in sequence; and the pixel electrode is positioned in an area outside the thin film transistor in the pixel unit and extends to the upper part of the drain electrode and is overlapped with the drain electrode. Through the array substrate provided by the invention, as the active layer is positioned above the source / drain electrode, the active layer can be prevented from being damaged in the forming process of the source / drain electrode. Moreover, when the active layer is made of metallic oxide, a blocking layer can be omitted, and further, the process flow is simplified, the production efficiency is improved, and the production cost is reduced.

Owner:BOE TECH GRP CO LTD

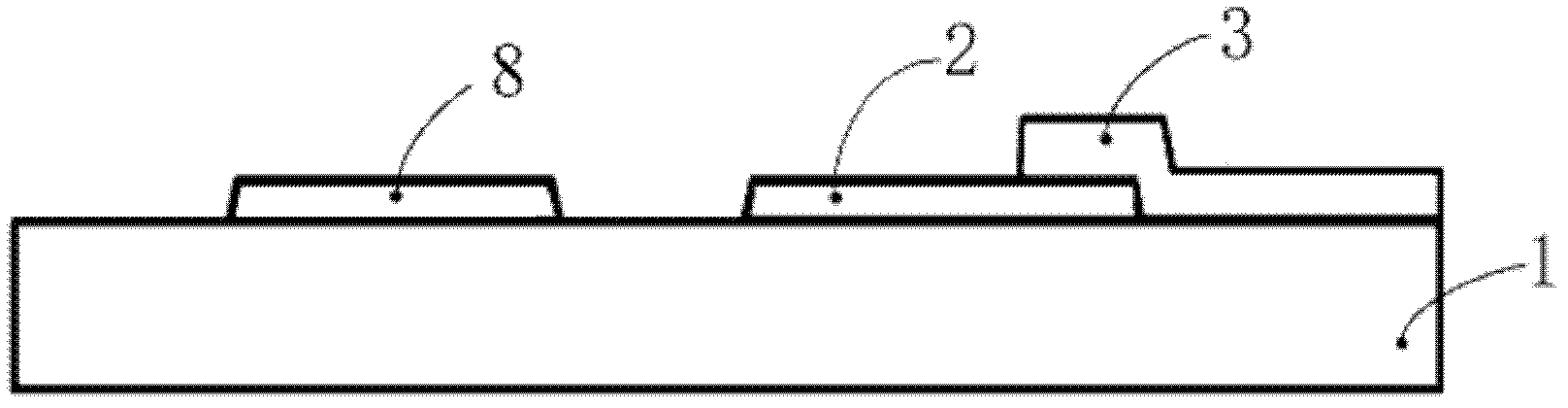

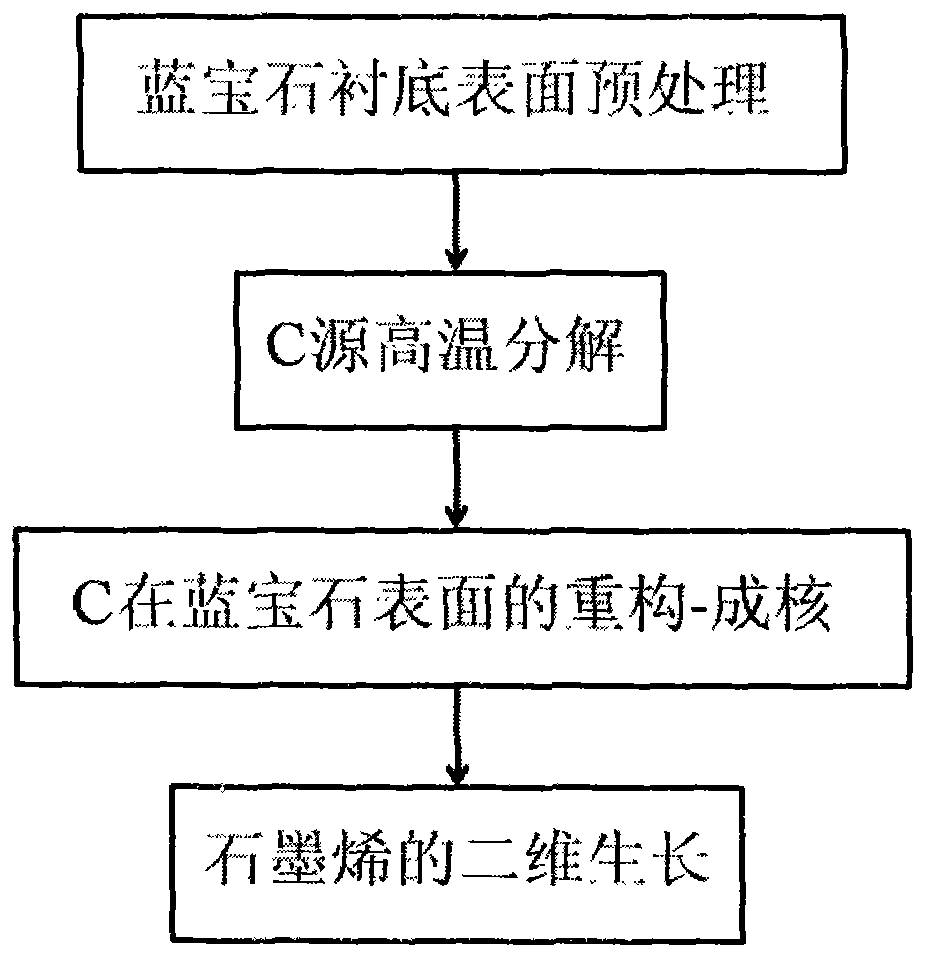

Graphene CVD (chemical vapor deposition) direct epitaxial growth method based on sapphire substrate and device fabricated with method

InactiveCN102915913AImprove reliabilityExcellent electrical propertiesSemiconductor/solid-state device manufacturingThermal chemical vapor depositionControllability

The invention discloses a graphene CVD (chemical vapor deposition) direct epitaxial growth method based on a sapphire substrate. Sapphire is used as the substrate, the sapphire substrate is reasonably pre-processed, and the growth pressure, the flow rate and the temperature are regulated, so that the graphene can directly grow on the sapphire without metals as the catalyst, and the grown graphene can be directly used to fabricate various devices without being transferred, so that the electrical characteristics and reliability of the device can be enhanced, and the complexity of fabrication of the device can be reduced. The large-area graphene material with semiconductor cleanliness is grown, the controllability of a single layer is more than 80%, and the area of a wafer is up to 8 inches.

Owner:XIDIAN UNIV

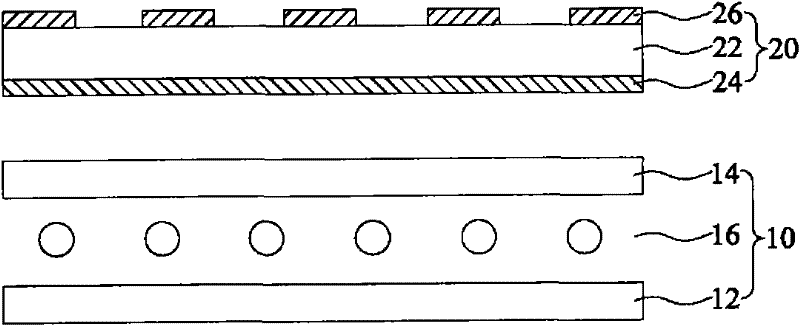

Liquid crystal display device and method for manufacturing the same

ActiveCN102478738AReduce thicknessSimple manufacturing process stepsStatic indicating devicesNon-linear opticsLiquid-crystal displayPatch cable

A liquid crystal display device and a method for manufacturing the same are disclosed. The liquid crystal display device comprises gate and data lines arranged to cross each other on a substrate to define a plurality of pixels; a pixel electrode formed in each of the plurality of pixels; a common electrode forming an electric field together with the pixel electrode, patterned to sense a touch of a user; a sensing line discontinuously formed on the common electrode and electrically connected with the common electrode; a jump line formed below the common electrode to electrically connect discontinuous portions of the sensing line with one another; and first and second connection electrodes for electrically connecting the jump line with the sensing line, wherein the first connection electrode is connected with the jump line, and the second connection electrode is connected with the sensing line and the first connection electrode respectively. Because the common electrode is used as a sensing electrode, an independent touch screen is not needed on the liquid crystal panel.

Owner:LG DISPLAY CO LTD

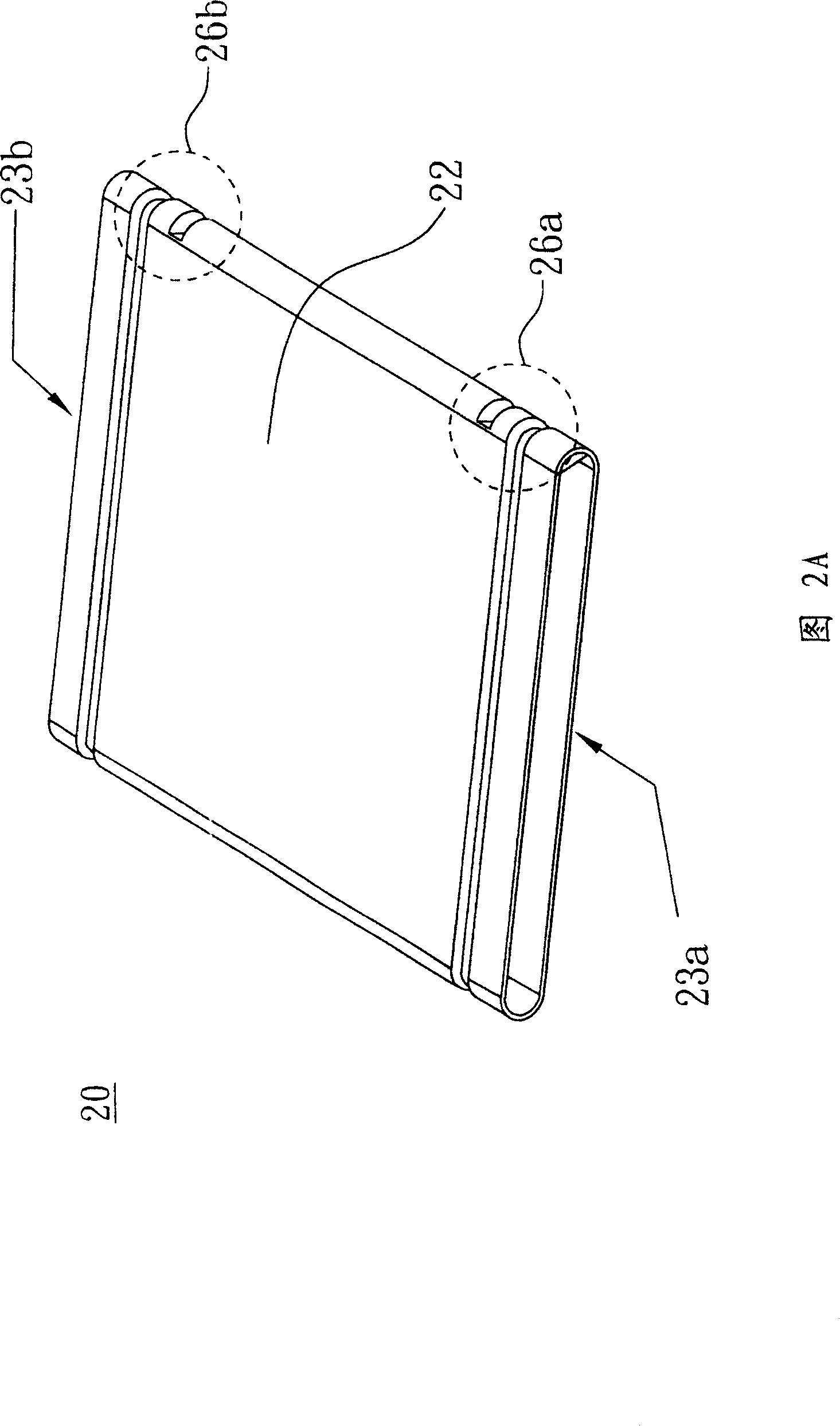

Heat dissipation module, temperature equalizing element and manufacturing method for temperature equalizing element

InactiveCN101666586ALess weld pathImprove reliabilityIndirect heat exchangersCooling/ventilation/heating modificationsWorking fluidEngineering

The invention discloses a heat dissipation module, a temperature equalizing element and a manufacturing method for the temperature equalizing element. The manufacturing method for the temperature equalizing element comprises the following steps: providing a flat hollow tube body of which the inner wall surface is distributed with continuous first capillary structures; providing at least one guideelement which is placed in the flat hollow tube body and of which surface is provided with second capillary structures; connecting the first and second capillary structures to form continuous capillary structures; and filling a working fluid into the flat hollow tube body, and sealing two ends of the flat hollow tube body. In addition, the invention also provides the temperature equalizing elementand the heat dissipation module comprising the temperature equalizing element, wherein the heat dissipation module is provided with the temperature equalizing element which is used on a heating element. The manufacturing method for the temperature equalizing element comprises the steps of providing the flat hollow tube body of which inner wall surface is provided with the first capillary structures, placing the at least one guide element with a guide capillary structure into the flat hollow tube body, and making the first capillary structures and the guide capillary structure form the continuous capillary structures by using a sintering process. The manufacturing method for the temperature equalizing element can provide better flowing path for the working fluid in the temperature equalizing element.

Owner:DELTA ELECTRONICS INC

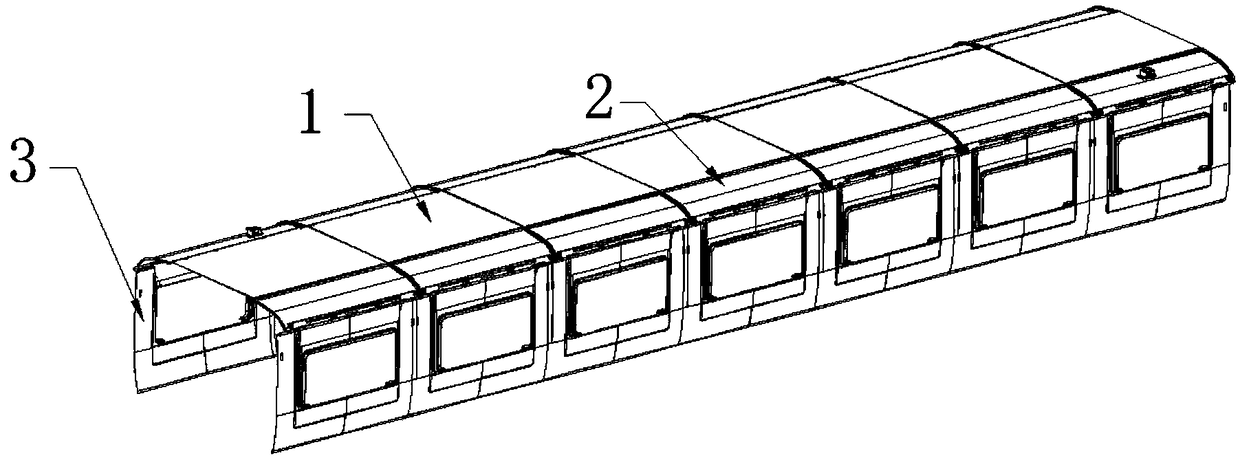

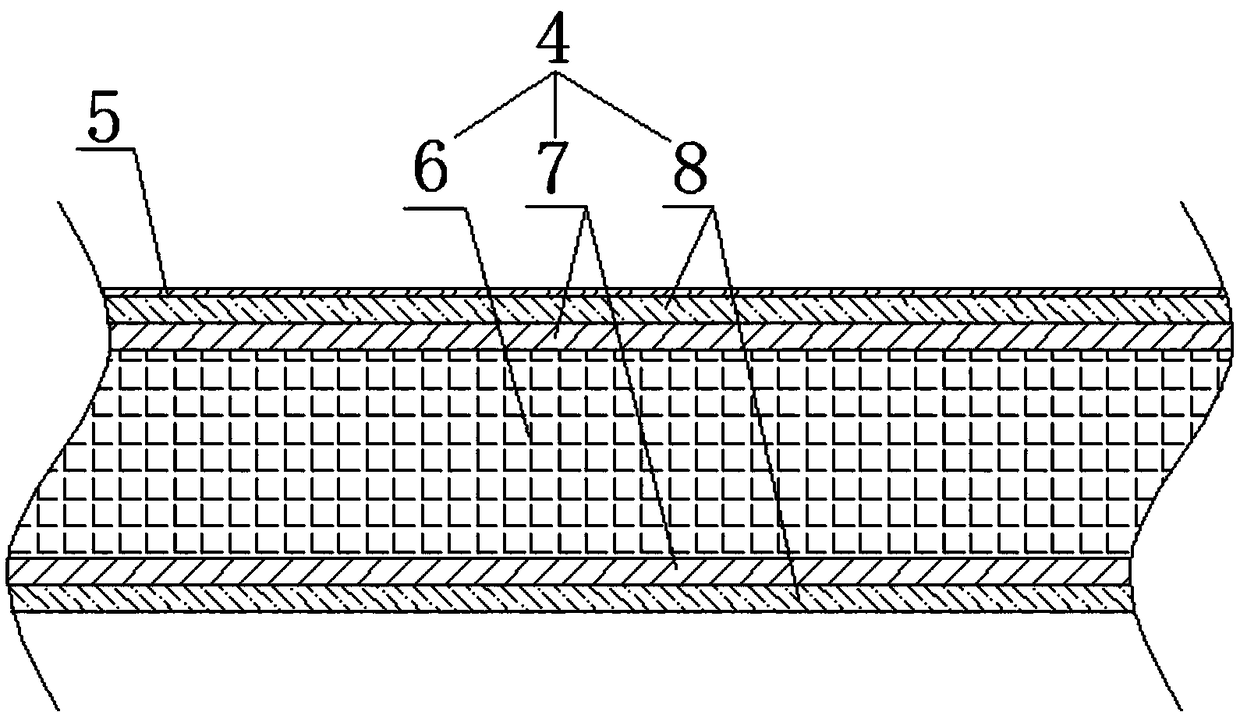

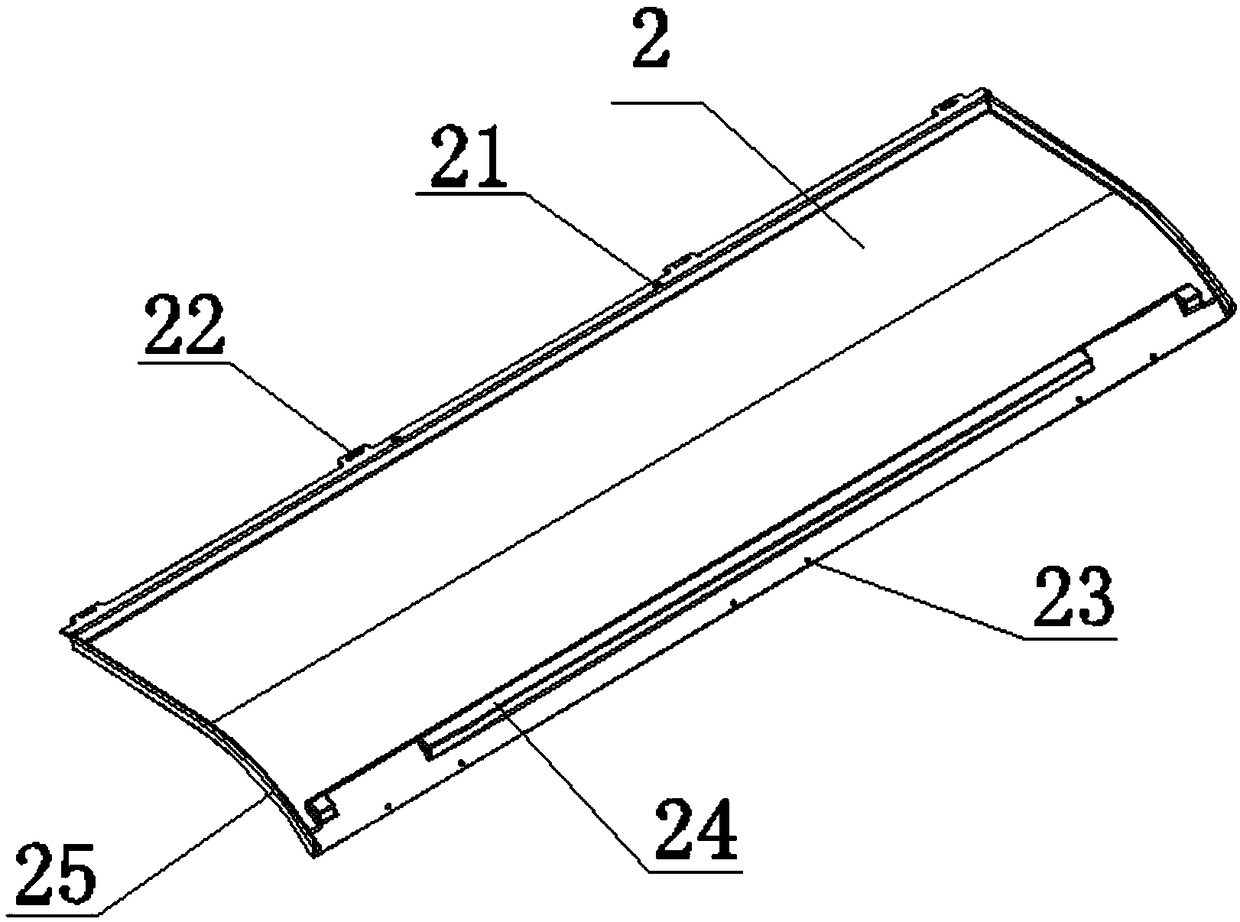

Lightweight composite material train interior trim part with high-strength coatings

PendingCN108859167ASimple manufacturing process stepsImprove impact resistanceSynthetic resin layered productsAxle-box lubricationHoneycombWall plate

The invention discloses a lightweight composite material train interior trim part with high-strength coatings. The train interior trim part comprises top plates, side top plates and wall plates; eachof the top plates, the side top plates and the wall plates comprises a composite sheet layer and the high-strength coating; and each composite sheet layer comprises a honeycomb material layer body, afiber material layer body and a polyurethane material layer body, wherein the fiber material layer body and the polyurethane material layer body are sequentially wrapped outside the honeycomb materiallayer body from inside to outside. Compared with the prior art, the train interior trim part has the advantages that the train interior trim part is prepared by utilizing the lightweight composite plates with the high-strength coatings, and a plurality of sheets are reasonably combined, so that the train interior trim part which is high in strength, light in weight, safe, environmentally friendly, low in cost and high in output is formed.

Owner:ZHEJIANG SANSE MOLD TECH

Array substrate of display device and manufacturing method of array substrate of display device

ActiveCN104022129AReduce parasitic capacitanceReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceElectrical impedance

The invention relates to a structure of a display device and a manufacturing field of the structure of the display device, in particular to an array substrate of the display device and a manufacturing method of the array substrate of the display device. A traditional CMOS technological process is improved, the characteristic that the impedance of an ITO / Ag / ITO is low is adopted, the traditional nine photomask processes in the CMOS process is decreased to be seven photomask processes, the manufacturing process steps are simplified, yield is improved, and meanwhile the advantages of high design redundancy, low power consumption, low process and design difficulty and the like of the traditional nine photomask processes are kept.

Owner:EVERDISPLAY OPTRONICS (SHANGHAI) CO LTD

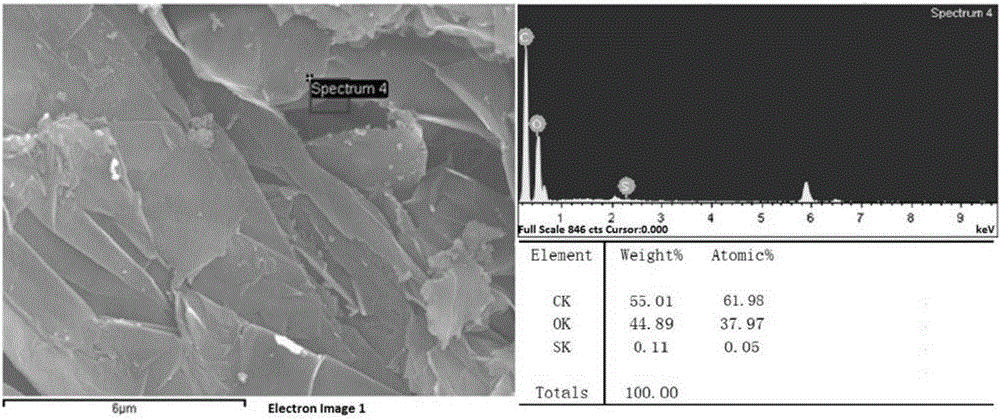

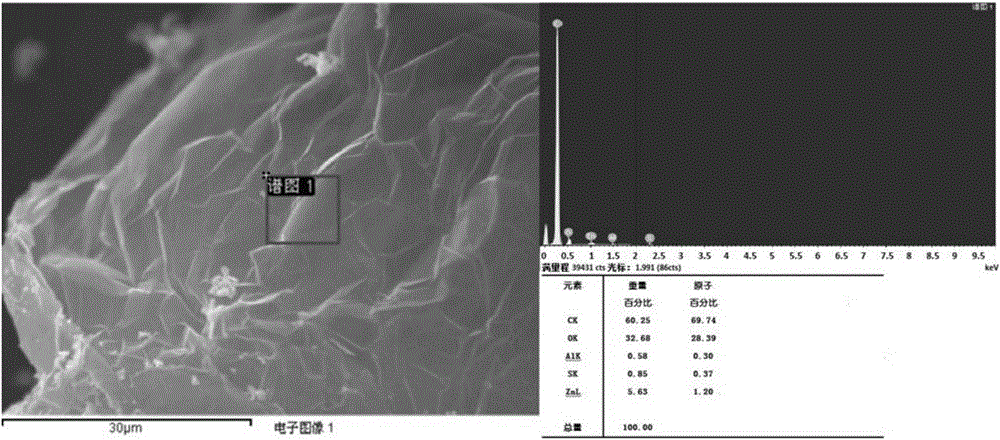

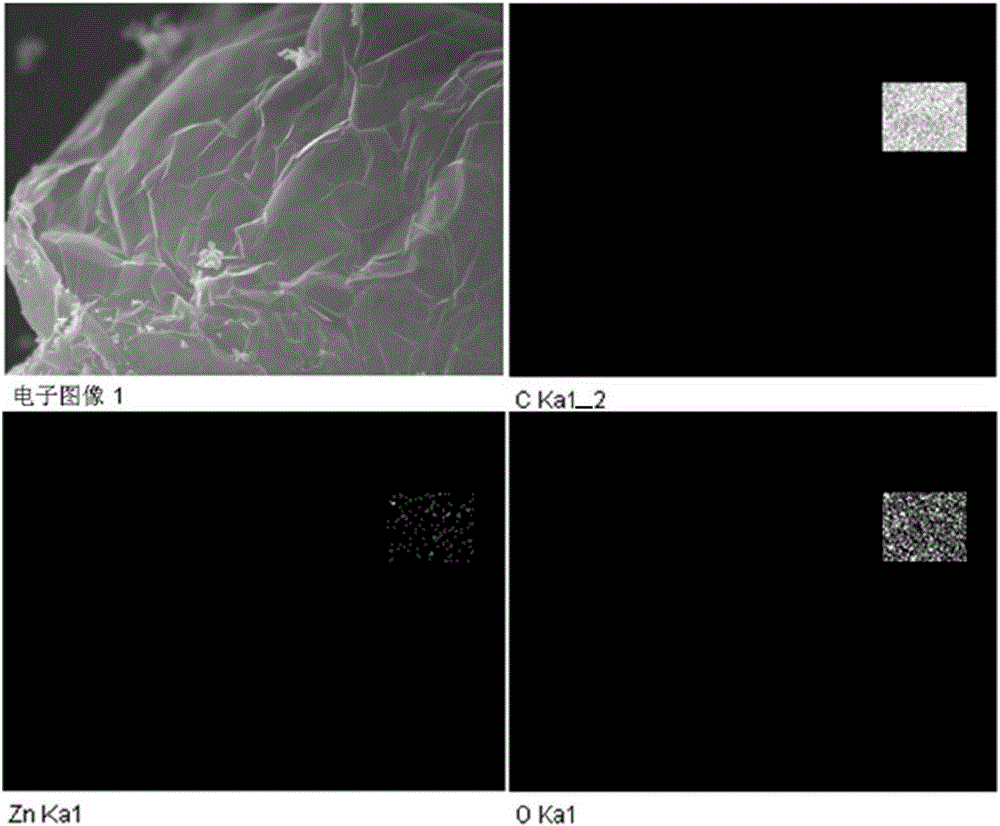

Method for preparing anode material of lithium ion battery by high-temperature reaction of expansible graphite and zinc powder

ActiveCN105244502ASimple manufacturing process stepsReduce the degree of oxidationCell electrodesSecondary cellsGas phaseOxygen

The invention relates to a method for preparing an anode material of a lithium ion battery by high-temperature reaction of expansible graphite and zinc powder. The method comprises the following steps of using the expansible graphite and the zinc powder as raw materials; carrying out high-temperature reaction of the expansible graphite and the zinc powder in a temperature condition of the zinc powder serving as an air phase; and preparing to obtain a composite electrode material of the expanded graphite and zinc oxide, wherein a vacuum environment is controlled or an inert gas is introduced during the reaction process. The method disclosed by the invention is a one-step reaction method, the problems of complicated step and long time consumption existing in the prior art by using the expanded graphite and a zinc source for wet synthesis are solved, and the preparation process is simplified; not only the zinc oxide is deposited on the surface of the expanded graphite and among layers, but also the oxidation-reduction reactions are included; and a part of oxygen in the expanded graphite is reduced by zinc, the oxidation degree of the expanded graphite is further reduced, meanwhile, the generated zinc oxide is taken as the electrode material, and the specific capacity of the electrode material is also improved.

Owner:SHANDONG UNIV

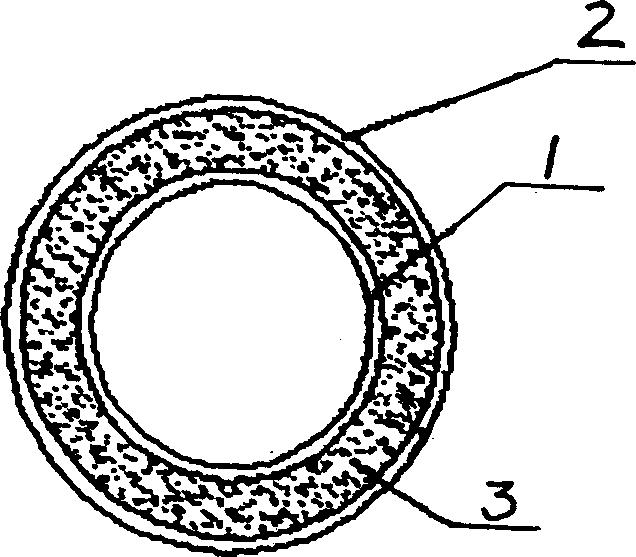

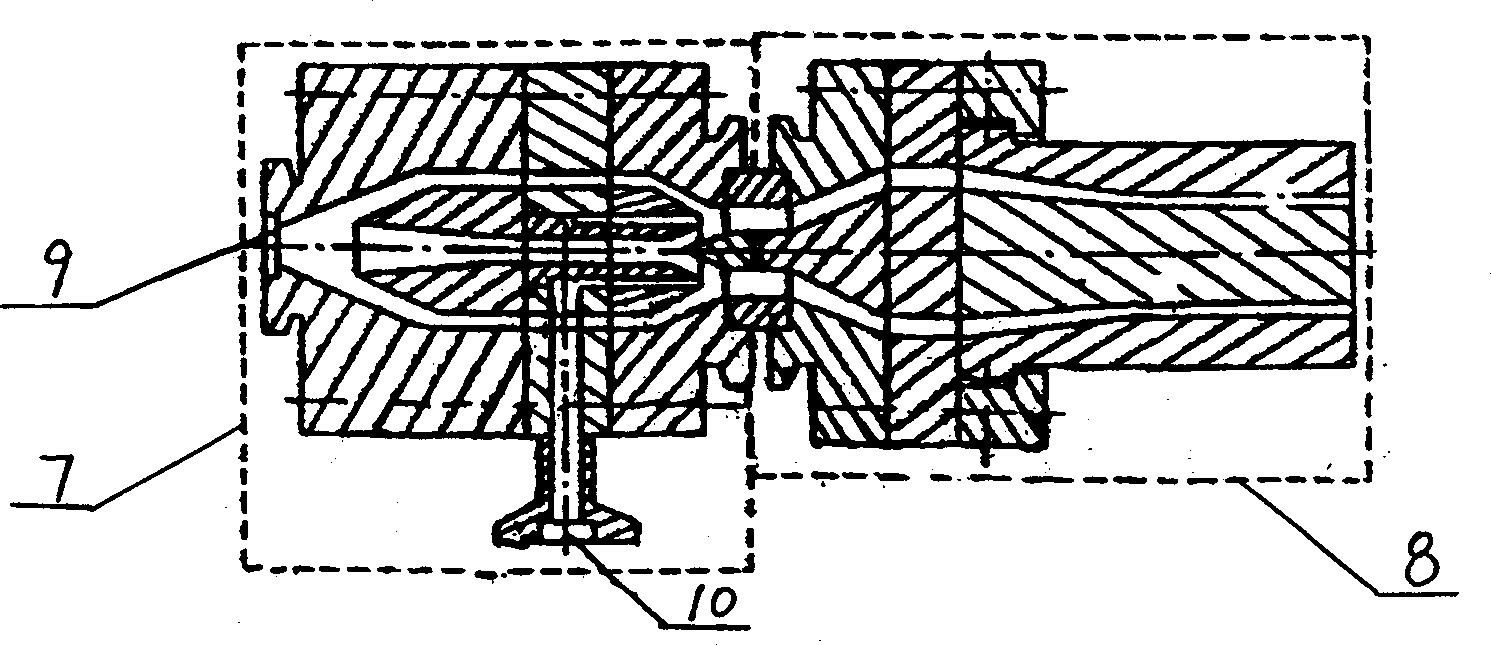

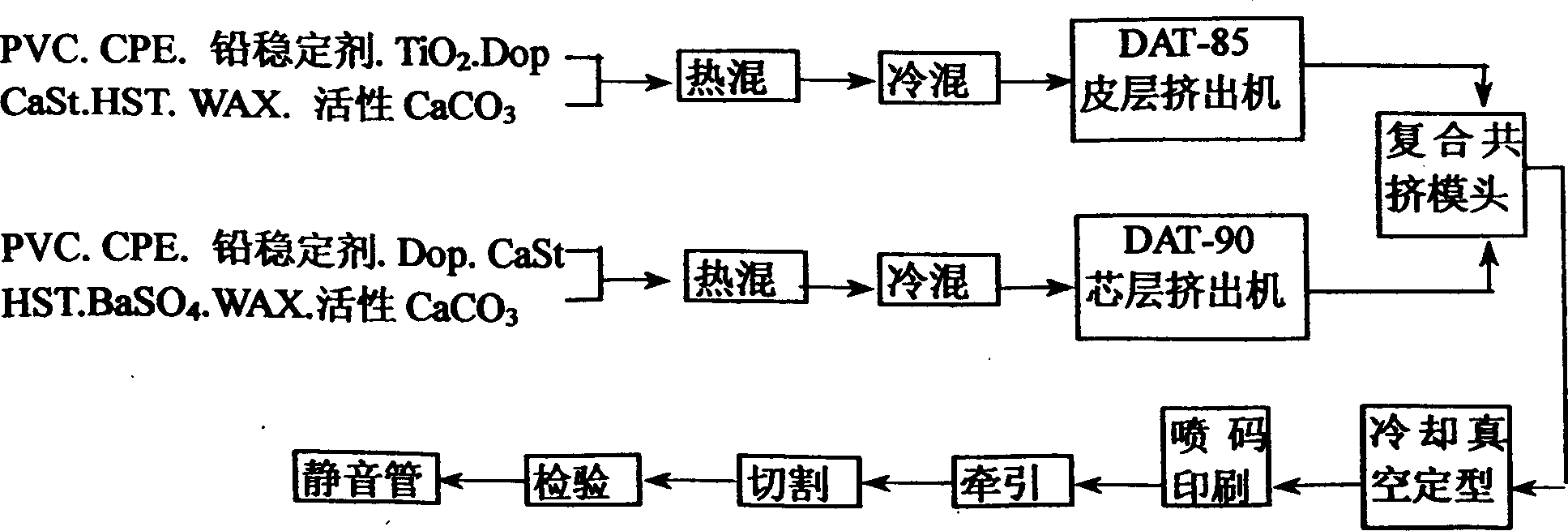

Silent polyvinyl chloride drain pipe

ActiveCN1486834AGood impact strength and tensile strengthSimple manufacturing process stepsChlorinated polyvinyl chlorideEngineering

The present invention is silent polyvinyl chloride drain pipe and its making process, and the silent polyvinyl chloride drain pipe features the extruded sound absorbing core layer between the outer layer and the inner layer. The sound absorbing core layer is produced with material including polyvinyl chloride in 100 portions, chlorinated polyvinyl chloride in 15-150 portions and barium sulfate in 50-500 portions. It has advantages of 2.7-12.9 dB lowered noise compared with common polyvinyl chloride drain pipe, rather high impact strength and tensile strength, simple production process and convenient use.

Owner:重庆顾地塑胶电器有限公司

Method for producing ibuprofen through multistage continuous reaction crystallization

InactiveCN110627629AResolve side effectsUniform particle sizePreparation from carboxylic acid saltsOrganic chemistry methodsNucleationSolvent

The invention discloses a continuous crystallization process for ibuprofen. The ibuprofen product is obtained in a multistage continuous crystallization manner; and multistage continuous reaction crystallization comprises the steps of oil forming through a reaction, 2-4-stage reaction crystallization and dehydrating washing, wherein a pH and a temperature of each step are regulated and controlled.According to the process, a burst nucleation phenomenon caused by oil separating during the reaction crystallization of the ibuprofen is effectively solved; the crystallization is stable in process conditions and simple in operation control; by taking water as a solvent, environmental pollution is reduced; and the obtained ibuprofen crystal is large and uniform in size, the product is high in purity and yield, the stability of running of the crystallization process and the quality of the product are improved, the production cost is reduced, and the stabilized industrial production of the ibuprofen is achieved.

Owner:SHANDONG XINHUA PHARMA CO LTD

Organic electroluminescent device and method for fabricating the same

InactiveCN1751400AIncrease brightnessHigh color purityOrganic chemistryElectroluminescent light sourcesOptoelectronicsOrganic electroluminescence

Disclosed are an organic electroluminescent device and a method for fabricating the same. The device includes a substrate, a first electrode formed on the substrate, an emission layer formed over the first electrode, and having a first emission area, a second emission area, and a third emission area, a hole blocking layer formed on the emission layer, the hole blocking layer being formed of the same substance as that of the third emission area, and a second electrode formed over the hole blocking layer.

Owner:LG DISPLAY CO LTD

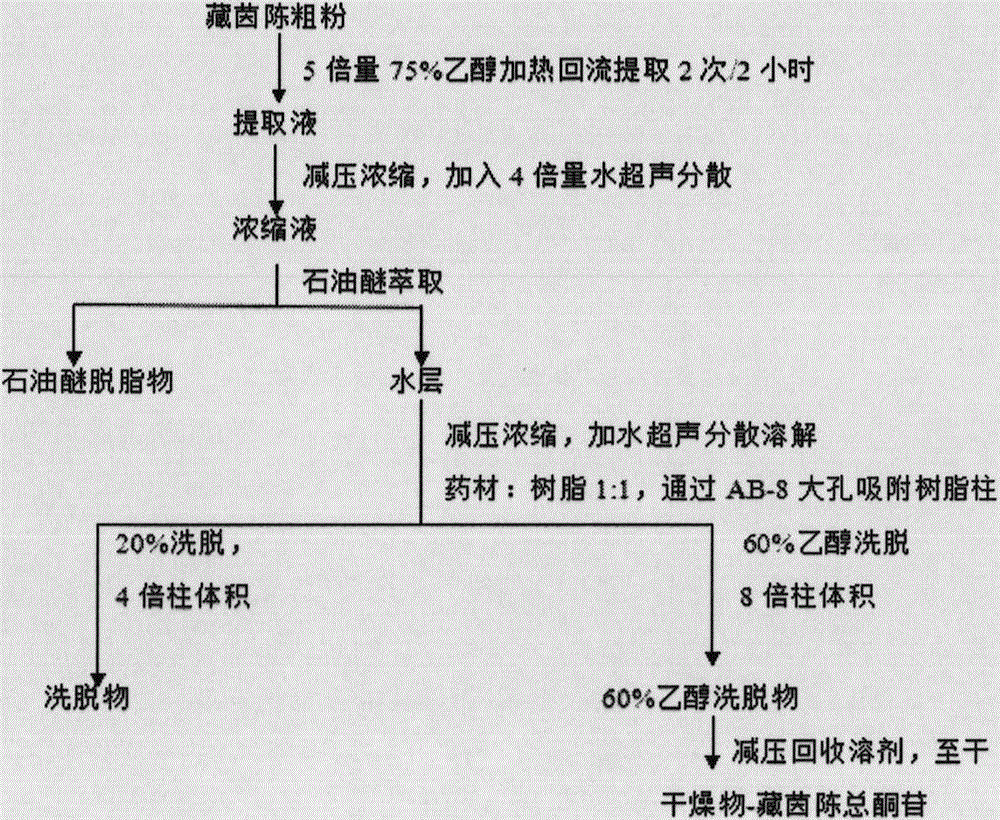

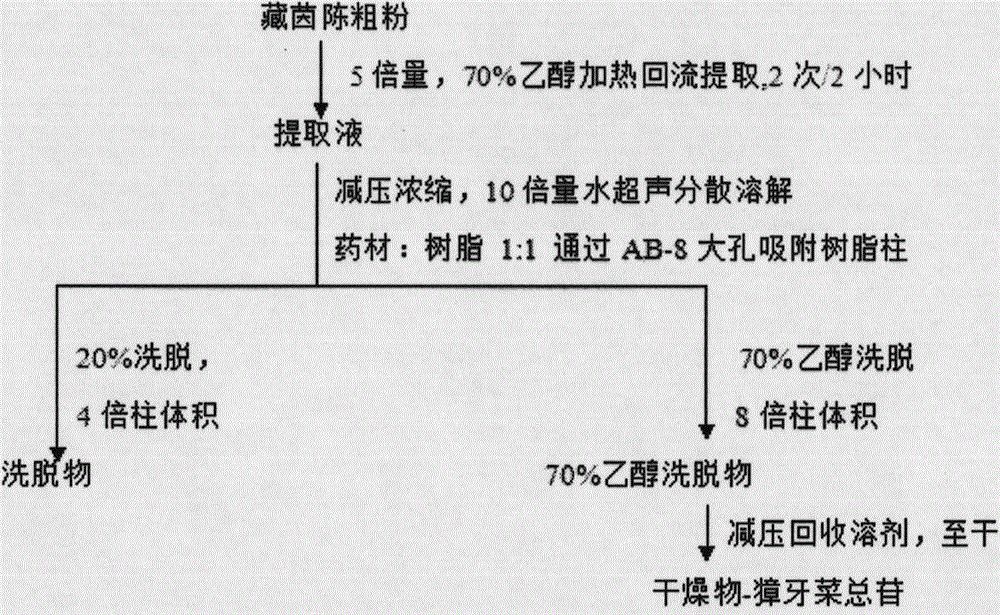

Tibetan artemisia capillaris extract and preparation method, drug composition and application thereof

InactiveCN104971088AImprove extraction efficiencyHigh content of ingredientsDigestive systemAntiviralsMedicineChronic hepatitis

The invention discloses a Tibetan artemisia capillaris extract, a preparation method, a drug composition and an application thereof. The Tibetan artemisia capillaris is Comastoma Pedunculatum[Rogle ex D.Dou]Holub. The Tibetan artemisia capillaris extract includes at least 25% by weight of Tibetan artemisia capillaries total flavonoid glycoside. Compared with a drug composition in the prior art, the drug composition has following advantages: the Tibetan artemisia capillaris extract is high in extraction efficiency, is concentrated in effective components, is simple in steps, is low in energy consumption and less in cost, is high in effective components, is less in impurities and is convenient to control in quality, has the effects of clearing heat and removing toxin, and dispelling liver and draining bile, and can be used for treating various acute and chronic hepatitis.

Owner:MINZU UNIVERSITY OF CHINA

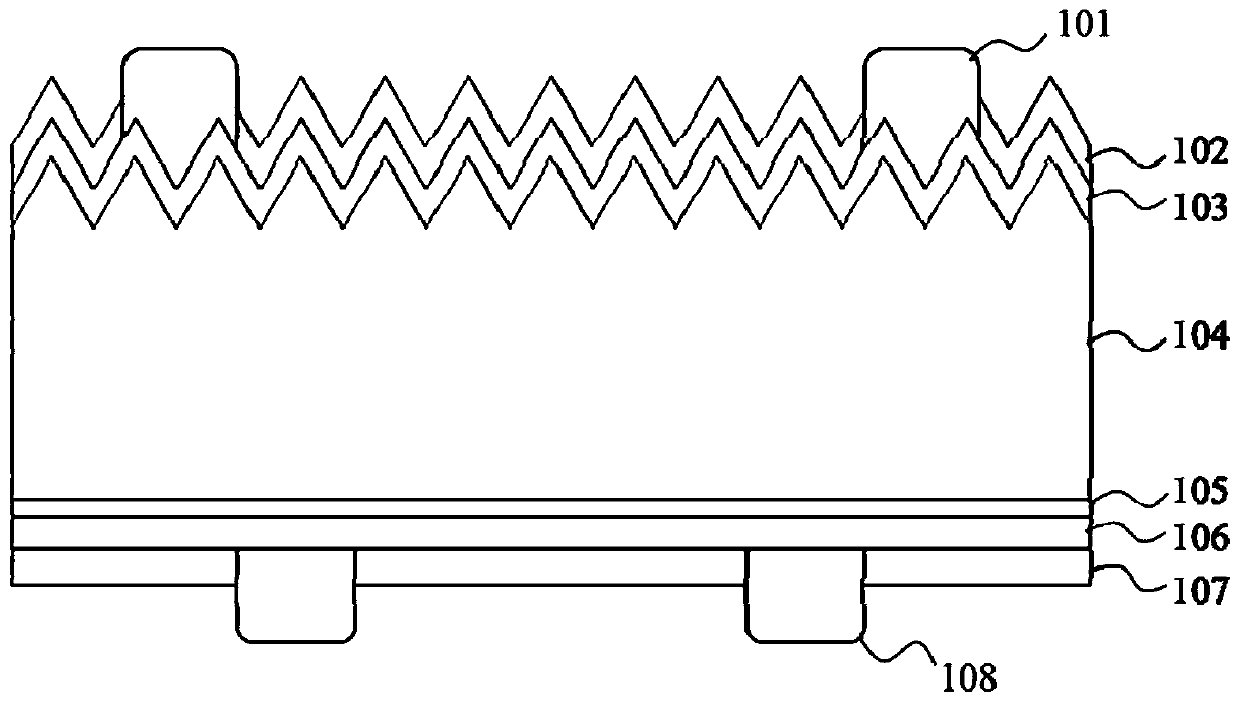

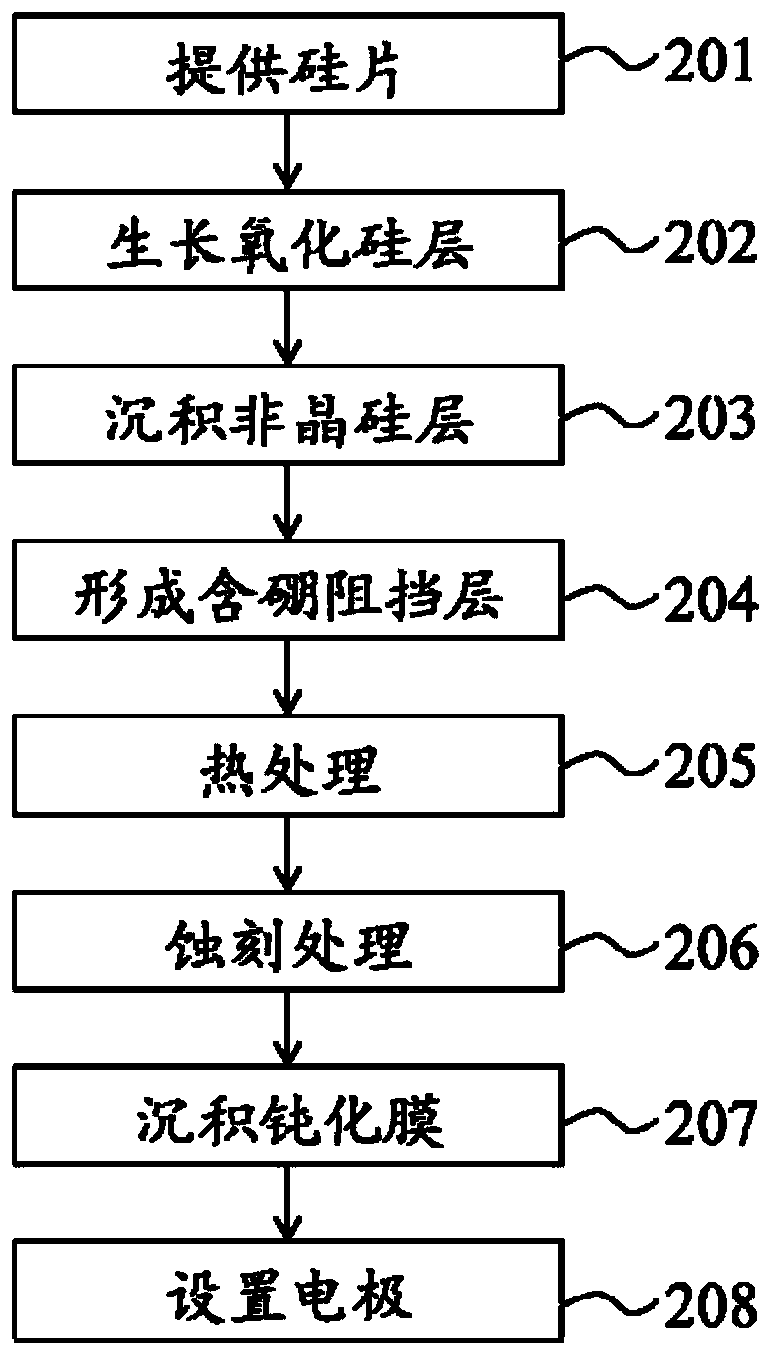

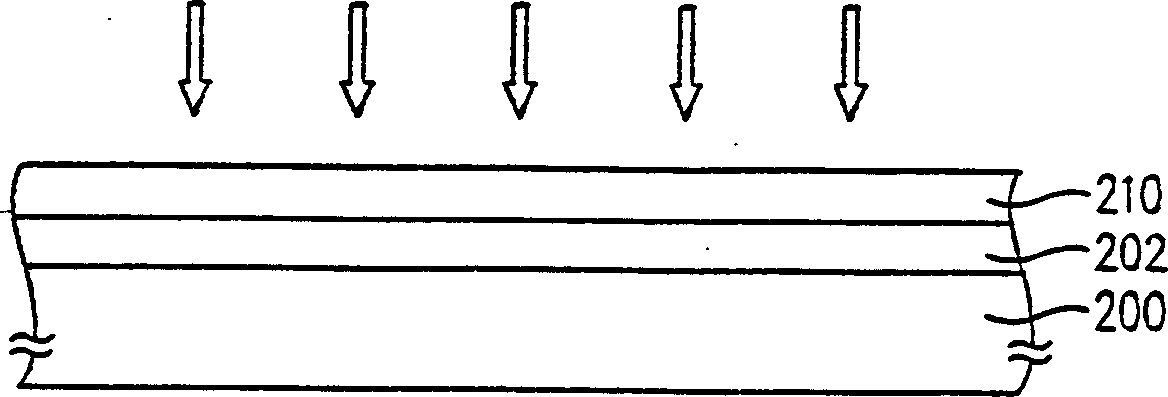

Preparation method of P-type passivation contact crystalline silicon solar cell

ActiveCN110212057AImprove yieldImprove efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingAmorphous siliconBoron containing

The invention provides a preparation method of a P-type passivation contact crystalline silicon solar cell, and relates to the technical field of solar cells. The method comprises the following stepsof providing a P-type silicon wafer; generating a silicon oxide layer on the back surface of the silicon wafer; depositing an amorphous silicon layer on the silicon oxide layer; coating the amorphoussilicon layer with boron paste and carrying out drying to form a boron-containing barrier layer on the amorphous silicon layer; carrying out heat treatment on the silicon wafer, wherein the heat treatment comprises first heat treatment, second heat treatment and third heat treatment which are sequentially and continuously carried out; carrying out etching treatment on the silicon wafer; depositinga first passivation film on the front surface of the silicon wafer, and depositing a second passivation film on the back surface of the silicon wafer; and arranging metal electrodes on the front surface and the back surface of the silicon wafer. The three independent high-temperature treatment processes of amorphous silicon crystallization, boron diffusion and phosphorus diffusion are integratedinto one process, so that the preparation process is simplified, the yield of the battery can be improved, the production period is shortened, and the productivity is improved. Due to the fact that the high-temperature treatment process of the battery is simplified, the influence on the minority carrier service life is reduced, and the battery efficiency is improved.

Owner:SUZHOU TALESUN SOLAR TECH CO LTD

Radio frequency SiP ceramic packaging shell and manufacturing method thereof

PendingCN112563237AReduce the risk of "air leaks"Improves sealing reliabilitySemiconductor/solid-state device detailsSolid-state devicesRadio frequency signalCoplanar waveguide

The invention discloses a radio frequency SiP ceramic packaging shell and a manufacturing method thereof, the radio frequency SiP ceramic packaging shell comprises a multi-layer wiring ceramic substrate, a metal enclosure frame and a metal cover plate, the metal enclosure frame is welded on the surface of the multi-layer wiring ceramic substrate, and the metal cover plate and the metal enclosure frame are welded and fixed so as to cover the technical enclosure frame; the multilayer wiring ceramic substrate is provided with a two-stage stepped impedance matching transmission line structure witha ground coplanar waveguide-similar coaxial-strip line-similar coaxial- strip ground coplanar waveguide, the radio frequency signal transmission insertion loss can be obviously reduced while the airtightness of the packaging shell is ensured, and the light weight and miniaturization of the packaging shell are realized.

Owner:NO 43 INST OF CHINA ELECTRONICS TECH GRP CETC

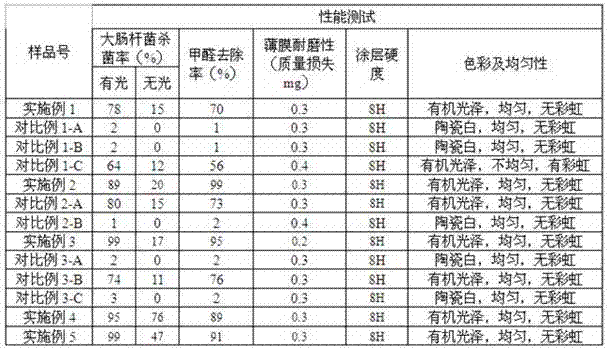

A process for manufacturing composite ceramic covered with a photocatalyst membrane

ActiveCN107473770AEnsure safetyEnsure hygieneWater closetsWash-standsProduction lineComposite ceramic

The invention provides a process for manufacturing composite ceramic covered with a photocatalyst membrane, and belongs to the technical field of ceramic. An adopted technical scheme is the process for manufacturing the composite ceramic covered with the photocatalyst membrane. The process includes preparing an aqueous solution of a peroxy-titanium system, with the concentration of the solution being 0.1-5 wt%; adding a surfactant into the aqueous solution to prepare a spraying solution; evenly coating clean and dry ceramic with the spraying solution; drying the surface; performing high-temperature calcination, with the calcination temperature being controlled to be 300-900 DEG C and the calcination time being 10-120 min; cooling the product to room temperature to obtain the composite ceramic. Beneficial effects of the process are that the process has simple and concise steps, is short in consumed time, high in efficiency and low in investment, and can be widely applied in various production lines of manufacture factories; and a product has excellent wear resistance, antibacterial performance and formaldehyde degrading performance, can efficiently clean air, can improve the environment, has beautiful gloss like organic precious stone, and is high-grade, elegant and beautiful.

Owner:唐山佐仑环保科技有限公司

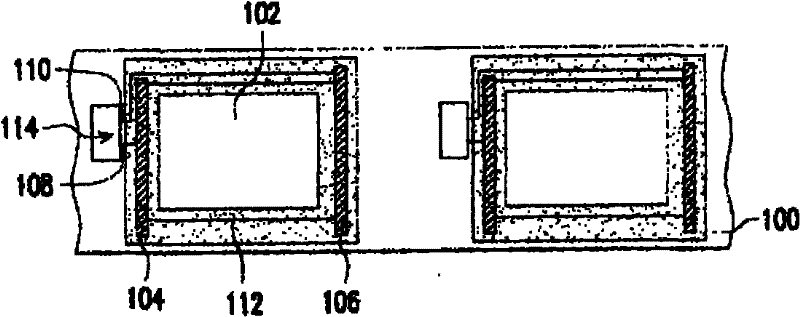

Touch panel roll and manufacturing method thereof

InactiveCN102193664AShorten manufacturing process timeEasy to shipInput/output processes for data processingTouch panelElectrical and Electronics engineering

The invention discloses a touch panel roll and a manufacturing method thereof. The method comprises a step of providing first and second structure rolls. A forming method of the first structure roll comprises steps of forming an opening in a first flexible substrate and extending a lead electrically connected with each electrode to the opening. A forming method of the second structure roll comprises steps of forming the lead electrically connected with each electrode and an independent lead corresponding to the lead in the first structure roll on a transparent conductive layer, wherein one ends of the leads are positioned at a position corresponding to the opening. The method also comprises a step of compressing the first structure roll and the second structure roll in a roll-to-roll mode.

Owner:IND TECH RES INST

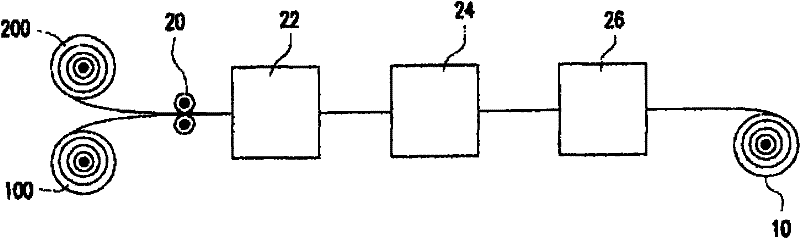

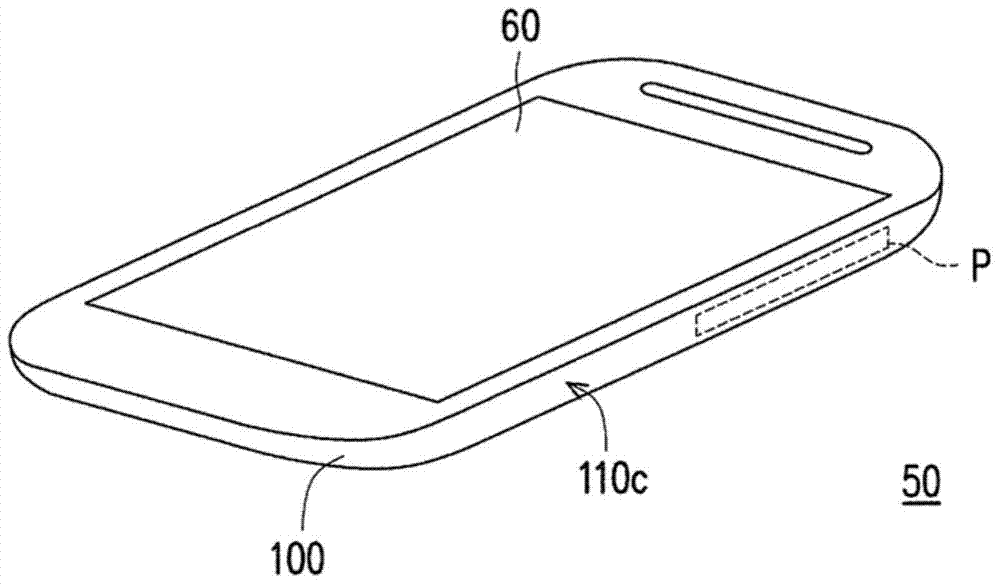

Electronic device and housing thereof

InactiveCN104780728AIntegrity guaranteedPrevent intrusionCasings/cabinets/drawers detailsElectronic switchingKey pressingElectrical resistance and conductance

The invention discloses an electronic device and a housing thereof. The housing comprises a housing body and an induction component, wherein the housing body is provided with a key part; the induction component comprises a first lead and two first contacts; the first lead is arranged on the internal surface of the housing body, and forms a strain induction pattern at the key part; and the first contacts are arranged on the internal surface of the housing body, and connected with the two ends of the first lead respectively. The strain induction pattern is suitable for allowing a resistance value to change along with deformation of the key part to generate an electrical signal.

Owner:HTC CORP

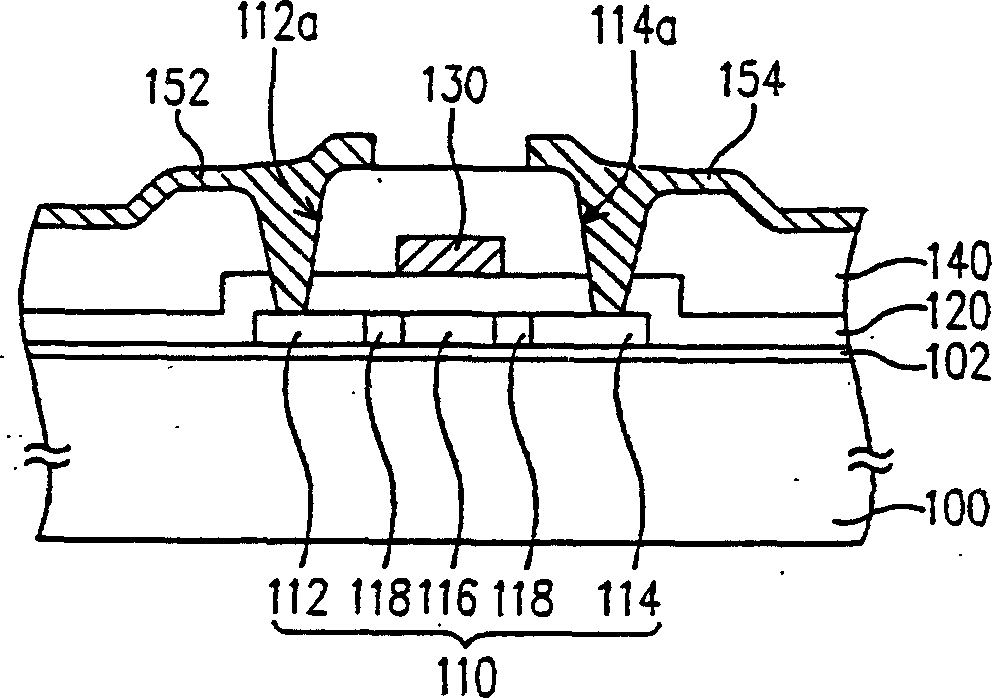

Film transistor and manufacturing method of its lightly mixed drain area

InactiveCN1758446ASimple manufacturing process stepsIncrease productivityTransistorSemiconductor/solid-state device manufacturingInsulation layerManufacturing technology

This invention relates to a method for manufacturing a light doped drain region of a film transistor, which first of all forms a polysilicon layer on the base plate then forms a grating insulation layer on the polysilicon layer, after that forms a buffer and a grating on the grating insulation layer, in which, the grating is set on the buffer and exposes part of the buffer, then carries out a doping manufacture technology and forms a light doped drain region in the polysilicon layer corresponding to the lower part of the buffer exposed by the grating.

Owner:CHUNGHWA PICTURE TUBES LTD

Semiconductor structure and manufacturing method thereof

ActiveCN109987573ASimple manufacturing process stepsIncrease productivityTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesSemiconductor structureEngineering

The invention discloses a semiconductor structure and a manufacturing method thereof. The semiconductor structure comprises a semiconductor substrate; a sacrificial layer on the semiconductor substrate; a functional layer located on the sacrificial layer; a pad on the functional layer; a protection layer which covers the functional layer and includes an opening through which the pad is exposed; and at least one through hole penetrating through the protection layer and the functional layer, and at least part of the sacrificial layer is exposed through the at least one through hole. In the semiconductor structure, the bonding pad is formed on the functional layer and exposed through the opening of the protection layer, so that after a part of the sacrificial layer is removed through the through hole, the protection layer does not need to be removed, the subsequent lead process can be directly carried out on the exposed bonding pad, the purpose of simplifying the manufacturing process steps is achieved, the production efficiency is improved, and the manufacturing cost is reduced.

Owner:无锡韦感半导体有限公司

Special brick for highway revegetation and preparation method of brick

The invention discloses a special brick for highway revegetation. The brick consists of 10-15% of lime powder, 5-15% of fly ash, 10-20% of plant straw powder, 30-40% of residual oil waste powder, 3-10% of a binding agent, 0.3-3% of a curing agent and 5-15% of cement. Furthermore, the invention discloses a preparation method of the special brick for highway revegetation. The special brick for highway revegetation disclosed by the invention has the advantages that the brick can achieve waste material utilization of raw materials, recycle the waste materials, reduce the occupied land area of the wastes in the city and improve the surrounding environment of the city; after being molded, the brick is free from emission of any toxic substance, so that the environment is protected; and the preparation process is relatively simple in step and the obtained product is good in quality.

Owner:ANHUI POPULAR SCI PROD ENG RES CENT

Environment-friendly curbstone for landscape architecture construction and production method therefor

InactiveCN106477984AImprove the surrounding environmentSimple manufacturing process stepsTraffic signalsRoad signsEnvironmental resistancePollution

The invention discloses environment-friendly curbstone for landscape architecture construction. The curbstone is prepared from the following raw materials in parts by weight: 15-20 parts of pulverized coal ash, 16-22 parts of clay, 8-10 parts of polypropylene fibers, 3-5 parts of epoxy resin, 10-14 parts of silicon micropowder, 1-2 parts of foamer, 18-24 parts of yellow sand, 35-48 parts of cement and 28-36 parts of water. A method for producing the environment-friendly curbstone comprises the steps: adding water into the pulverized coal ash, carrying out stirring for 1 to 2 hours, carrying out uniform mixing so as to form slurry, and maintaining the temperature of the slurry to 50 DEG C to 55 DEG C; uniformly mixing and stirring the clay, the yellow sand and the cement so as to form a dry material; adding the polypropylene fibers, the epoxy resin and the silicon micropowder into the slurry mixture in twice, then, adding the dry material into the mixture, carrying out intensive mixing, then, adding the foamer into the mixture, carrying out stirring for 20 minutes so as to form a mixed slurry material, and maintaining the temperature of the mixed slurry material to 50 DEG C to 55 DEG C so as to control the fluidity of the slurry material to 30cm; and pouring the slurry material into a mold body, carrying out standing for 60 minutes, transferring the mold body into a steam kettle, and carrying out curing for 8 hours. According to the environment-friendly curbstone for landscape architecture construction and the production method therefor, the used raw materials can achieve waste utilization, and the raw materials of the curbstone are pollution-free, so that the curbstone is relatively especially satisfactory for landscape architecture.

Owner:安徽瀚一规划设计院有限公司