Preparation method of vertical silicon nanowire field effect transistor

A field-effect transistor and silicon nanowire technology, which is applied in nanotechnology, nanotechnology, semiconductor/solid-state device manufacturing, etc., can solve the problems of vertical silicon nanowire field-effect transistors, such as difficult source-drain and gate self-alignment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0099] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments, and a process scheme for implementing a vertical silicon nanowire field-effect transistor with a small parasitic resistance proposed by the present invention is specifically provided, but the scope of the present invention is not limited in any way. scope.

[0100] A vertical silicon nanowire field effect transistor with a channel length of about 90 nanometers and a diameter of about 10 nanometers was prepared according to the following steps:

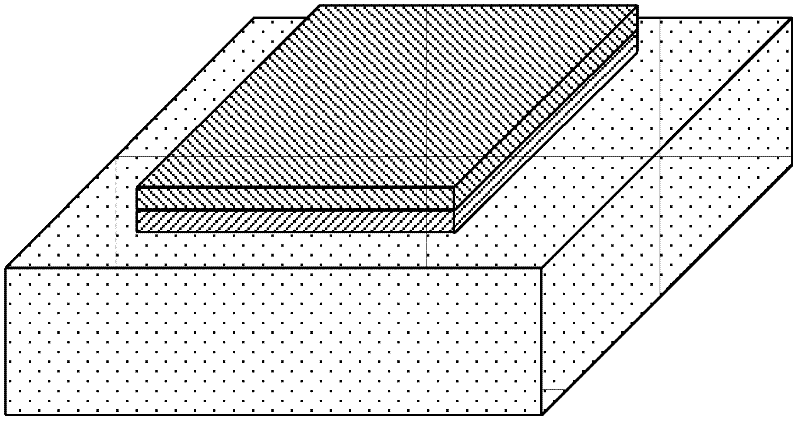

[0101] 1. Low pressure chemical vapor deposition silicon oxide 300

[0102] 2. Low pressure chemical vapor deposition silicon nitride 1000

[0103] 3. Optical lithography to define the active area;

[0104] 4. Anisotropic dry etching 1000 silicon nitride;

[0105] 5. BHF solution corrosion 300 Silicon oxide, overetched for 5s, such as Figure 1A shown;

[0106] 6. Remove the photoresist;

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More