Optical exposing method, and method for applying optical exposure in preparation of silicon material vertical hollow structure

An optical exposure and hole technology, used in microlithography exposure equipment, photosensitive material processing, manufacturing of microstructure devices, etc., can solve the problems of expensive, difficult to use, and high cost, and achieve low production cost, simple operation, and repeatability. good effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

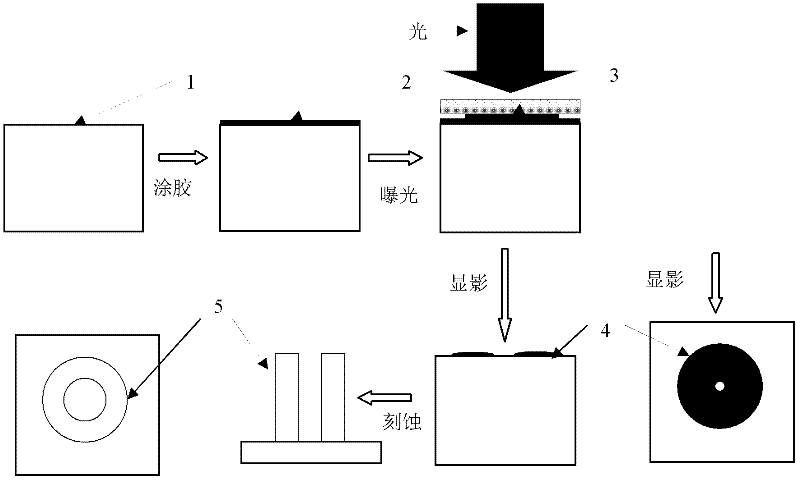

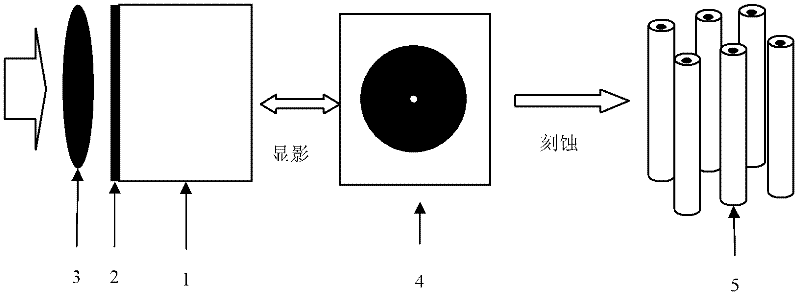

Method used

Image

Examples

example 1

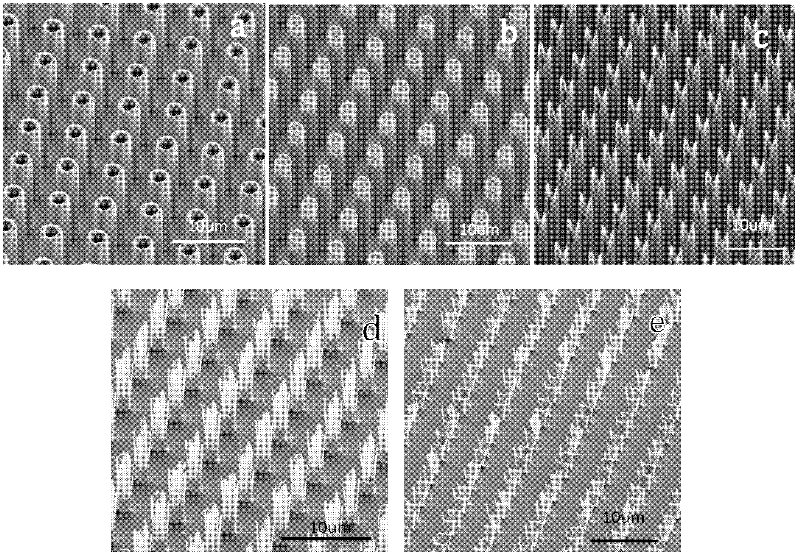

[0057] The silicon tubular array structure prepared in this example is shown in the attached image 3 (a) The silicon tube has a wall thickness of 200 nanometers, an inner diameter of 300 nanometers, and a height of 20 microns. The specific preparation method is as follows:

[0058] 1) Surface treatment of silicon wafer: Take a silicon substrate 1 and use a conventional semiconductor cleaning process, that is, ultrasonically clean it in acetone, alcohol and deionized water in sequence, and dry it with nitrogen;

[0059] 2) Glue coating: S1813 photoresist 2 is spin-coated on the silicon substrate 1, and the spin coating speed is controlled to obtain a 500-nanometer thick photoresist coating;

[0060] 3) Pre-baking: Bake the photoresist-coated silicon wafer obtained in step 2) on a hot plate at 150°C for 0.5 minutes;

[0061] 4) Exposure: select a mask 3 with a solid circular array pattern with a radius of 1 micron. Expose on the MA6 UV exposure machine. During the exposure process, th...

example 2

[0065] The silicon tubular array structure prepared in this example is shown in the attached image 3 (b) The silicon tube has a wall thickness of 100 nanometers, an inner diameter of 350 nanometers, and a height of 20 microns. The specific preparation method is as follows:

[0066] 1) Surface treatment of silicon wafer: Take a silicon substrate 1 and use a conventional semiconductor cleaning process, that is, ultrasonically clean it in acetone, alcohol and deionized water in sequence, and dry it with nitrogen;

[0067] 2) Glue coating: S1813 photoresist 2 is spin-coated on the silicon substrate 1, and the spin coating speed is controlled to obtain an 800 nm thick photoresist coating;

[0068] 3) Pre-baking: Bake the photoresist-coated silicon wafer obtained in step 2) on a hot plate at 115°C for 1 minute;

[0069] 4) Exposure: select a mask 3 with a solid circular array pattern with a radius of 1 micron. Expose on the MA6 UV exposure machine. During the exposure process, the Poisson...

example 3

[0073] For the V-shaped tubular array structure of this example, see the attached image 3 (c) The prepared silicon tube has a wall thickness of 100 nanometers, an inner diameter of 350 nanometers, and a height of 30 microns. The specific preparation method is as follows:

[0074] 1) Surface treatment of silicon wafer: Take a silicon substrate 1 and use a conventional semiconductor cleaning process, that is, ultrasonically clean it in acetone, alcohol and deionized water in sequence, and dry it with nitrogen;

[0075] 2) Glue coating: S1813 photoresist 2 is spin-coated on the silicon substrate 1, and the spin coating speed is controlled to obtain an 800 nm thick photoresist coating;

[0076] 3) Pre-baking: Bake the photoresist-coated silicon wafer obtained in step 2) on a hot plate at 115°C for 1 minute;

[0077] 4) Exposure: Select the mask 3 with a solid circular array pattern with a radius of 1 micron, and expose it on the MA6 UV exposure machine. During the exposure process, the P...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Wall thickness | aaaaa | aaaaa |

| Wall thickness | aaaaa | aaaaa |

| Diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More