Preparation method for FS-IGBT device

A device and semiconductor technology, applied in the field of power semiconductor devices, can solve problems such as high annealing temperature, easy oscillation, and influence on device reliability, so as to ensure the integrity of silicon wafers, reduce equipment requirements, and excellent device performance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

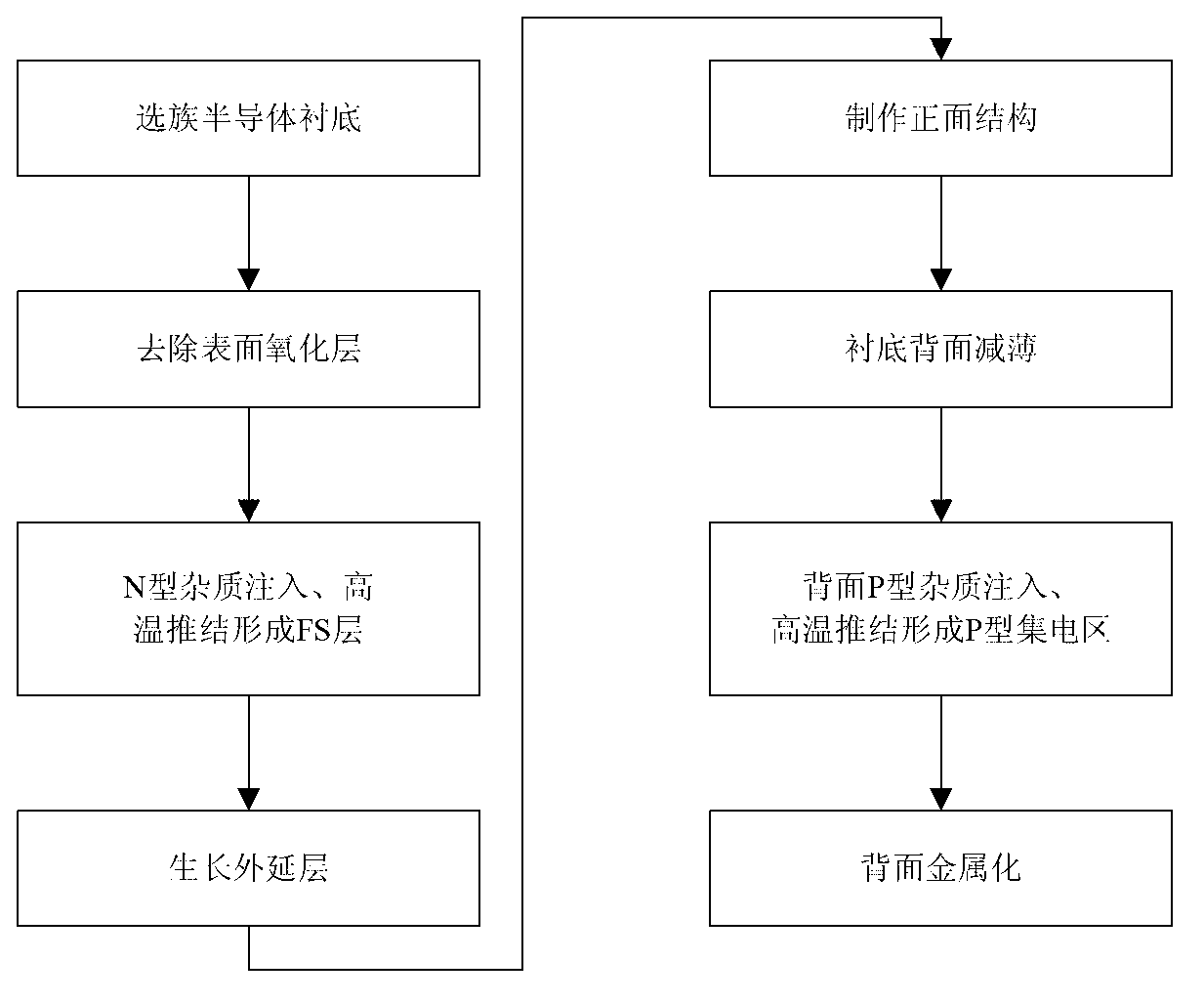

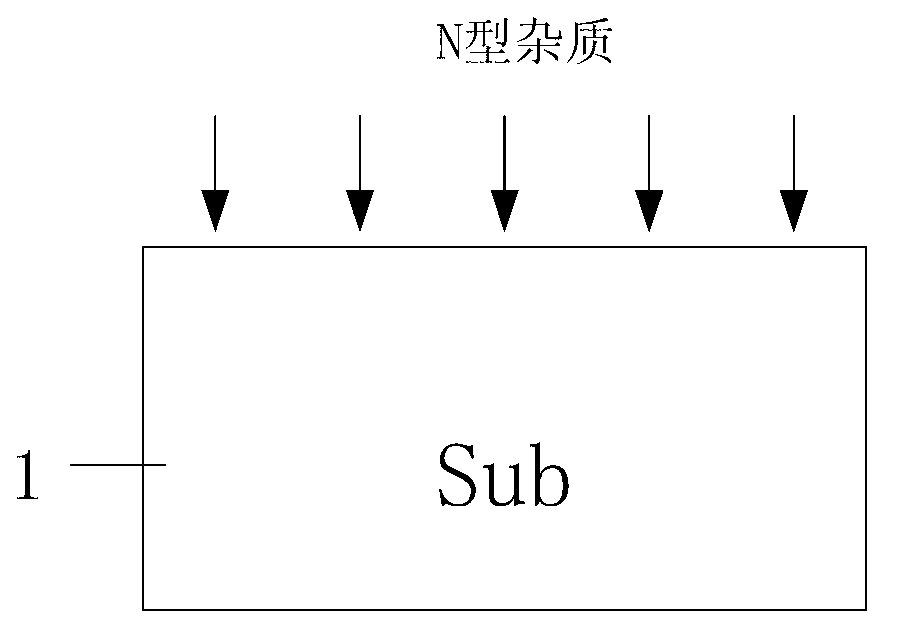

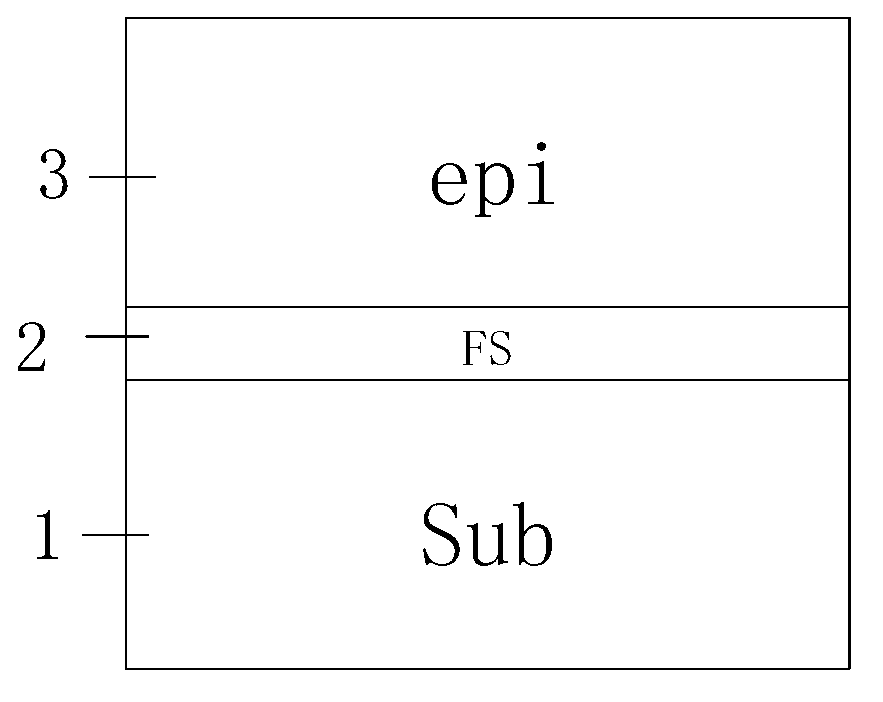

[0032] A method for manufacturing a power device, taking a trench field stop type insulated gate bipolar transistor as an example, includes selecting a silicon wafer, removing a surface oxide layer, injecting N-type impurities and pushing the junction at high temperature to form an FS layer, growing an epitaxial layer, growing Field oxide layer, lithography active area and field limiting ring terminal, grow scattering oxide layer and inject boron, etch away scattering oxide layer and anneal push junction, photolithography emitter area, grow scattering oxide layer and implant N-type impurities, remove Scatter the oxide layer and anneal and push the junction, remove the oxide layer and deposit silicon nitride, photolithography the groove area and etch the Trench groove, grow the gate oxide layer, fill the polycrystalline, etch part of the polycrystalline and planarize, and oxidize the polycrystalline area And remove silicon nitride, deposit passivation layer, perform ohmic contac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More