Method for realizing submicron-level process line width in manufacturing of silicon carbide power electronic devices

A power electronic device, sub-micron technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as large on-resistance, affecting device performance, material damage, etc., to achieve low cost and simple process. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

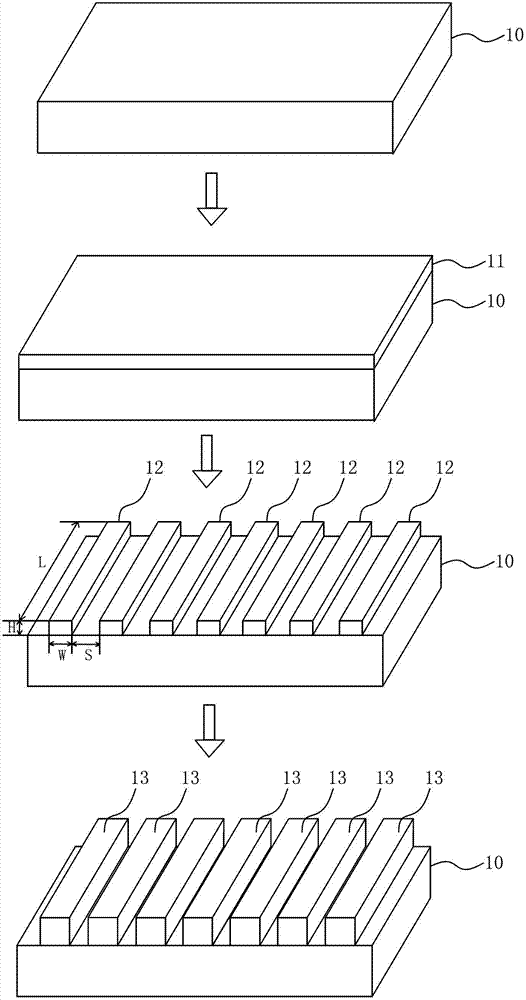

Embodiment 1

[0025] The material of the silicon carbide semiconductor thin film 10 is an N-type 4H-SiC (0001) 8° wafer with a thickness of 390 μm and a doping concentration of 1×10 16 cm -3 , wherein, the silicon carbide semiconductor thin film 10 needs to be cleaned by standard RCA, and RCA is the most commonly used wet chemical cleaning method.

[0026] The method for growing the silicon thin film layer 11 is a plasma-enhanced chemical vapor deposition method, wherein the crystal form of the silicon thin film layer 11 is polysilicon, and the thickness of the silicon thin film layer 11 is 0.7 μm.

[0027] The photolithography technique is a dry etching technique, the silicon thin film patterns 12 are in the shape of parallel strips, the etching width S between the silicon thin film patterns 12 is 2 μm, and the etching depth H is 0.7 μm. The width W of the portion is 2 μm, and the length L of the unetched portion thereof is 5 μm.

[0028] To oxidize the sample, put the sample into a tubu...

Embodiment 2

[0030] This embodiment is similar to the above-mentioned embodiment 1, except that the oxidation temperature of this embodiment is 1300° C., the oxidation time is 250 minutes, and the thickness of the oxide layer is about 1.5 μm. After the silicon thin film pattern 12 is oxidized, the width of each side is widened to 0.8 μm, so that the gap between the silicon oxide thin film 13 after the silicon thin film pattern 12 is oxidized becomes 0.4 μm.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More