Electrically erasable programmable read only memory (EEPROM) storage chip especial for intelligent ammeter

A technology of smart energy meter and storage chip, applied in the field of microelectronics, can solve the problems of large chip area, high size, high cost and system complexity, and high production cost, so as to reduce the device size and chip area, and save the number of manufacturing masks. , the effect of low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

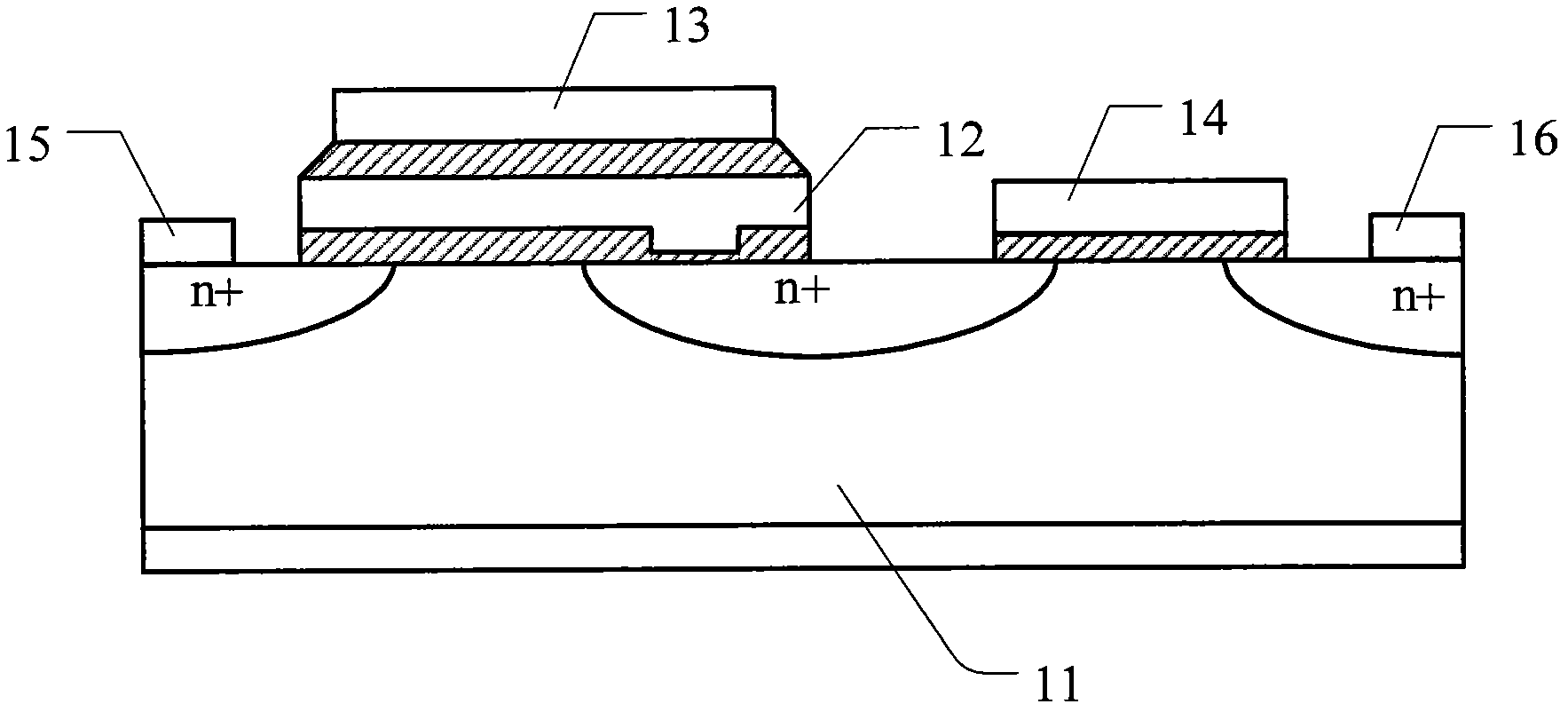

[0027] In this preferred embodiment, the core storage unit of the dedicated EEPROM memory chip for smart electric energy meters is a 1T storage unit composed of a single planar floating gate nanocrystalline memory transistor, and a high-density storage array is formed based on the 1T storage unit; The structure of the EEPROM can be used, or Nor Flash or its improved structure (such as DiNOR, DuSNOR, etc.), can also be designed according to the application scenario needs (such as specific chip specifications, capacity and other related parameters) to design a specific structure, as long as it can Ensure that each memory cell (single bit) in the memory array can be flexibly addressed, programmed, erased and other operations; the write mode of the memory cell selects the FN tunneling method or the channel hot electron injection method (such as CHEI , SSI, etc.); the erasing method of the memory cell selects the FN tunneling method or the hot hole band band tunneling injection (BBHH...

no. 2 example

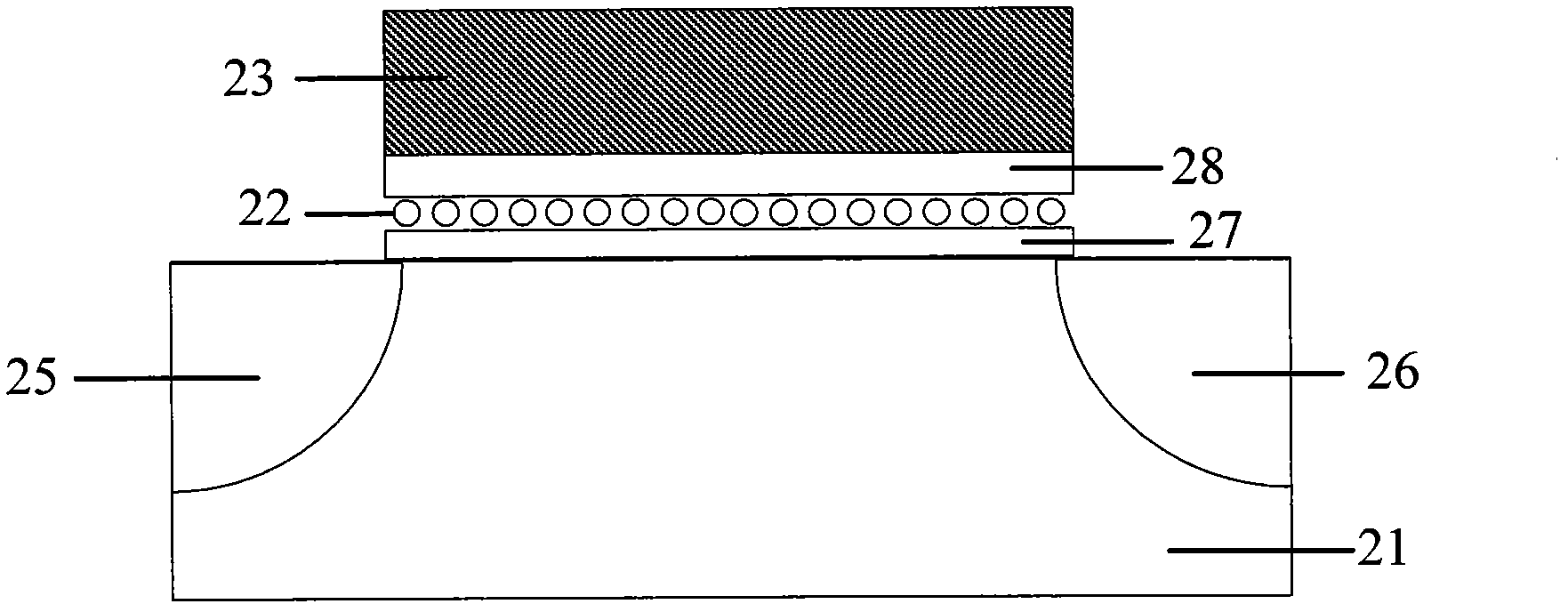

[0034] In this preferred embodiment, the nanocrystalline memory cell of the dedicated EEPROM memory chip for smart energy meters is a 1.5T memory cell composed of nanocrystalline memory transistors with a split gate structure, and a high-density memory array is formed based on the 1.5T memory cell. Reference image 3 , Shows a schematic diagram of the nanocrystalline memory cell structure of the second embodiment of the EEPROM memory chip dedicated for smart energy meters of the present invention, including: Si substrate material 31; N+ formed by heavily doping the N-type substrate region of the substrate material 31 The source conductive region 35 and the N+ drain conductive region 36; the select gate dielectric layer 39 covering the channel surface and located under the transistor select gate 34; the tunneling dielectric layer 37 covering the channel surface and located under the transistor control gate 33; transistor The nanocrystalline storage layer 32 below and on the side ...

no. 3 example

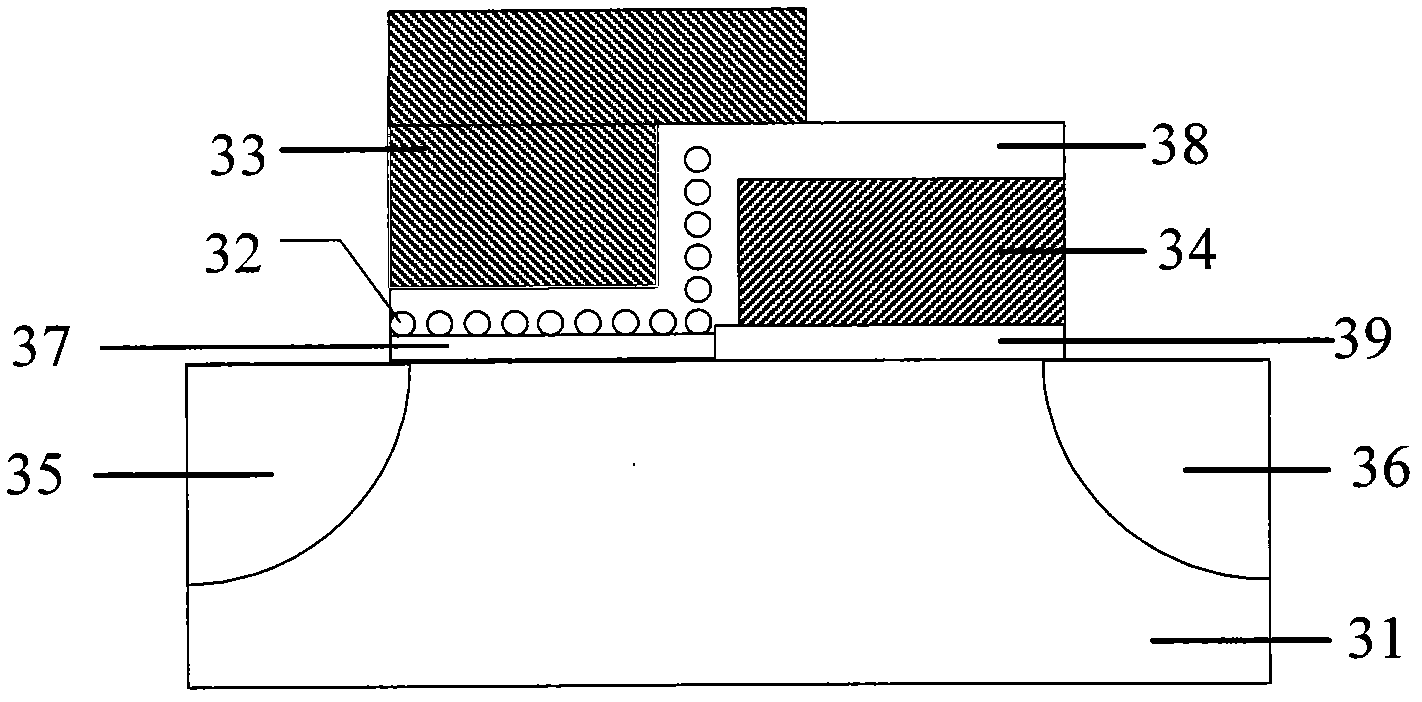

[0039] In this preferred embodiment, the core storage unit of the dedicated EEPROM memory chip for smart energy meters is a 2T storage unit formed by a single planar floating gate nanocrystalline storage transistor and a selection transistor in series, and a high-density storage unit is formed based on the 2T storage unit Storage array. Reference Figure 4-3 , Shows a schematic diagram of the nanocrystalline memory cell structure of the third embodiment of the EEPROM memory chip dedicated for smart energy meters of the present invention, including: a semiconductor substrate material 41, a source conductive region formed by heavily doping the substrate area of the substrate material 41 45 and the first drain conductive region 46-1, the second drain conductive region 46-2, the tunneling dielectric layer 47 covering the carrier channel between the source conductive region 45 and the first drain conductive region 46-1, tunneling The nanocrystalline memory layer 42 covered on the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More