TSV (through silicon via) high-frequency three-dimensional integrated interconnection structure based on SOI (silicon on insulator)

An interconnect structure and three-dimensional technology, applied in the field of microelectronics, can solve the problems of reducing device reliability, reducing economic efficiency, and serious leakage loss, etc., and achieve the effects of reducing noise coupling crosstalk, improving transmission quality, and reducing leakage loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

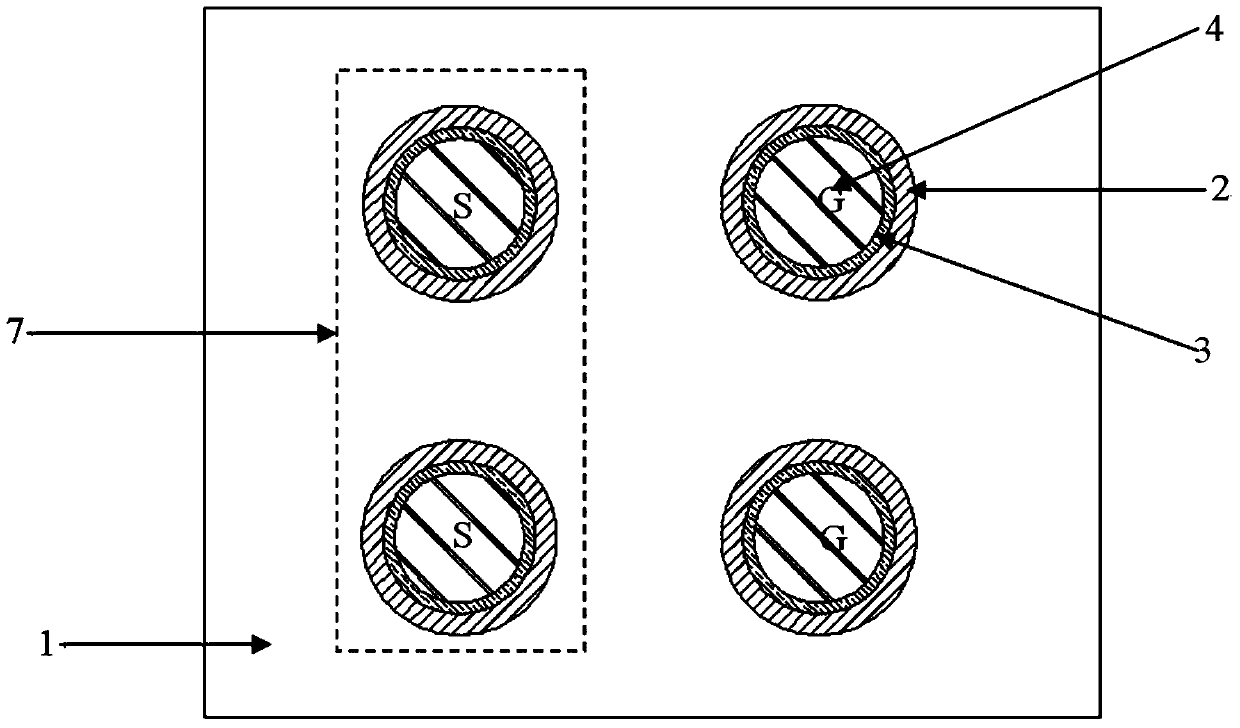

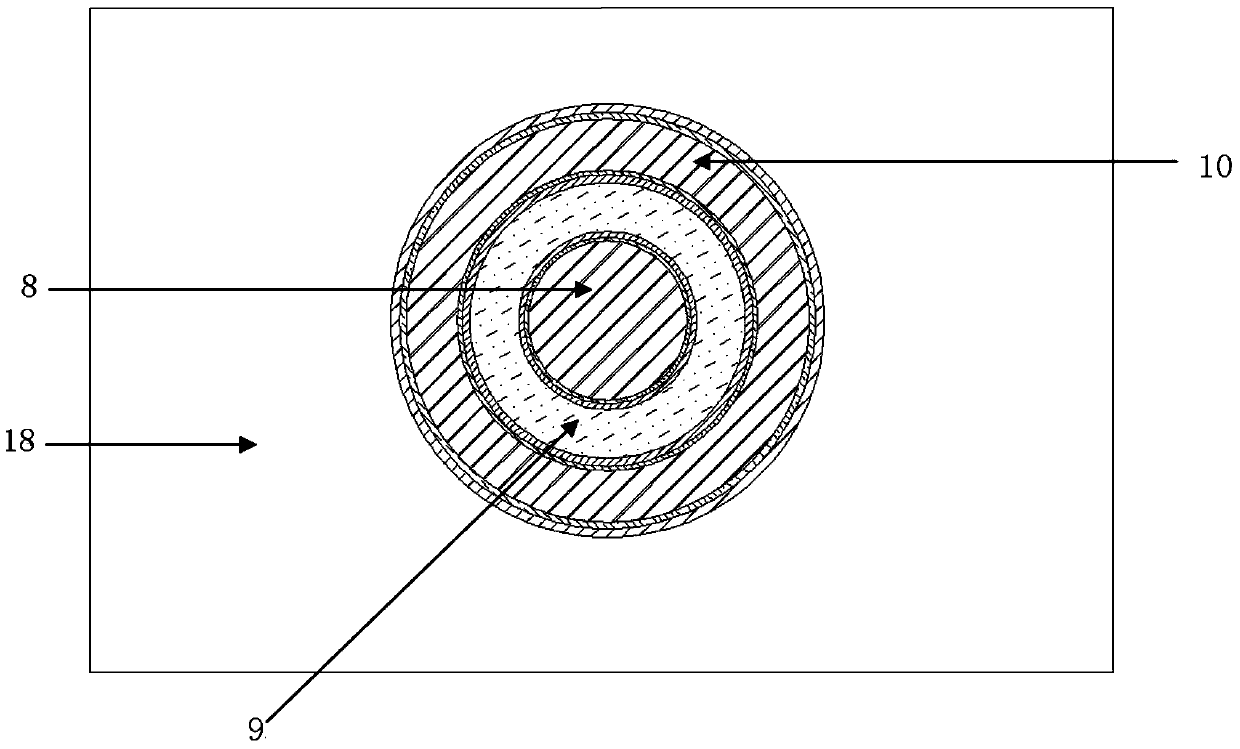

[0017] Such as image 3 As shown, the TSV three-dimensional integrated interconnection structure is based on the SOI substrate 18, the substrate type is P-type silicon, the internal TSV through hole is cylindrical, the external TSV through hole is circular, and the filling between the two is BCB (benzo ring butene resin) fill layer 9.

[0018] Such as Figure 4 As shown, the thickness of the top layer silicon 11 of the SOI substrate 18 is The thickness of the buried oxide layer 12 is The underlying silicon 13 has a thickness of 80 μm. The diameter W1 of the inner cylindrical TSV copper pillar 8 is 15 μm, the thickness D1 of the inner cylindrical TSV through-hole insulation layer 16 is 0.5 μm, the thickness of the inner cylindrical TSV through-hole barrier layer TaN and copper seed layer 17 is 0.4 μm, and the thickness of the TaN layer is D2 is 0.2 μm, and the thickness D3 of the copper seed layer is 0.2 μm. The thickness W2 of the outer annular TSV copper pillar 10 is 6...

Embodiment 2

[0021] Such as image 3 As shown, the TSV three-dimensional integrated interconnection structure is based on the SOI substrate 18, the substrate type is N-type silicon, the internal TSV via hole is cylindrical, the external TSV via hole is annular, and the filling between the two is BCB (benzo ring butene resin) fill layer 9.

[0022] Such as Figure 4 As shown, the thickness of the top layer silicon 11 of the SOI substrate 18 is The thickness of the buried oxide layer 12 is The underlying silicon 13 has a thickness of 100 μm. The diameter W1 of the inner cylindrical TSV copper pillar 8 is 20 μm, the thickness D1 of the inner cylindrical TSV through-hole insulation layer 16 is 0.5 μm, the thickness of the inner cylindrical TSV through-hole barrier layer TaN and copper seed layer 17 is 0.4 μm, and the thickness of the TaN layer is D2 is 0.2 μm, and the thickness D3 of the copper seed layer is 0.2 μm. The thickness W2 of the outer annular TSV copper pillar 10 is 7 μm, the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More