Semiconductor packaging method of wafer level silicon-based through hole

A packaging method and a technology of through-silicon vias, which are applied in semiconductor devices, semiconductor/solid-state device manufacturing, and electrical solid-state devices, etc., can solve problems such as easy generation of fragments, slivers, accelerated device failure, and affect product reliability, etc., to reduce challenges , Reduce the overall size and realize the effect of miniaturization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be described in more detail below with reference to accompanying drawing:

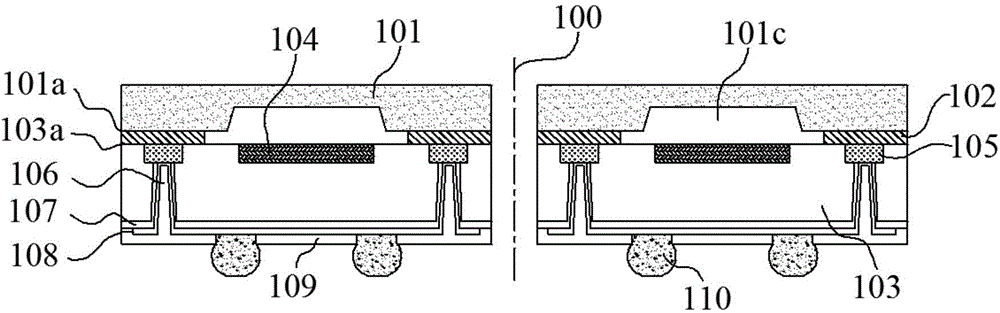

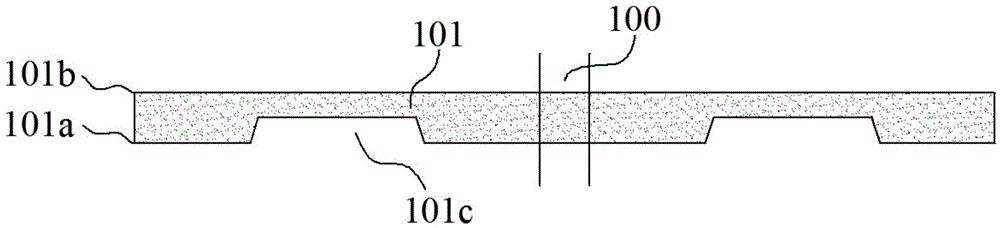

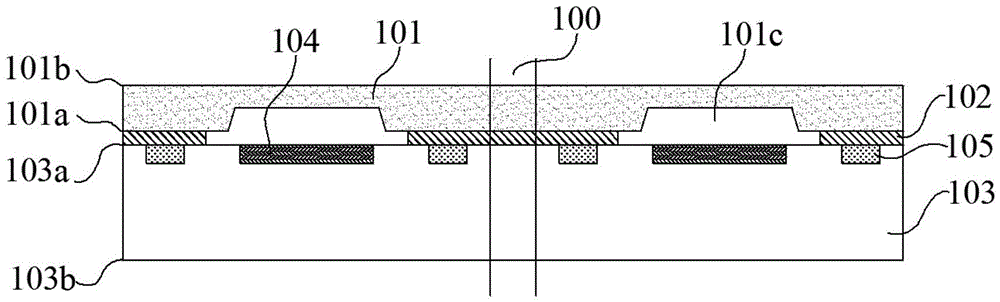

[0037] by figure 1As shown, the wafer-level semiconductor package containing through-silicon vias according to the embodiment of the present invention includes: 1. a cover plate 101, and a cavity structure 101c is fabricated on the front surface 101a of the cover plate; 2. a wafer 103, which includes a wafer Circular front 103a and wafer back 103b; 3. functional area 104 and bonding pads 105, a plurality of chip areas are prefabricated on the wafer front 103a, each chip area includes a central functional area 104 and several bonding pads 105 around ; 4. Bonding glue 102, by coating a layer of bonding glue 102 on the front surface 101a of the cover plate, bonding the front surface 101a of the cover plate with the front surface 103a of the wafer; 103b making through-silicon vias 106 to expose the pads 105 for connection to the subsequent redistribution circuit layer; 6....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More