Preparation method of semiconductor device

A semiconductor and device technology, which is applied in the field of semiconductor device preparation, can solve the problems of increased production cost and complicated process flow, and achieve the effects of low cost, simplified silicon oxide filling, and improved alignment accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments, but not as a limitation of the present invention.

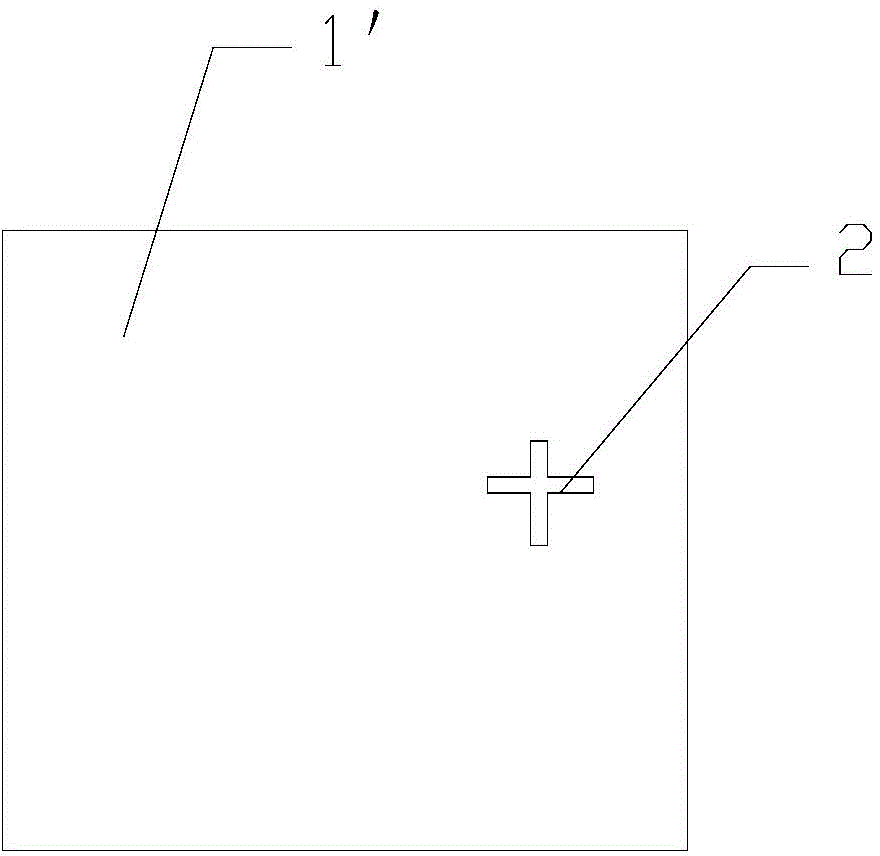

[0029] Figure 1-4 is a schematic flow chart of a method for preparing a semiconductor device in an embodiment of the present invention; as Figure 1-4 Shown:

[0030] This embodiment relates to a method for preparing a semiconductor device, which can be applied to the preparation process of a CMOS image sensor (CIS), and specifically includes the following steps:

[0031] Step S1, provide a semiconductor substrate 1, in the embodiment of the present invention, the semiconductor substrate 1 is a silicon wafer, such as figure 1 structure shown.

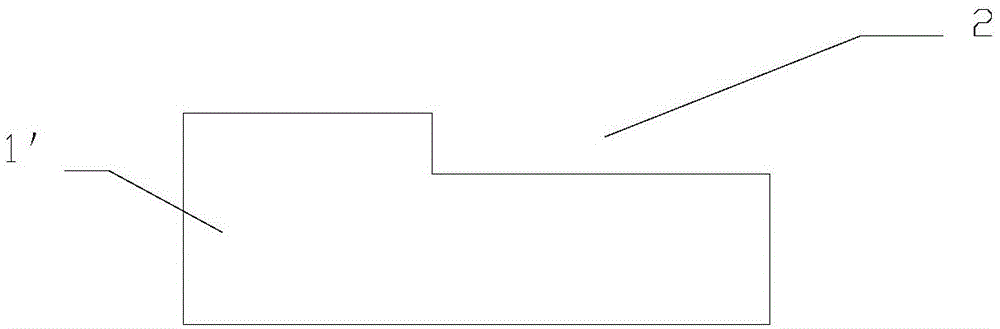

[0032] Step S2, etching a zero-layer alignment mark (AlignmentMark) 2 on the upper surface of the semiconductor substrate 1. In an embodiment of the present invention, the step of etching the zero-layer alignment mark 2 is specifically, spin coating A...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More