Full back electrode contact crystalline silicon solar cell structure and preparation method thereof

A full-back electrode contact and solar cell technology, applied in the field of solar cells, can solve the problems of high material cost, recombination loss, and resistance loss, etc., and achieve the effects of reducing the amount of silver electrodes used, reducing recombination loss, and improving conversion efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

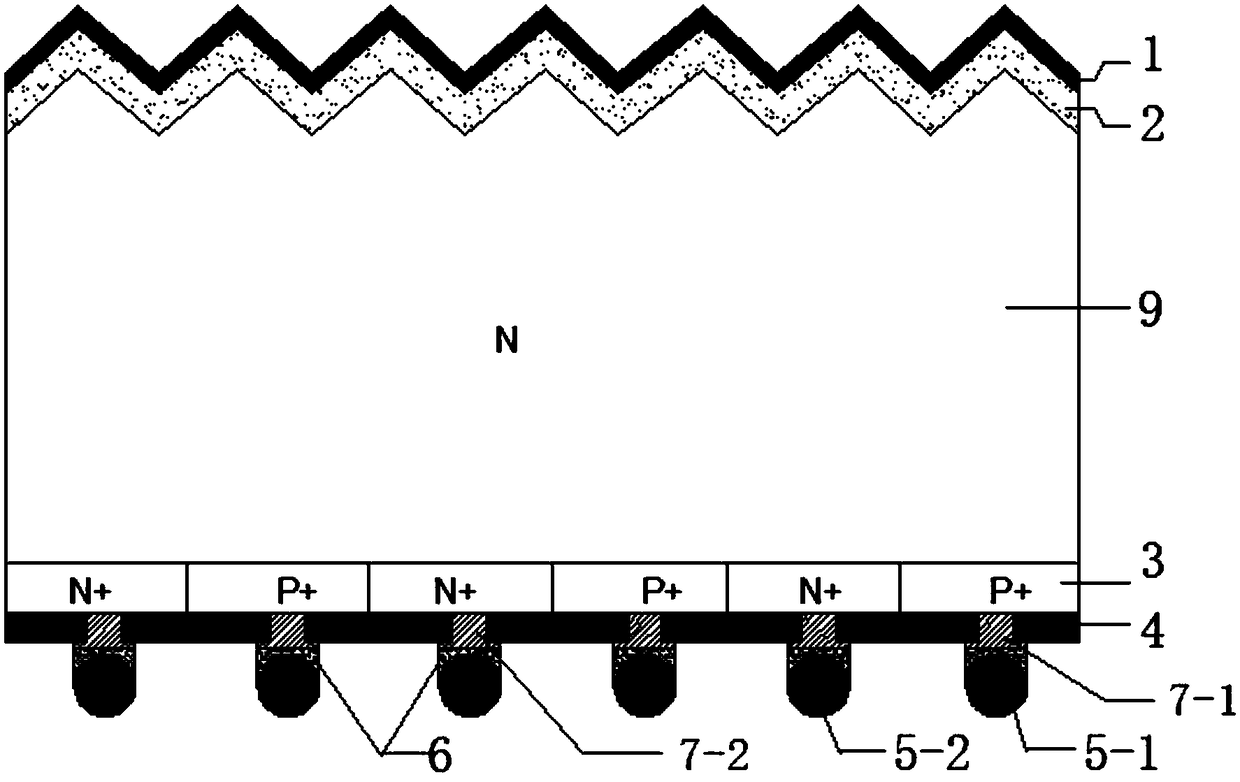

Embodiment 1

[0055] (1) The N-type monocrystalline silicon wafer is anisotropically etched in a KOH solution at about 80°C to obtain a pyramid structure on the surface.

[0056] (2) Print a boron-containing interdigitated diffusion mask layer on the back of the silicon wafer, and then perform phosphorus-doped thermal diffusion at about 750-850°C. The boron on the mask layer enters the silicon substrate after diffusion to form a P-type The doped layer, and the area where the mask layer is not printed, forms an N-type doped layer after phosphorus is diffused. The width of a single P-type doped strip region on the back is 500um, and the square resistance is 70Ω / □; the width of a single N-type doped strip region on the back is 300um, and the square resistance is 70Ω / □. This process simultaneously forms a 100Ω / □ N+ doped layer on the front side of the silicon wafer.

[0057] (3) The phosphosilicate glass and borosilicate glass on the front and back are removed by wet etching.

[0058] (4) Dep...

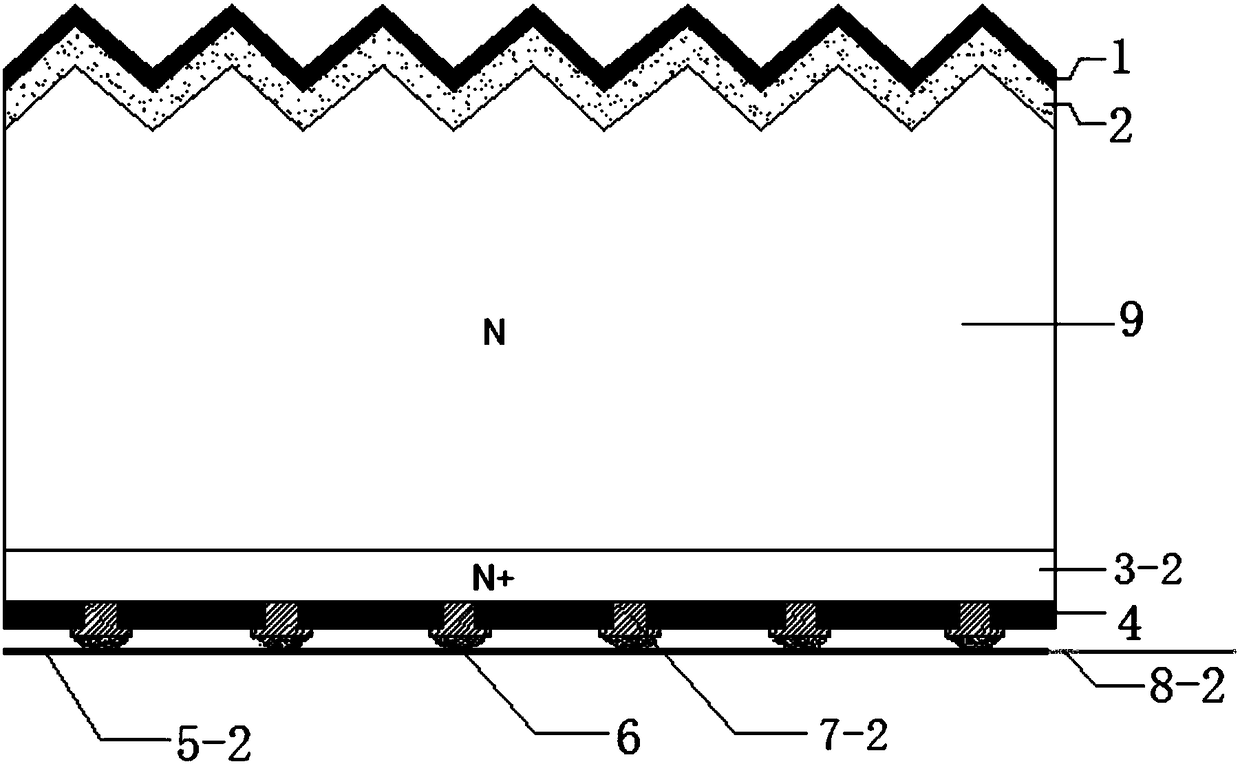

Embodiment 2

[0066] (1) The N-type monocrystalline silicon wafer is anisotropically etched in a KOH solution at about 80°C to obtain a pyramid structure on the surface.

[0067] (2) On the back of the silicon wafer, ion implantation is used to form finger-shaped alternately distributed P-type doped layers and N-type doped layers. The width of a single P-type doped strip region on the back is 1mm, and the square resistance is 50Ω / □ ; The width of a single N-type doped strip region on the back is 0.5mm, and the square resistance is 50Ω / □. An 80Ω / □ N+ doped layer is prepared on the front side of the silicon wafer by ion implantation.

[0068] (3) Perform annealing treatment on the silicon wafer after ion implantation.

[0069] (4) Carry out chemical cleaning to silicon chip.

[0070] (5) Deposit 90 nm of silicon oxide on the front side of the silicon wafer, and deposit 30 nm of silicon oxide on the back side.

[0071] (6) The method of steel plate printing is used to make an array of local...

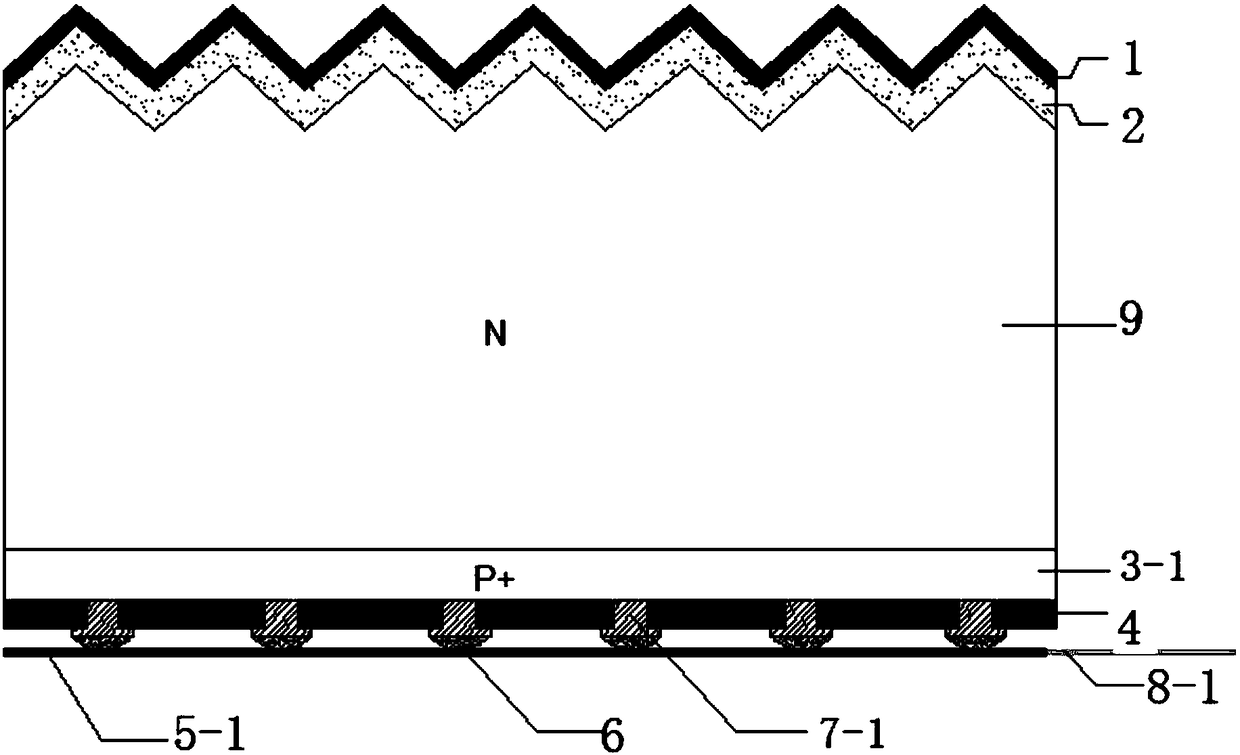

Embodiment 3

[0078] (1) The N-type monocrystalline silicon wafer is anisotropically etched in a KOH solution at about 80°C to obtain a pyramid structure on the surface.

[0079] (2) Print a boron-containing interdigitated diffusion mask layer on the back of the silicon wafer, and then perform thermal diffusion at about 750-950°C. The boron on the mask layer enters the silicon substrate after diffusion to form P-type doping layer, and the area where the mask layer is not printed, forms an N-type doped layer after phosphorus is diffused, and the P and N-doped layers are alternately arranged on the back of the silicon wafer. The width of the single P-doped strip region on the back is 2mm, and the square resistance is 60Ω / □; the width of the single N-doped strip region on the back is 1mm, and the square resistance is 60Ω / □. This process simultaneously forms a 90Ω / □ N+ doped layer on the front side of the silicon wafer.

[0080] (3) The phosphosilicate glass and borosilicate glass on the front a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More