Fabrication method for wafer-level mono-axial strain Si on AlN-buried insulation layer based on non-crystallization and scale effect

A uniaxial strain technology on an insulating layer, applied in the field of microelectronics, can solve the problems of non-adjustment, easy breakage, high cost, avoid damage and defects, improve insulation and heat dissipation, and improve material performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

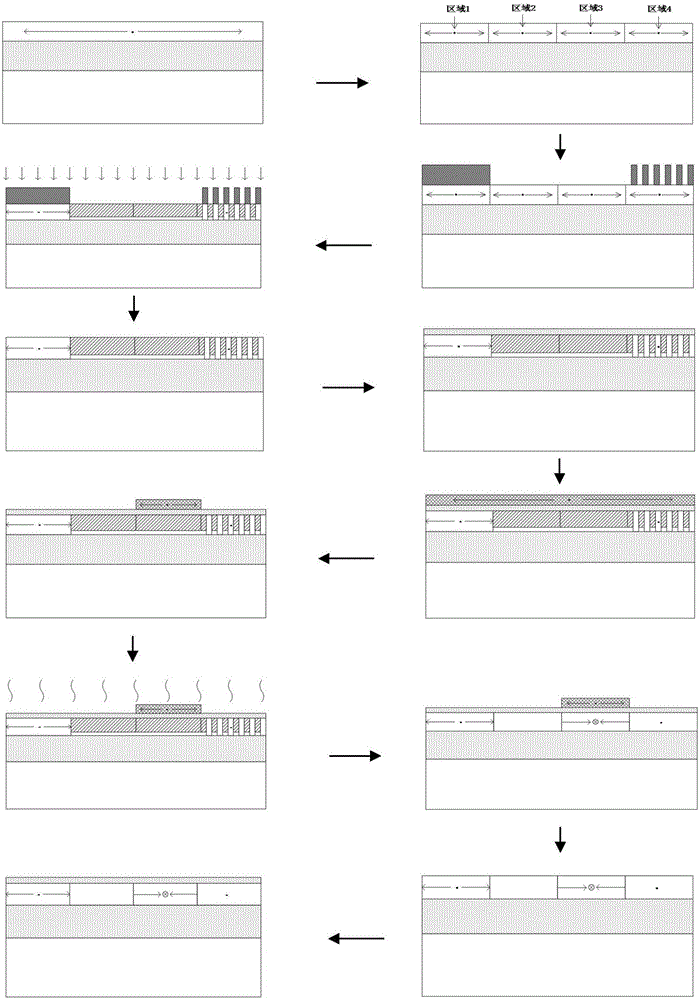

[0051] Example 1, making a wafer-level uniaxial tensile-strained Si material on a 5-inch AlN buried insulating layer.

[0052] Step 1: Select a 5-inch Si wafer on an AlN-buried insulating layer and clean it.

[0053] (1a) Use acetone and isopropanol to alternately perform ultrasonic cleaning on the Si wafer on the selected AlN buried insulating layer to remove organic contamination on the substrate surface;

[0054] (1b) Prepare a mixed solution of ammonia water, hydrogen peroxide, and deionized water in a ratio of 1:1:3, heat to 120°C, soak the Si wafer on the AlN-buried insulating layer in the mixed solution for 12 minutes, take it out and use Rinse with a large amount of deionized water to remove inorganic pollutants on the surface of the Si wafer on the AlN buried insulating layer;

[0055] (1c) Soak the Si wafer on the AlN buried insulating layer with HF acid buffer for 2 minutes to remove the oxide layer on the surface.

[0056] Step 2: Deposit SiO 2 Layer 4, such as ...

Embodiment 2

[0083] Example 2, manufacturing a wafer-level uniaxial tensile strained Si material on a 6-inch AlN buried insulating layer.

[0084] Step 1: Select a 6-inch Si wafer on an AlN-buried insulating layer and clean it.

[0085] The implementation of this step is the same as step 1 of Embodiment 1.

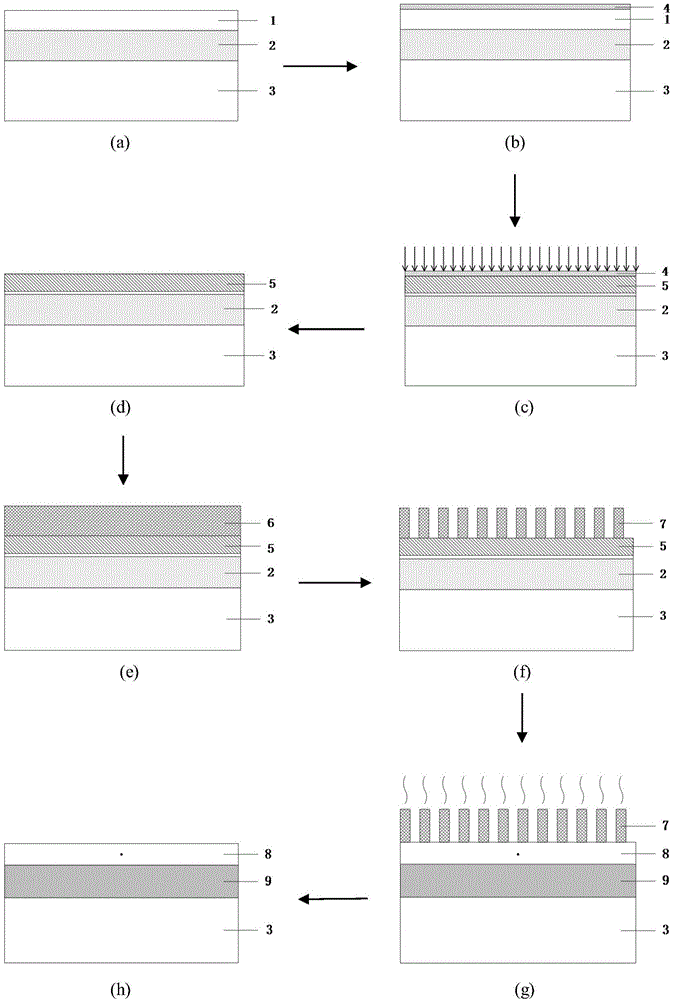

[0086] Step 2: Take out the Si wafer on the AlN buried insulating layer after cleaning, and deposit SiO on the top Si layer 1 by plasma-enhanced chemical vapor deposition PECVD process 2 layer, that is, the SiH 4 The flow rate is 45sccm, N 2 O flow is 164sccm, N 2 The flow rate is 800sccm, the gas pressure is 600mTorr, the power is 60W, and the deposition temperature is 300°C, and the SiO with a thickness of 16nm is deposited. 2 Layer 4, such as figure 2 (b) shown.

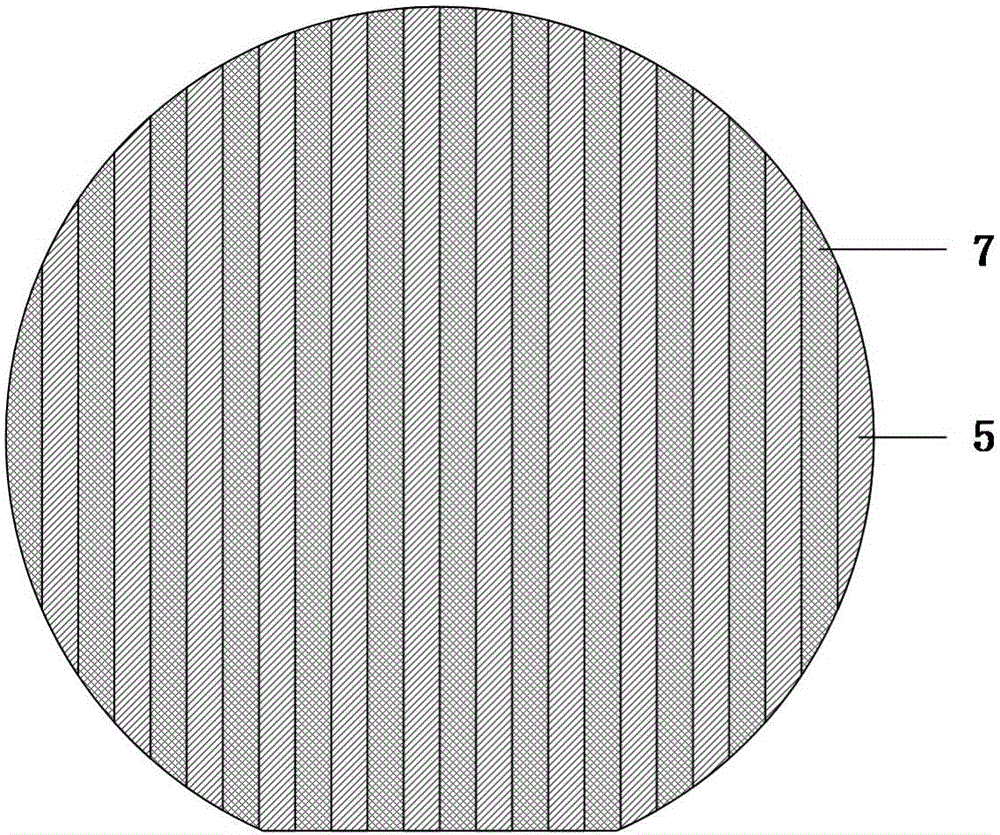

[0087] Step 3: Use an ion implanter to implant a dose of 3E15cm into the top Si layer 1 -2 , the energy is 60keV, Si ions to form an amorphous layer 5 inside the top Si layer 1, such as figure 2 (c) shown.

[0088...

Embodiment 3

[0098] Example 3, fabricating a wafer-level uniaxial compressively strained Si material on an 8-inch AlN buried insulating layer.

[0099] Step A: select an 8-inch Si wafer on an AlN buried insulating layer, and clean it.

[0100] The implementation of this step is the same as step 1 of Embodiment 1.

[0101] Step B: Deposit SiO 2 Layer 4, such as figure 2 (b) shown.

[0102] Take out the Si wafer on the AlN buried insulating layer after cleaning, and deposit SiO with a thickness of 25 nm on the top Si layer 1 by plasma enhanced chemical vapor deposition PECVD process. 2 Layer 4, prevents "channeling" from occurring, such as figure 2 (b) shown.

[0103] The deposition process is as follows: SiH 4 The flow rate is 45sccm, N 2 O flow is 164sccm, N 2 The flow rate is 800 sccm, the gas pressure is 600 mTorr, the power is 60 W, and the deposition temperature is 300° C.

[0104] Step C: forming an amorphized layer 5, such as figure 2 (c) shown.

[0105] Form SiO 2 Aft...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More