Low-power fin type field effect transistor and manufacturing method thereof

A fin field effect, low-power technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as large edge roughness, device characteristic consistency degradation, channel mobility degradation, etc. Achieve the effect of small leakage current, low cost and high on-state current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0080] The present invention will be described in detail below in conjunction with the accompanying drawings and specific examples.

[0081] A low-power N-type fin field-effect transistor with a fin-type isolation structure prepared on an SOI substrate can be realized according to the following steps:

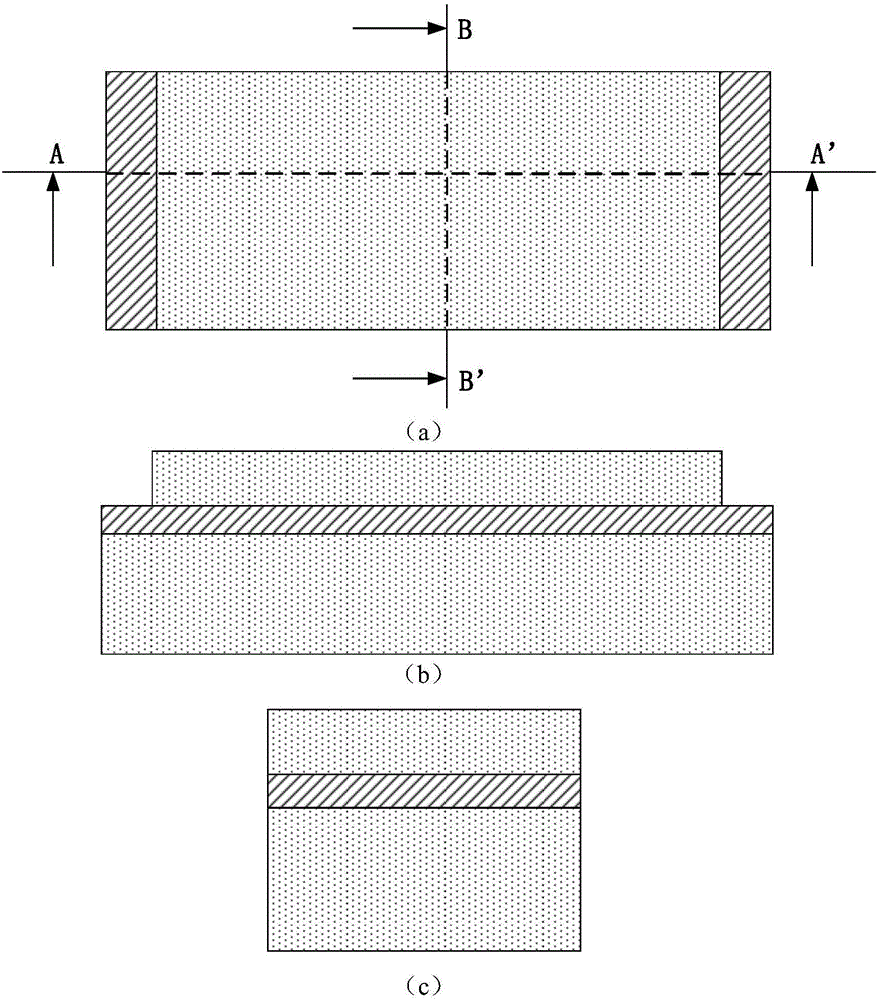

[0082] 1) On the P-type (100) SOI substrate, the HNA solution is used to thin the top silicon film to 250nm, and the active area of the device is formed by photolithography and RIE etching, and the glue is removed, such as figure 1 shown;

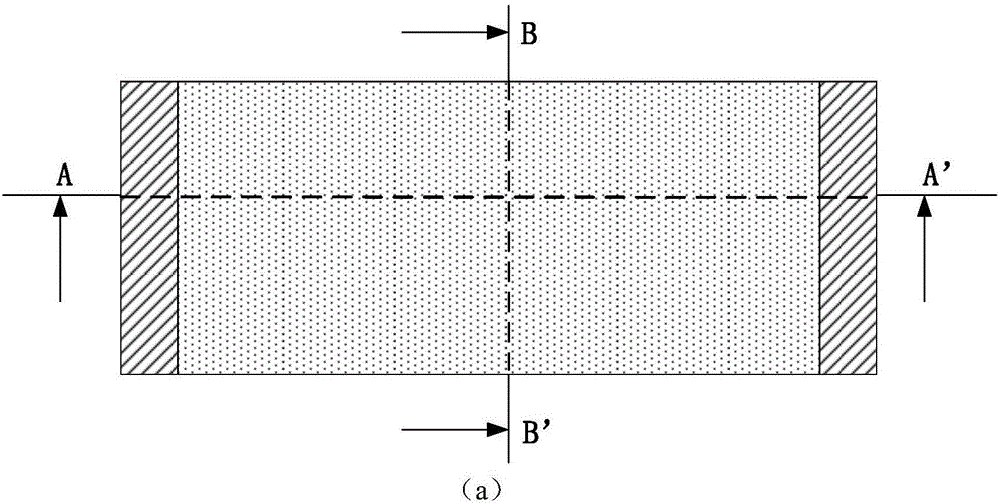

[0083] 2) LPCVD SiO 2 300nm, the surface is planarized by chemical mechanical polishing to expose the upper surface of the active region and form STI, such as figure 2 shown;

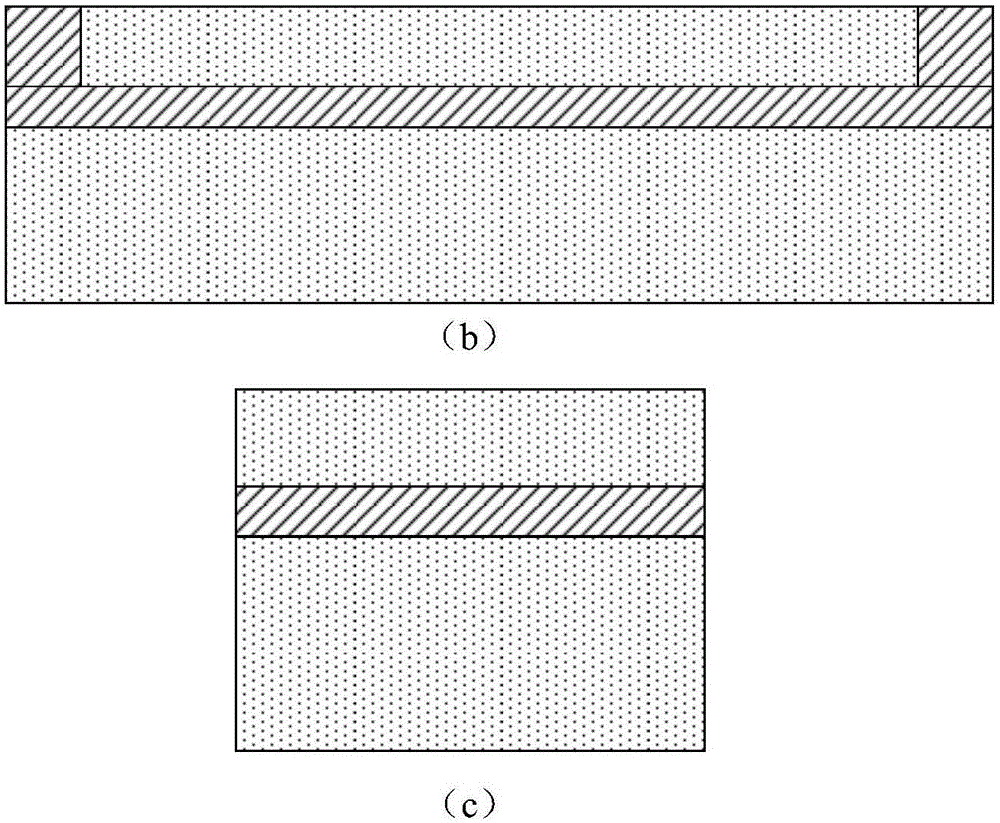

[0084] 3) LPCVD 200nm silicon oxide is used as the mask layer 1, and the pattern window of the fin-shaped spacer bar with a length of 100nm and a width of 30nm is defined by electron beam lithography, and the mask layer 1 and the mask layer 1 are anisotropical...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More