Fabrication method of grooved vertical double diffusion metal oxide semiconductor (VDMOS)

A manufacturing method and trench-type technology, which are applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem that trench-type VDMOS cannot work normally, weaken the driving ability of trench-type VDMOS, and reduce trench-type VDMOS cells. Density reduction, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

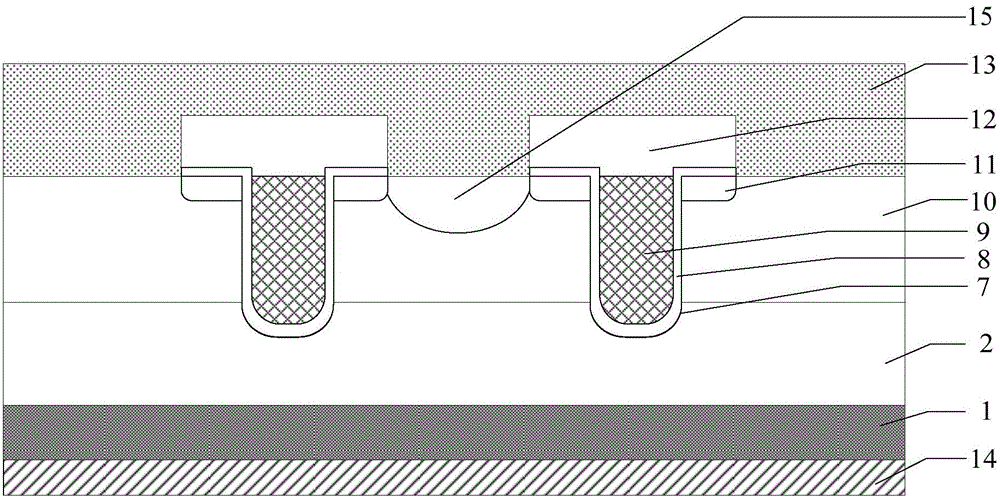

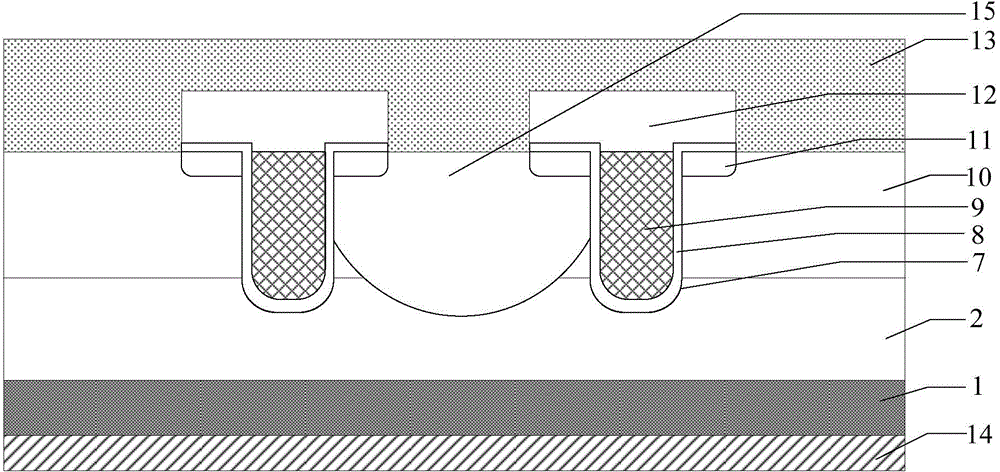

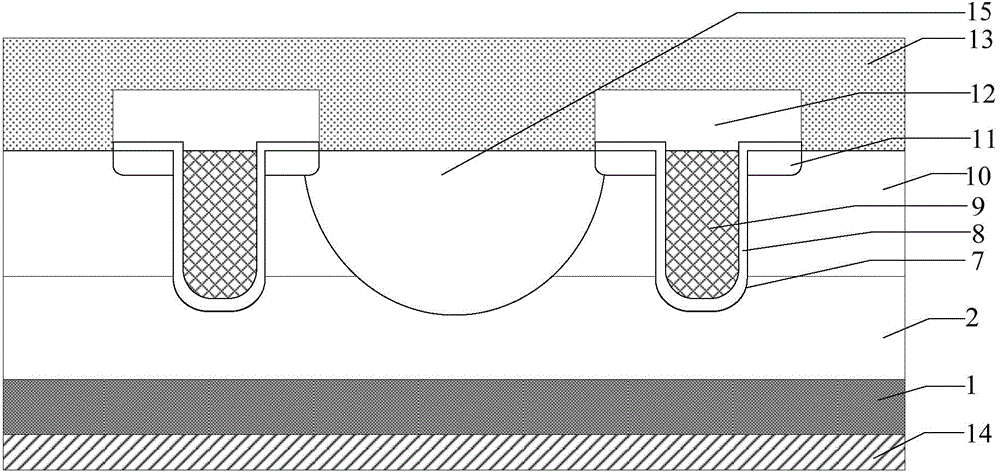

[0058] Figure 4 It is a flow chart of Embodiment 1 of the trench VDMOS manufacturing method of the present invention, such as Figure 4 As shown, the trench VDMOS manufacturing method provided in this embodiment includes:

[0059] Step 101 , depositing a hard mask layer 3 on the N-type epitaxial layer 2 .

[0060] In this embodiment, the N-type epitaxial layer 2 is grown on the N-type substrate 1 . Wherein, the N-type substrate 1 is a heavily doped N-type substrate, and the N-type epitaxial layer 2 is a lightly doped N-type epitaxial layer. The specific doping concentration of the N-type substrate 1 and the doping concentration of the N-type epitaxial layer 2 are the same as those in the prior art, and will not be repeated here.

[0061] In this embodiment, the hard mask layer 3 deposited on the N-type epitaxial layer 2 may be a silicon dioxide layer. The deposition process may be low pressure chemical vapor deposition. The deposited hard mask layer may have a thickness ...

Embodiment 2

[0095] Figure 18 It is the first flow chart of Embodiment 2 of the trench type VDMOS manufacturing method of the present invention, as Figure 18 As shown, the trench VDMOS manufacturing method provided in this embodiment includes:

[0096] Step 201 , depositing a hard mask layer 3 on the N-type epitaxial layer 2 .

[0097] Step 202 , performing photolithography and etching on the middle region of the hard mask layer 3 to form the first trench window region 4 .

[0098] Step 203 , etching the lower side region of the first trench window region 4 to form a first trench 5 in the N-type epitaxial layer.

[0099] Step 204 , growing P-type epitaxy 6 on the upper surface of the hard mask layer 3 , in the first trench window region 4 and the first trench 5 .

[0100] Step 205, using a chemical mechanical polishing process to remove the P-type epitaxy 6 on the upper surface of the hard mask layer 3, the P-type epitaxy 6 in the hard mask layer 3 and the first trench window region 4...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More