Preparation method for GaAs/Ge/GaAs heterogeneous SPiN diode applied to annular antenna

A loop antenna and diode technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of large injection dose and energy, affecting concentration, and incompatibility, so as to suppress the impact and improve the breakdown voltage Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

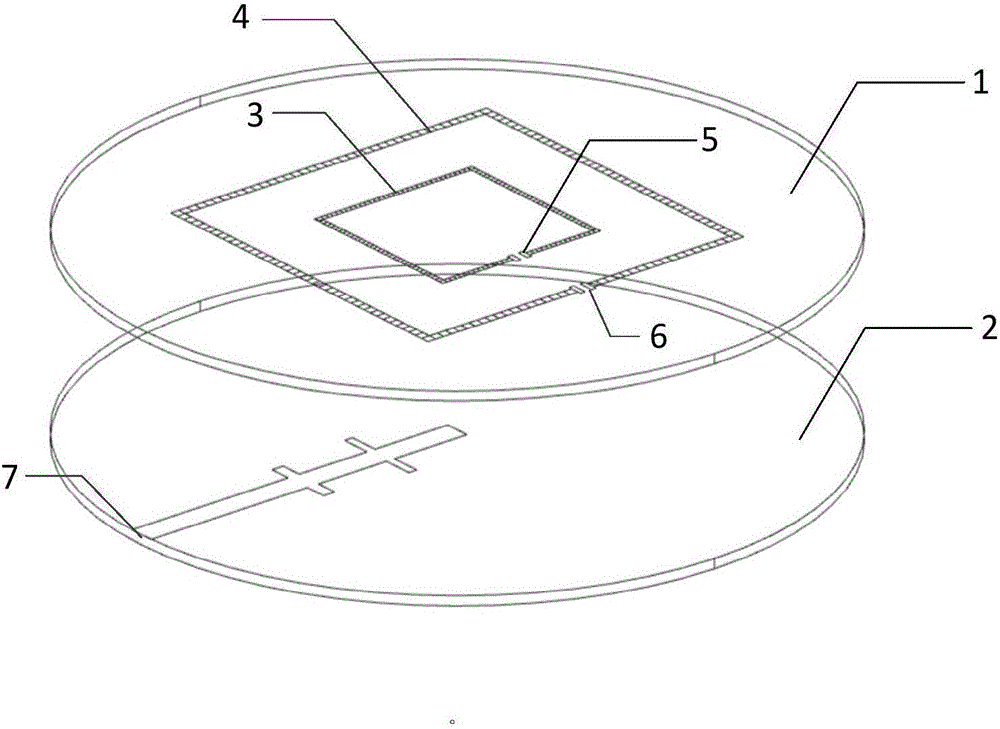

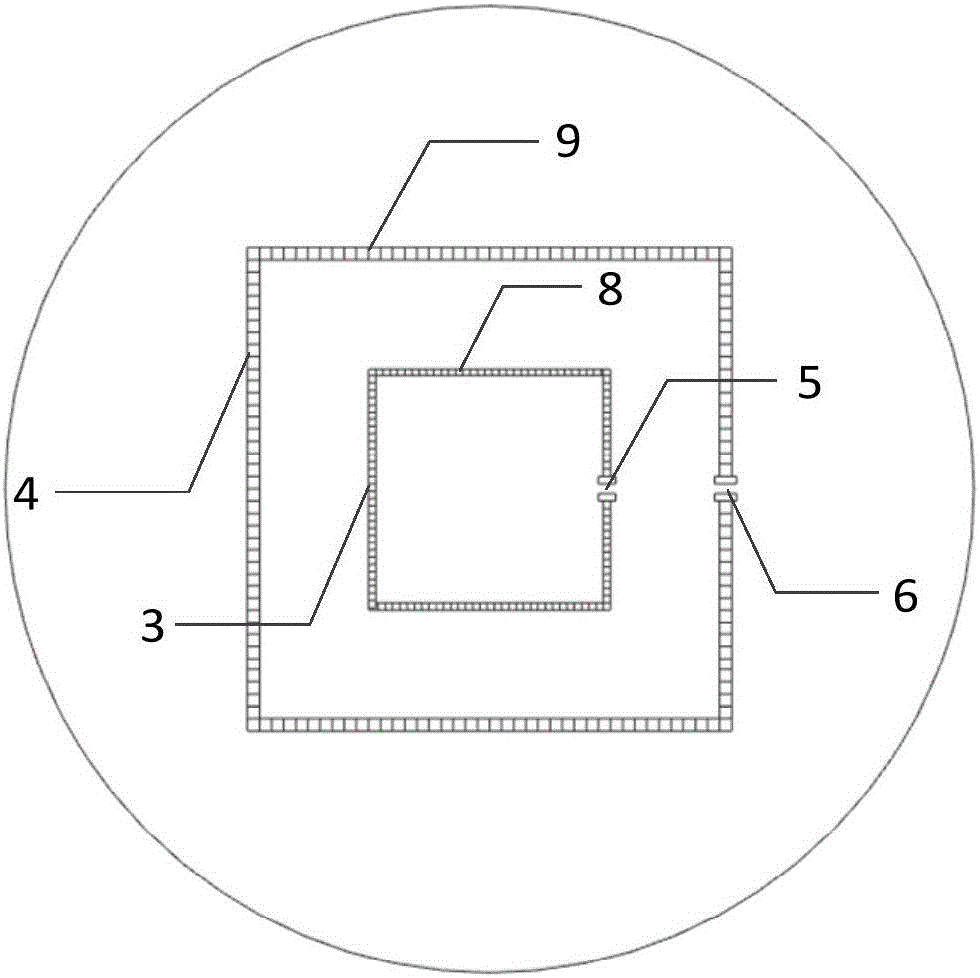

[0057] An embodiment of the present invention provides a method for manufacturing a GaAs / Ge / GaAs heterogeneous SPiN diode used for a loop antenna, and the GaAs / Ge / GaAs heterogeneous SPiN diode is used for making a reconfigurable loop antenna. Please refer to figure 1 , figure 1 It is a structural schematic diagram of a reconfigurable loop antenna according to an embodiment of the present invention; the loop antenna includes: a semiconductor substrate (1); a dielectric plate (2); a first SPIN diode ring (3), a second SPIN diode ring (4), the first DC bias line (5) and the second DC bias line (6) are all arranged on the semiconductor substrate (1); the coupled feed source (7) is arranged on the On the dielectric plate (2); the first SPIN diode ring (3), the second SPIN diode ring (4), the first DC bias line (5) and the second DC bias line (6) Manufactured on the semiconductor substrate (1) using a semiconductor process.

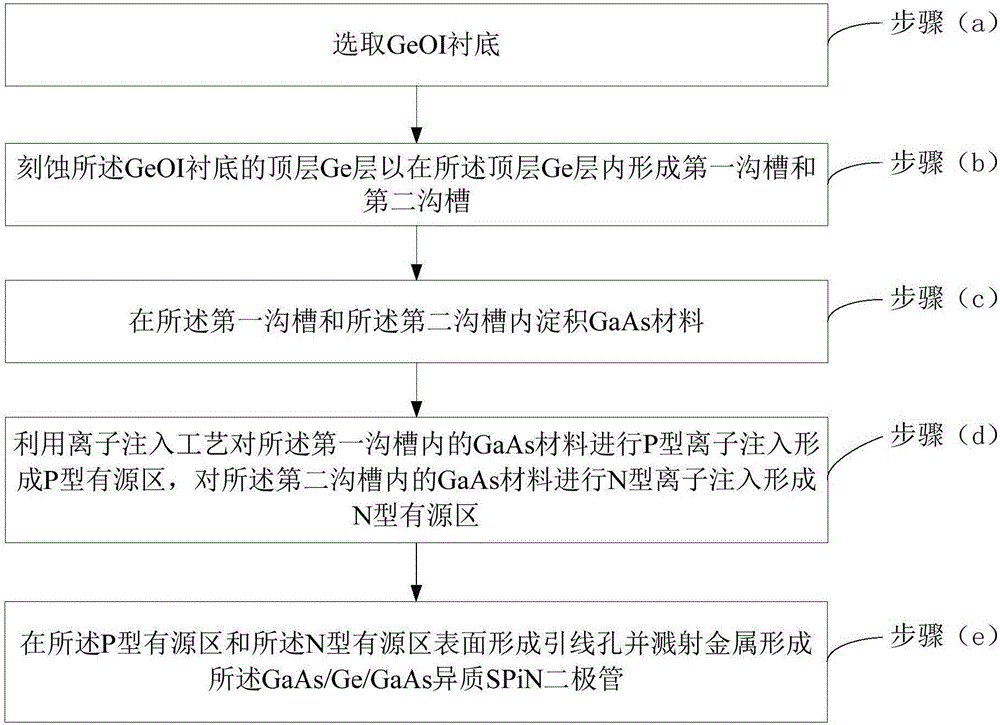

[0058] Please refer to figure 2 , figure 2 It is a...

Embodiment 2

[0098] See Figure 7a-Figure 7r , Figure 7a-Figure 7r It is a schematic diagram of a preparation method of a GaAs / Ge / GaAs heterostructure SPIN diode according to an embodiment of the present invention. On the basis of the above-mentioned embodiment 1, to prepare a channel length of 22nm (the length of the solid-state plasma region is 100 microns) The GaAs / Ge / GaAs heterostructure SPIN diode is taken as an example to describe in detail, and the specific steps are as follows:

[0099] Step 1, substrate material preparation steps:

[0100] (1a) if Figure 7a As shown, the (100) crystal orientation is selected, the doping type is p-type, and the doping concentration is 10 14 cm -3 A GeOI substrate sheet 101, the thickness of the top layer Ge is 50 μm;

[0101] (1b) if Figure 7b As shown, the method of chemical vapor deposition (Chemical vapor deposition, referred to as CVD) is used to deposit a layer of the first SiO with a thickness of 40nm on the GeOI substrate. 2 layer ...

Embodiment 3

[0129] Please refer to Figure 8 , Figure 8 It is a schematic diagram of a device structure of a heterogeneous Ge-based SPIN diode according to an embodiment of the present invention. The SPIN diode of the GaAs / Ge / GaAs heterostructure adopts the above-mentioned figure 2The preparation method shown is made, specifically, the SPIN diode of the GaAs / Ge / GaAs heterostructure is prepared and formed on the GeOI substrate 301, and the P region 304, the N region 305 of the SPIN diode and the lateral position of the P region 304 The i region (intrinsic region) between the N region 305 is located in the top layer Ge302 of the GeOI substrate. Wherein, the SPIN diode can be isolated by STI deep trenches, that is, an isolation trench 303 is provided outside the P region 304 and the N region 305, and the depth of the isolation trench 303 is greater than or equal to the thickness of the top Ge 302.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More