Wafer-level back gold chip packaging structure and packaging method thereof

A technology of packaging structure and packaging method, which is applied to electrical components, electrical solid devices, circuits, etc., can solve the problems of scrapping and short-circuit failure of the packaging body, and achieve the effects of low power loss, material cost saving, and easy operation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

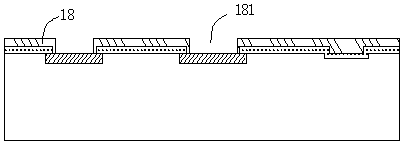

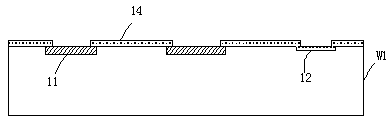

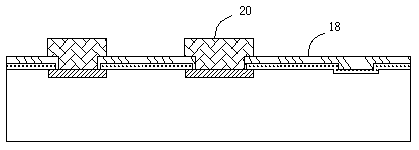

[0055] A packaging structure of a gold-backed chip of the present invention, such as figure 1 shown. The front side of the silicon base body 10 is provided with several chip electrodes 11 and functional sensing areas (not shown), the chip insulating layer 14 covers the silicon base body 10 and exposes the chip electrodes 11, and the chip insulating layer 14 covers the silicon base body The remainder of the scribe lane 12 of 10. The chip insulating layer 14 covers the remaining part of the scribe line 12 of the silicon base body 10 and extends outward to form a chip insulating layer extension 141 . The front protective layer 18 covers the chip insulation layer 14 and opens the front protective layer opening 181 to expose the chip electrode 11 again. The upper surface of the chip electrode 11 is provided with a metal bump 20 exposing the front protective layer 18. The metal bump 20 is made of copper or tin. , tin-silver alloy or Ni / Au, Ni / Pd / Au and other composite structures. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More