Wafer level hetero integrated high frequency system and production method thereof

A wafer-level, heterogeneous technology, applied in the field of microelectronics, can solve problems such as serious bonding loss and parasitic effects, unfavorable system miniaturization development, and lower overall system performance, so as to reduce the influence of parasitic effects and shorten internal The effect of interconnection and risk reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The present invention will be described in further detail below in conjunction with specific examples, but the embodiments of the present invention are not limited thereto.

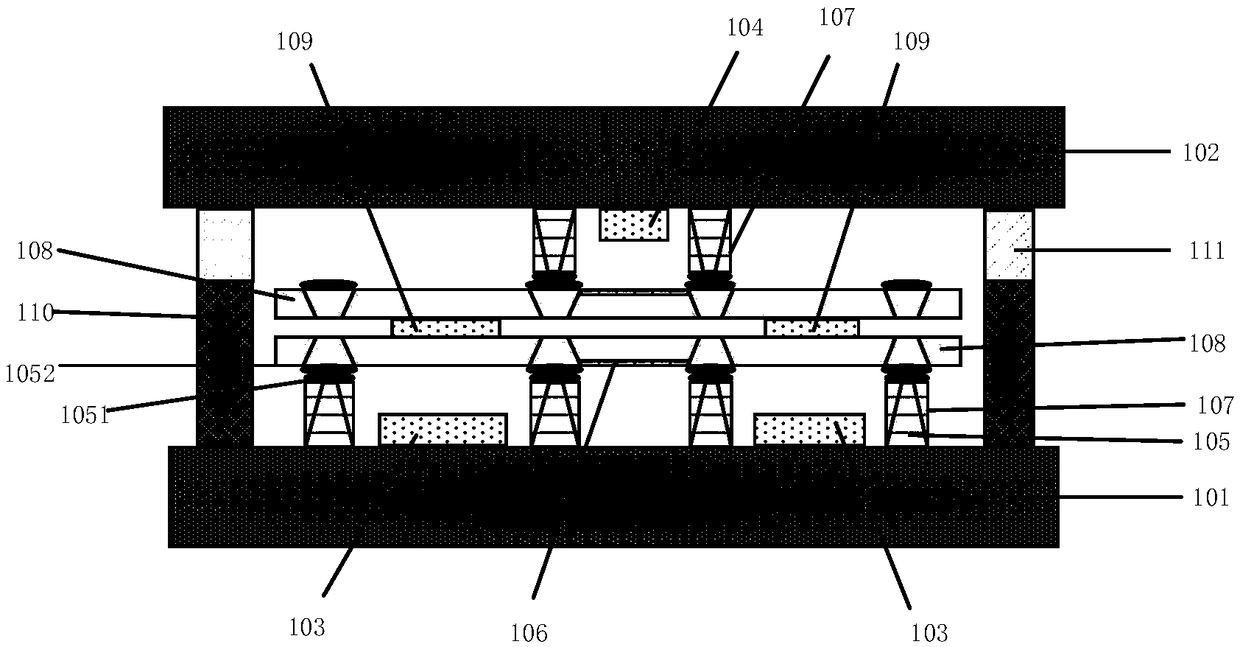

[0040] The present invention provides a wafer-level heterogeneous integrated high-frequency system, the structure of which is as follows figure 1 As shown, it includes at least a first substrate 101, a second substrate 102, an insulating bonding layer, and at least two chips arranged in different layers; wherein:

[0041] The second substrate 102, the insulating bonding layer, and at least two chips are arranged between the first substrate 101 and the second substrate 102, including a first chip 103 connected to the first substrate 101, and a second chip 104 connected to the second substrate 102;

[0042] The insulating bonding layer is provided with at least one through hole 105, and the side wall of the through hole 105 is coated with a conductive coating;

[0043] One of the at least two chips...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com