An enhanced high electron mobility transistor HEMT and a preparation method thereof

A high electron mobility, enhanced technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc. Power device development and other issues, to achieve the effect of maintaining current characteristics, reducing static power consumption, and high current characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

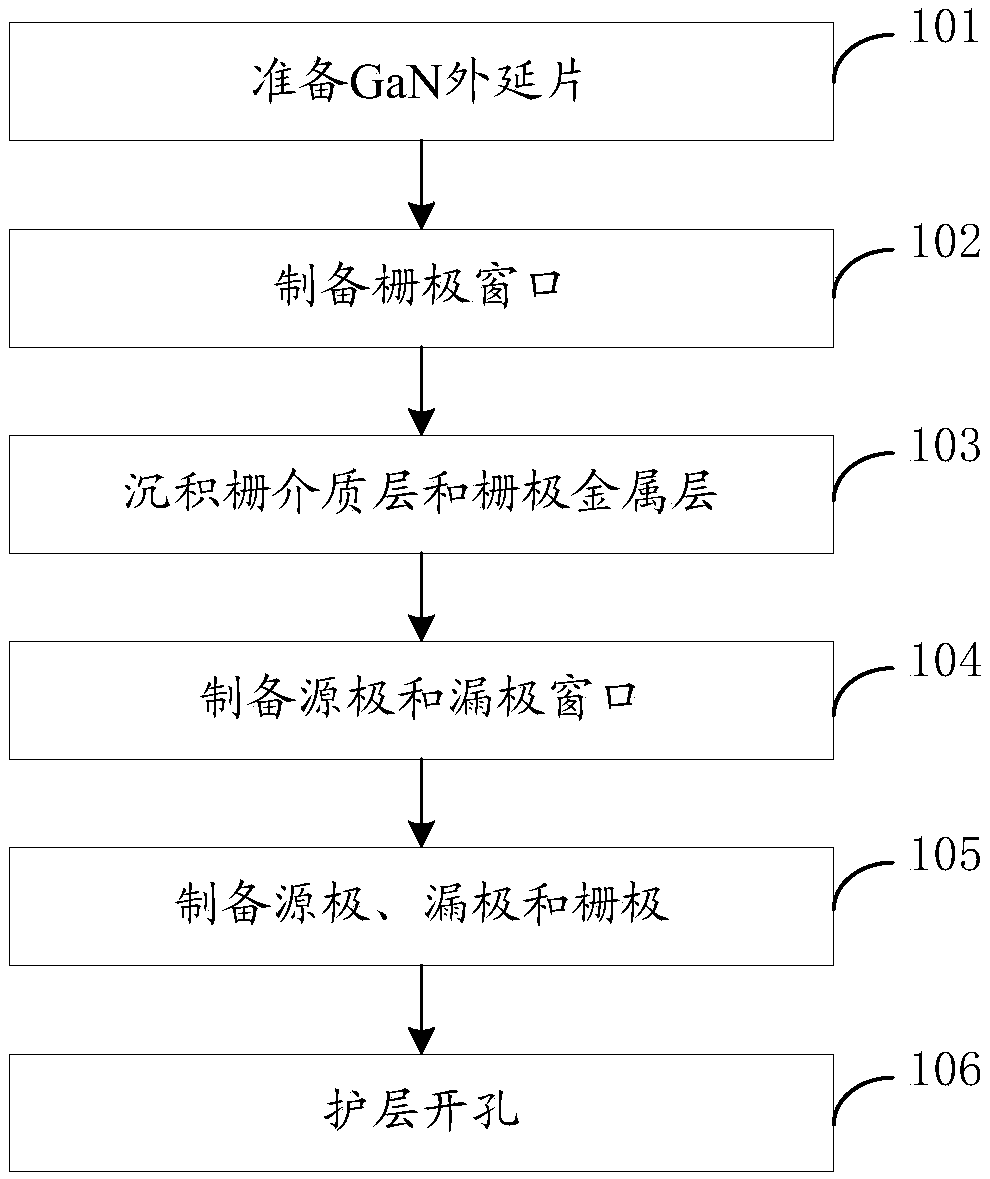

[0035] This embodiment takes M=4 as an example to illustrate the structure and preparation method of the enhanced HEMT, but it is not used to limit the present invention. In practical applications, M is an integer greater than or equal to 2, which can be based on the threshold voltage and current. Need to set the value of M.

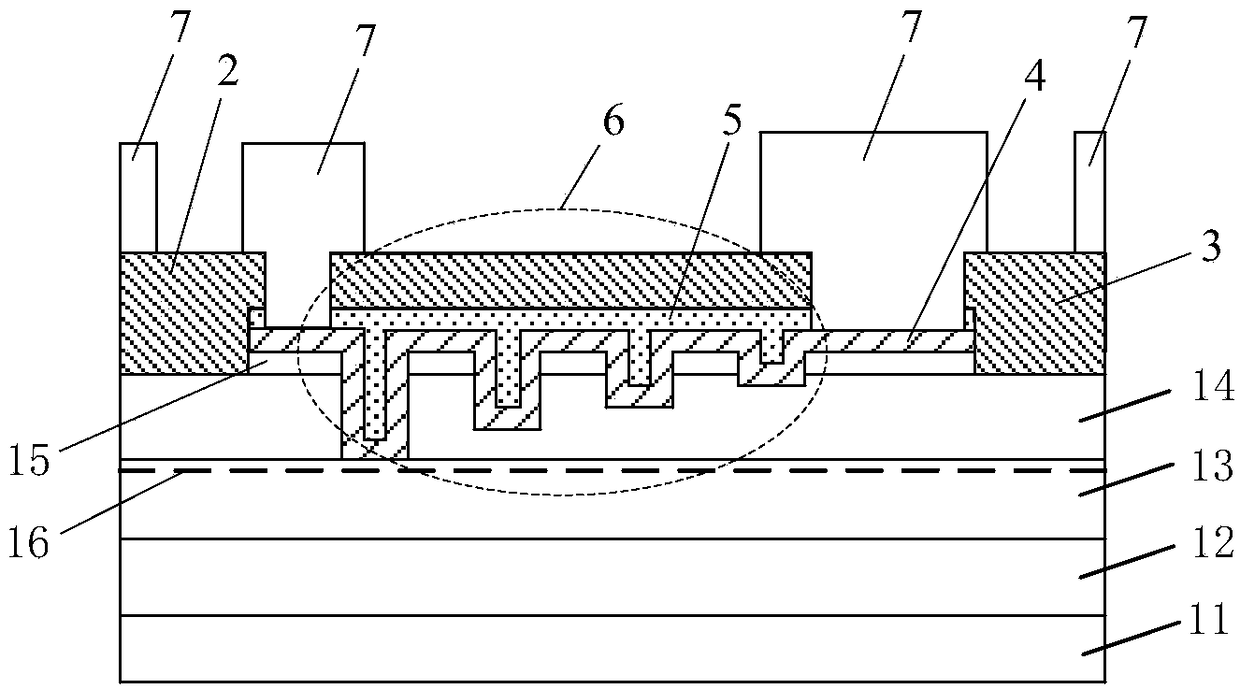

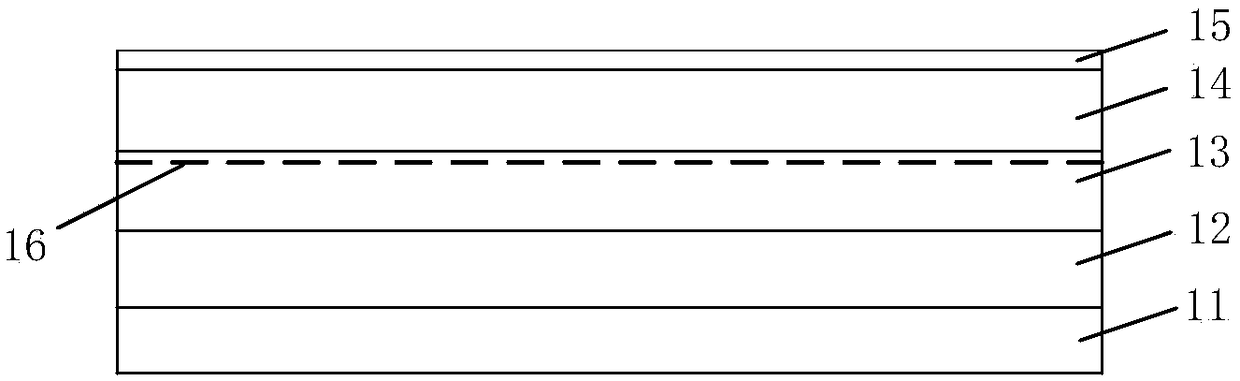

[0036] Please refer to figure 1 , figure 1 It is a schematic structural diagram of an enhanced HEMT in an embodiment of the present invention, such as figure 1 As shown, the enhanced HEMT includes a GaN epitaxial wafer, and the GaN epitaxial wafer at least includes a substrate 11 and a buffer layer 12, a channel layer 13, a barrier layer 14, and a cap layer 15 sequentially formed on the substrate 11, wherein the cap Layer 15 serves as the upper surface of the GaN epitaxial wafer, and a two-dimensional electron gas thin layer 16 is formed between the channel layer 13 and the barrier layer 14 , and the two-dimensional electron gas thin layer 16 is locate...

Embodiment 2

[0064] Different from Embodiment 1, in this embodiment, a filling dielectric layer 8 is also included between the GaN cap layer 15 and the gate dielectric layer 4. For its structure, see Figure 8 . The filling medium layer 8 can passivate and protect the surface, and is mainly used to eliminate the surface state of the material, reduce surface damage, and improve the stability and reliability of the device. In practical applications, the material filling the dielectric layer 8 can be SiO 2 、Si 3 N 4 and at least one of AlN.

[0065] based on Figure 8 In the fabrication process of the enhanced HEMT shown, the difference from Embodiment 1 is that before performing step 102, it is necessary to deposit a filling dielectric layer 8 on the upper surface of the GaN epitaxial wafer, and then perform step 102 and subsequent steps step. In practical applications, the filling dielectric layer 8 may be deposited on the upper surface of the GaN epitaxial wafer by means of LPCVD, AL...

Embodiment 3

[0067] Based on the first embodiment, the difference from the first embodiment is that in this embodiment, when preparing the enhanced HEMT, the source and drain are prepared first, and the gate is prepared after the superalloy, so that the high temperature of the ohmic metal can be avoided. The influence of the alloy on the gate metal can improve the gate reliability of the device. Specifically, the flow chart of its preparation method can be found in Figure 9 , may include the following steps:

[0068] Step 201: Prepare a GaN epitaxial wafer. The specific process is the same as step 101.

[0069] Clean the GaN epitaxial wafer. After cleaning, perform the following steps:

[0070] Step 202: Prepare source and drain windows.

[0071] First realize device isolation by etching or ion implantation, and then image 3 For the GaN epitaxial wafer shown, the source region and the drain region are first defined by a photolithography process (such as the yellow light process), an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More