FinFET and preparation method thereof

A substrate and drain technology, applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve the problems of low on-off speed and high power consumption of devices, and achieve lower power consumption, lower working voltage, and suppression The effect of the short channel effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

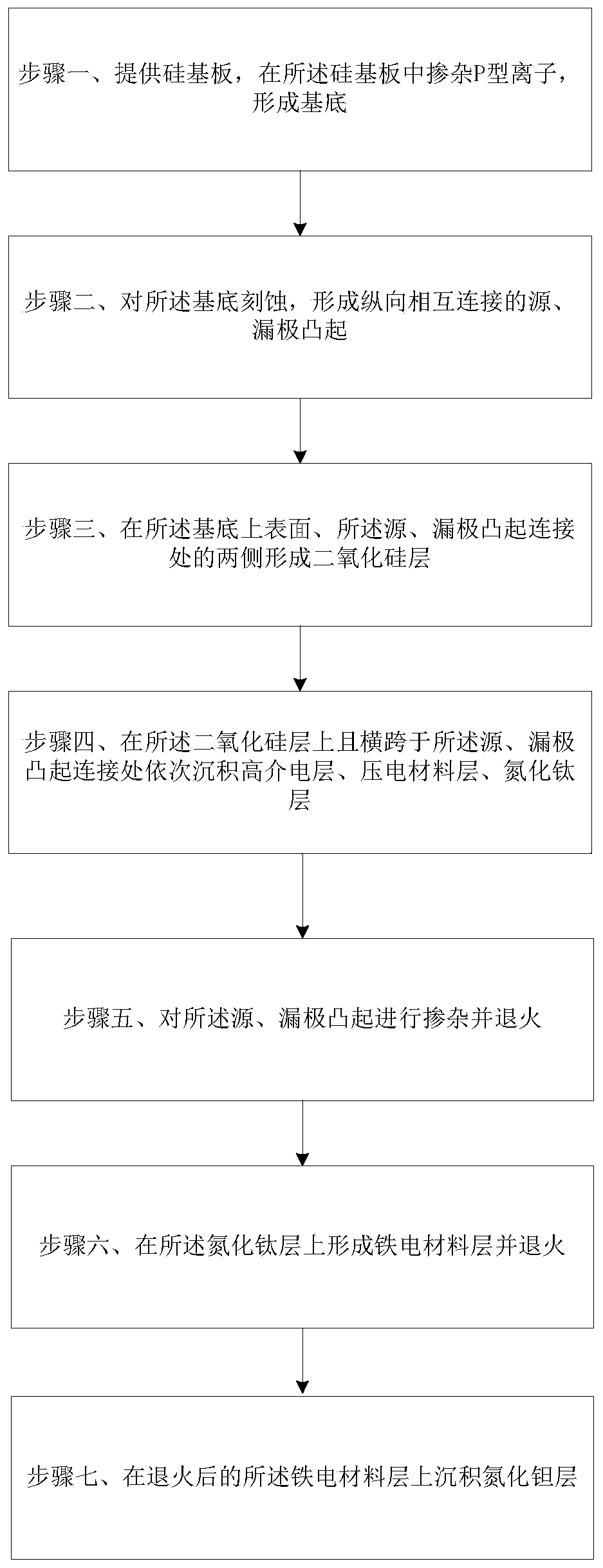

[0034] The present invention also includes the preparation method of the FinFET, refer to figure 2 , figure 2 Shown is the flow chart of the preparation method of the FinFET of the present invention. The method at least includes the following steps:

[0035] Step 1, providing a silicon substrate, doping P-type ions in the silicon substrate to form the base 01; that is to say, the formation of the P-type base is by implanting P-type ions into the silicon material plate, so as to form figure 1 P-type substrate 01 shown.

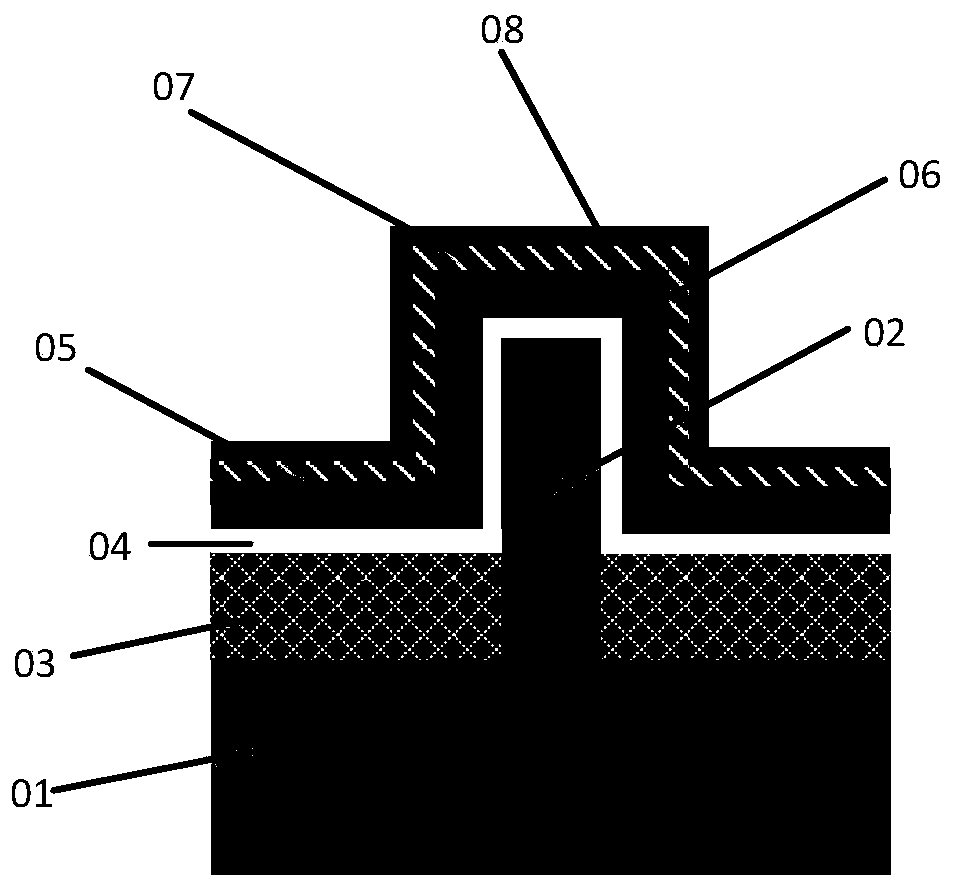

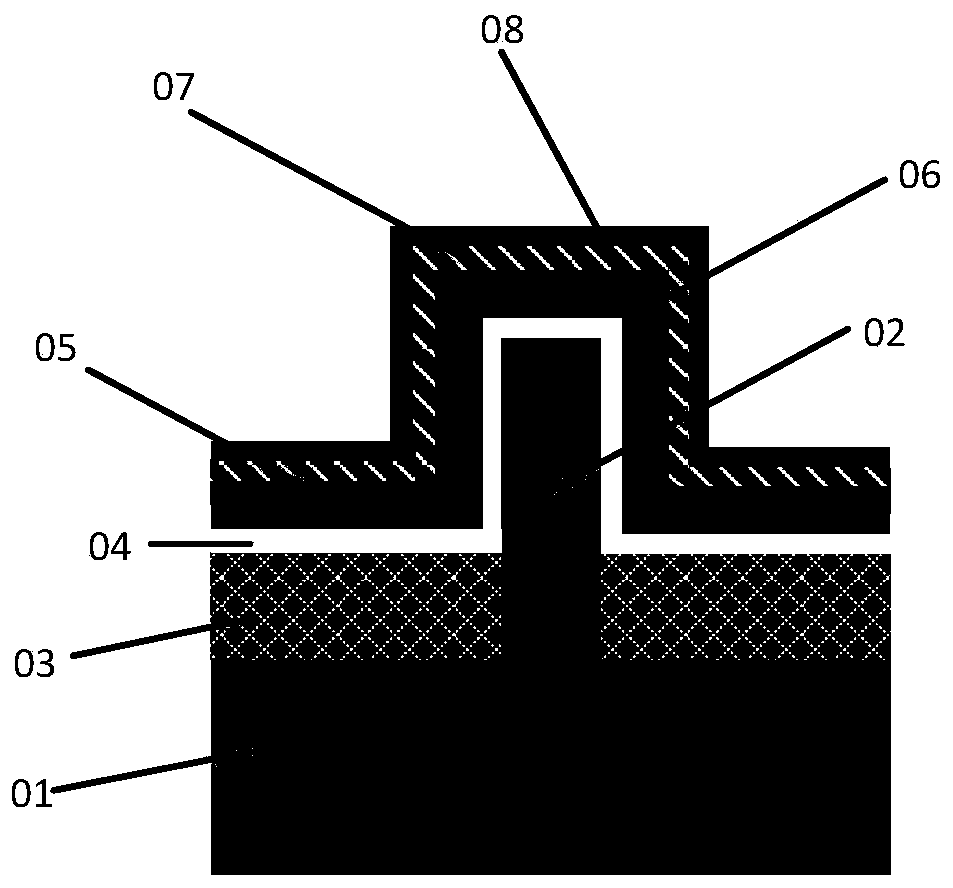

[0036] Step 2. Etching the base to form protrusions of source and drain interconnected vertically;figure 1 Shown is a schematic diagram of the cross-sectional structure of the FinFET, therefore, the source and drain bumps can only be figure 1 presented in the form of cross-sections. The source and drain protrusions serve as the source and drain of the FinFET;

[0037] Step 3, forming a silicon dioxide layer 03 on the upper surface of the substrate 01 and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More