Semiconductor device structure and preparation method thereof

A device structure, semiconductor technology, applied in the direction of semiconductor devices, electrical solid devices, electrical components, etc., can solve the problems that the performance of transistors cannot meet the requirements, the conduction current drops, etc., to improve the short channel effect, increase the channel area, The effect of increasing the width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

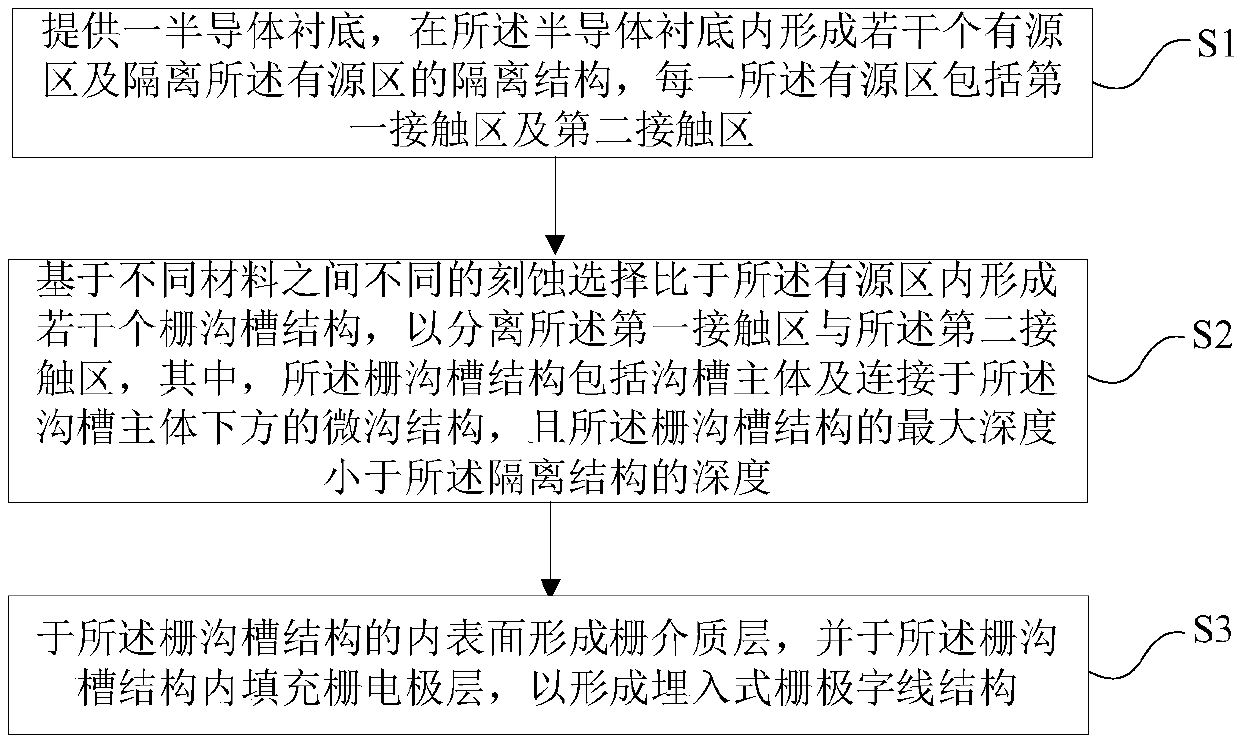

[0078] Such as figure 1 Shown, the preparation method of a kind of semiconductor device structure of the present invention, described preparation method comprises the following steps:

[0079] 1) A semiconductor substrate is provided, and several active regions and isolation structures for isolating the active regions are formed in the semiconductor substrate, and each active region includes a first contact region and a second contact region ;

[0080] 2) Based on different etching selectivity ratios between different materials, several gate trench structures are formed in the active region to separate the first contact region and the second contact region, wherein the gate trench The trench structure includes a trench body and a micro-trench structure connected under the trench body, and the maximum depth of the gate trench structure is smaller than the depth of the isolation structure; and

[0081] 3) A gate dielectric layer is formed on the inner surface of the gate trenc...

Embodiment 1

[0103] Such as Figure 8-19 As shown, this embodiment provides a method for forming the gate trench structure 103, and the forming steps specifically include:

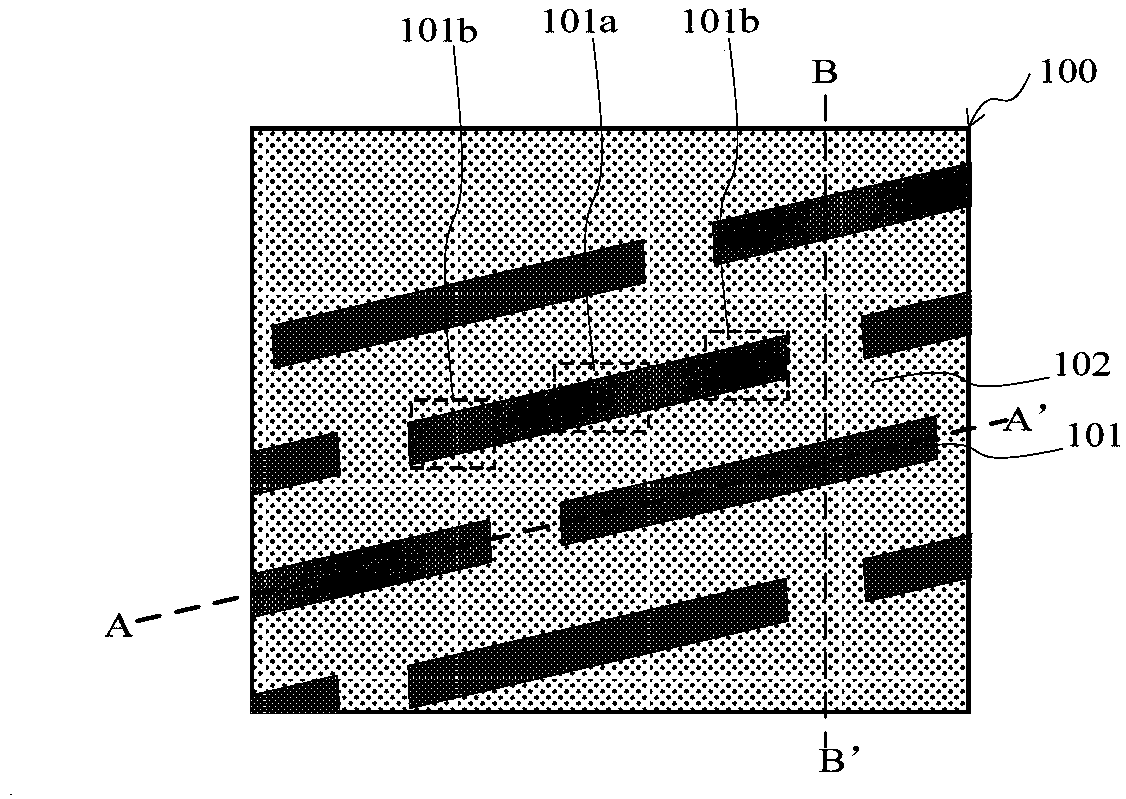

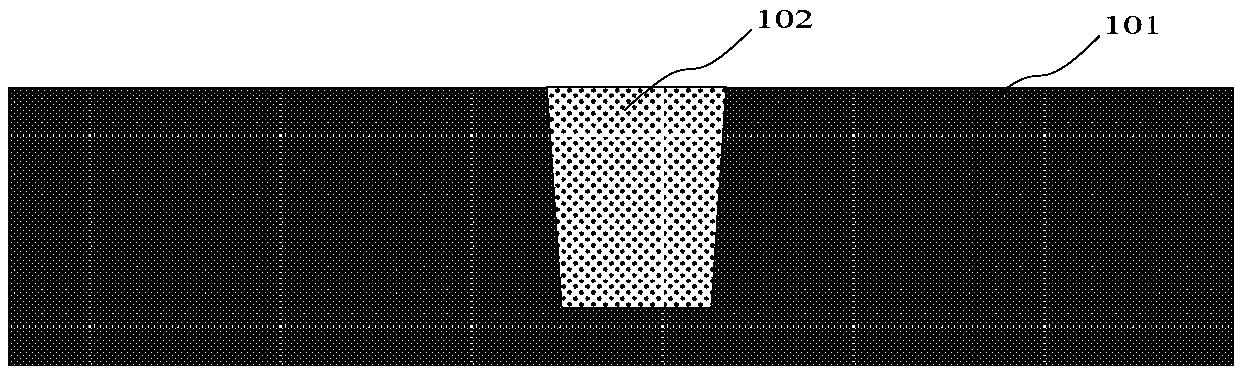

[0104] Such as Figure 8-10 As shown, step 2-1) is performed to form an etching mask layer 112 on the semiconductor substrate 100, and several gate trench windows 106 are formed on the etching mask layer. The window 106 exposes the active region 101 and defines the position of the gate trench structure 103; specifically, first defines the position of the gate trench structure 103 in the active region 101, in an example In each of the active regions 101, two gate trench windows 106 are correspondingly formed, and are located between the adjacent first contact regions 101a and the second contact regions 101b.

[0105] As an example, the etching mask layer 112 includes a hard mask layer 104 and a photoresist layer 105 sequentially formed on the semiconductor substrate 100, and the thickness of the hard mask layer 501 is...

Embodiment 2

[0116] Such as Figure 20-39 As shown, this embodiment provides another method for forming the gate trench structure, and the forming steps specifically include:

[0117] Such as Figure 20-22 As shown, step 2-1) is performed to form a hard mask layer 201 on the semiconductor substrate 100, and several etching windows 203 are formed on the hard mask layer, and the etching windows 203 expose The active region 101 defines the position of the gate trench structure 103; specifically, first defines the position of the gate trench structure 103 in the active region 101, in an example, each Two gate trench windows 106 are correspondingly formed on the active region 101, and are located between the adjacent first contact region 101a and the second contact region 101b.

[0118] As an example, the hard mask layer 201 is formed based on a photoresist layer 202, so as to etch down the photoresist layer 202 to form the gate trench structure 103, wherein the thickness of the hard mask lay...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More