Device for read-write control based on time division multiplexing in DDR3

A technology of time-division multiplexing and write control, which is applied in the direction of instrumentation, electrical digital data processing, etc., to achieve the effects of simple structure, improved system operating frequency, and reduced implementation cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

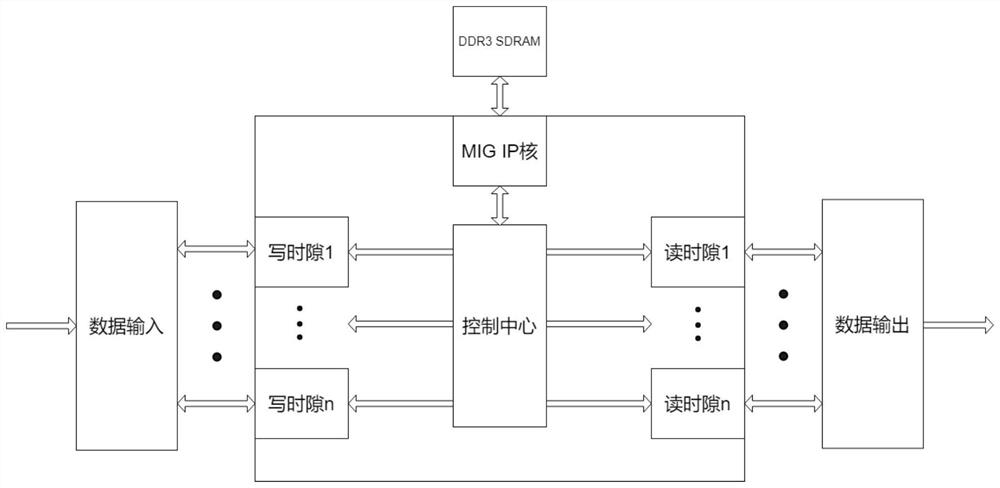

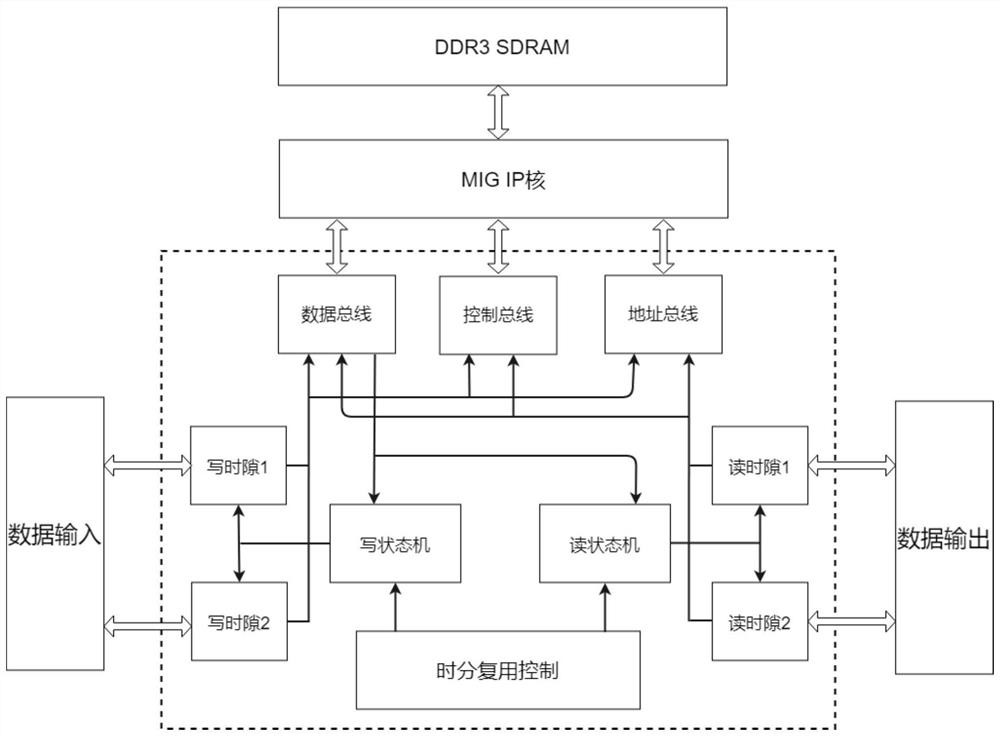

Method used

Image

Examples

example 1

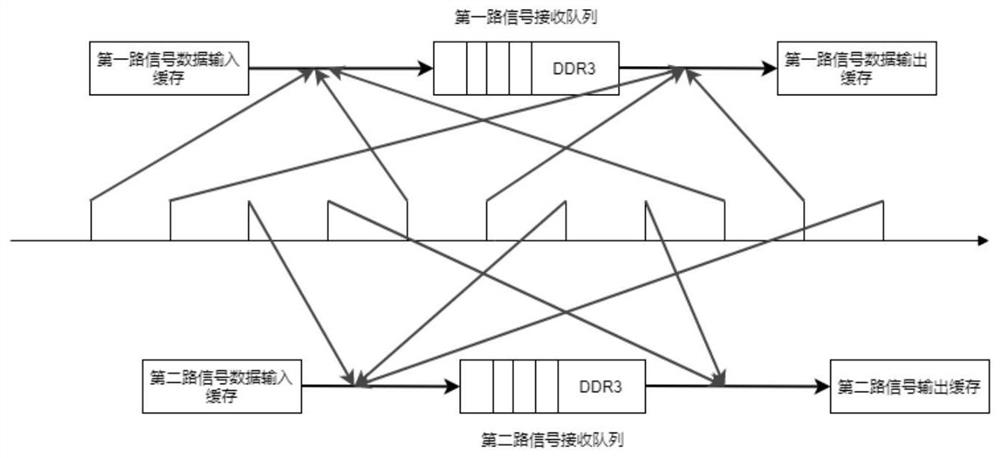

[0037] Example 1: FPGA simulation and implementation of matrix interleaving of multiple independent signals using DDR3

[0038] The simulation platform used in Example 1 is Matlab, Vivado 2018.2 and Modelsim 10.6e, and the implemented architecture is as follows Figure 4 As shown, the implemented function is based on the time-division multiplexing technology proposed in this paper, and the matrix column permutation and interleaving process of two independent signals is completed in one piece of DDR3. First in Matlab based on Figure 4 Establish a simulation platform for matrix interleaving and deinterleaving in the data conversion process: generate data sources, and simulate on the simulation platform to obtain the output data of each module and the final correct simulation results, which are used for comparison with FPGA simulation and implementation results.

[0039] exist Figure 4 The input data in is the same source data used by the Matlab simulation platform. In the da...

example 2

[0042] Example 2: Example 1 implements the analysis of throughput and DDR3 speed in the model

[0043] The simulation platform used in Example 2 is Vivado 2018.2 and Modelsim 10.6e. In the example, the working frequency of DDR3 is 400MHZ, the data bit width is 16bit, and the working mode of burst length is 8. The data throughput rate input by the data combination module is 0.85Gb / s, and the speed that DDR3 writes data can reach is 1.02Gb / s. The DDR3 write data rate is greater than the input data throughput rate, and the process of writing data can be completed correctly. Similarly, the read data throughput rate of the decompression module is 1.19Gb / s, and the DDR3 read data rate is 1.13Gb / s. The DDR3 read data rate is lower than the throughput rate of the dedata module output data, and the data read process can be completed correctly.

[0044] Since the interleaving principle involves the sequence conversion of data, the write address sequence of the DDR3 data writing process...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More