Porcelain paste of wet process multilayer chip ceramic capacitor and preparation method thereof

A multi-layer chip, wet process technology, applied in the direction of laminated capacitors, capacitors, fixed capacitors, etc., can solve the problems of easy delamination of products, high cost of process equipment, narrow product series, etc. The risk of delamination and cracking, the improvement of shrinkage matching, the effect of less organic solvent content

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

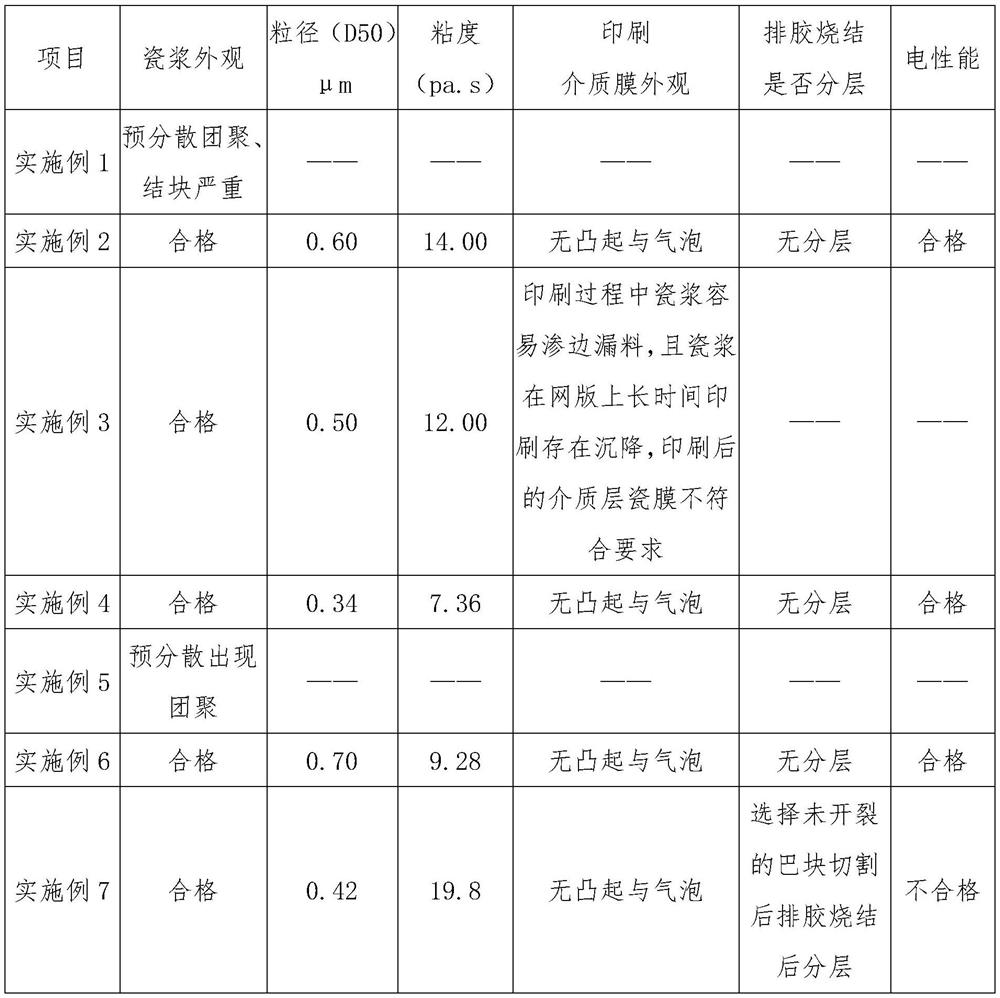

Examples

Embodiment 1

[0020] 1. The composition of the ceramic paste of the multi-layer chip ceramic capacitor is calculated as: 85% of the ceramic powder, 1.5% of the organic additive, and 13.5% of the organic solvent.

[0021] Further, the organic additive is composed of a dispersant and a binder in a mass ratio of 3:2; wherein, the dispersant is formed by mixing phosphate ester and ethyl cellulose type A in a mass ratio of 6:4; The binder is composed of ethyl cellulose type B, ethyl cellulose type C, ethyl cellulose type D and polyvinyl butyral in a mass ratio of 1:1:1:4.

[0022] Further, the organic solvent is composed of solvent A type and solvent B type in a mass ratio of 1:1; wherein, solvent A type is formed by mixing terpinolene and cineol in a mass ratio of 1:5 ; Solvent B is made by mixing terpinolene and α-terpineol in a mass ratio of 1:6.

[0023] 2. A method for preparing a ceramic paste for a multilayer chip ceramic capacitor, comprising the following steps:

[0024] (1) Pre-dispe...

Embodiment 2

[0032] 1. The composition of the ceramic paste of the multi-layer chip ceramic capacitor is calculated as: 80% of ceramic powder, 2% of organic additives, and 18% of organic solvent.

[0033] Further, the organic additive is composed of a dispersant and a binder in a mass ratio of 3:2; wherein, the dispersant is formed by mixing phosphate ester and ethyl cellulose type A in a mass ratio of 6:4; The binder is composed of ethyl cellulose type B, ethyl cellulose type C, ethyl cellulose type D and polyvinyl butyral in a mass ratio of 1:1:1:4.

[0034] Further, the organic solvent is composed of solvent A type and solvent B type in a mass ratio of 1:1; wherein, solvent A type is formed by mixing terpinolene and cineol in a mass ratio of 1:5 ; Solvent B is made by mixing terpinolene and α-terpineol in a mass ratio of 1:6.

[0035] 2. A method for preparing a ceramic paste for a multilayer chip ceramic capacitor, comprising the following steps:

[0036] (1) Pre-dispersion: add an o...

Embodiment 3

[0043] 1. The composition of the ceramic paste of the multi-layer chip ceramic capacitor is calculated as: 77% of ceramic powder, 7% of organic additives, and 16% of organic solvent.

[0044]Further, the organic additive is composed of a dispersant and a binder in a mass ratio of 2:1; wherein, the dispersant is formed by mixing phosphate ester and ethyl cellulose type A in a mass ratio of 4:3; The binder is composed of ethyl cellulose type B, ethyl cellulose type C, ethyl cellulose type D, and polyvinyl butyral in a mass ratio of 1:1:1:3.

[0045] Further, the organic solvent is formed by mixing alcohol and toluene in a mass ratio of 1:1, and both alcohol and toluene are electronic grades.

[0046] 2. A method for preparing a ceramic paste for a multilayer chip ceramic capacitor, comprising the following steps:

[0047] (1) Pre-dispersion: add organic solvent, dispersant and porcelain powder into the mixing tank, and stir for 35 minutes at 200 rpm stirring speed to obtain pre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More