Method and device for improving surface mobility of silicon carbide lateral double-diffusion field effect transistor

A lateral double diffusion, field effect transistor technology, applied in the field of wide bandgap power semiconductor devices, can solve the problems of reduced carrier mobility, high on-resistance, poor forward conduction characteristics, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0022] A method for improving the surface mobility of silicon carbide lateral double-diffused field effect transistors. The method introduces a voltage bias tube. When the silicon carbide LDMOS transistor is forward-conducting, the high voltage in the drift region of the voltage bias tube can be transmitted to the Multiple polysilicon field plates above the surface of the drift region of the SiC LDMOS transistor. The high voltage on the polysilicon field plate has the effect of attracting electrons, which makes the surface of the drift region of the LDMOS tube gather electrons, increase the electron concentration, reduce the probability of a single electron being captured by the traps on the surface of the oxide layer above the drift region, and increase the electron mobility.

Embodiment 2

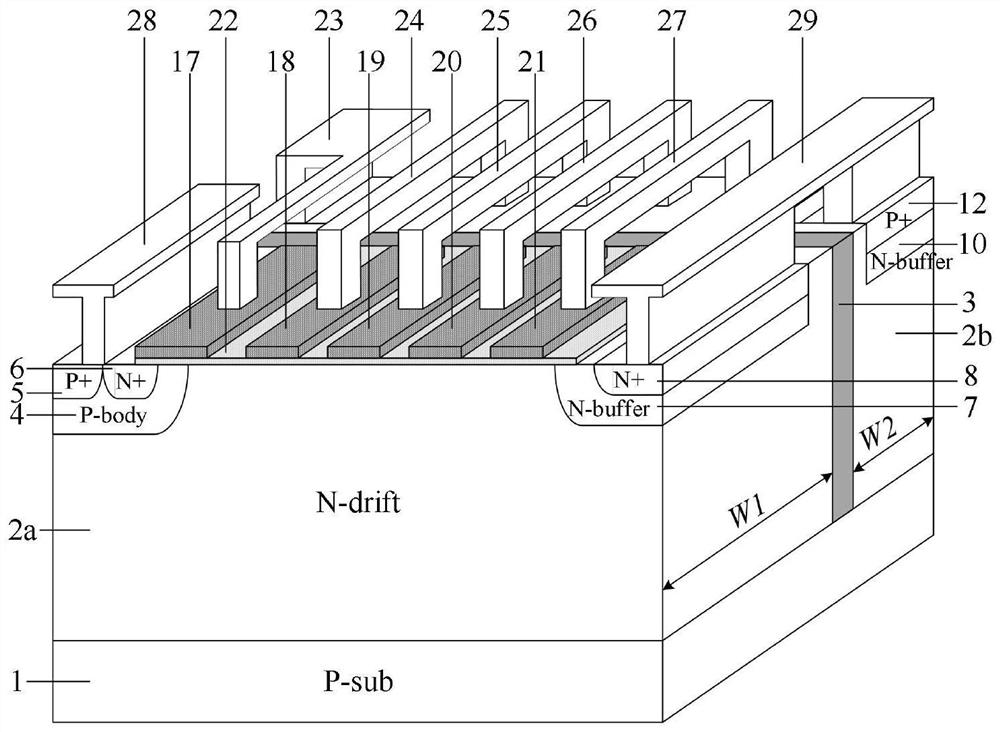

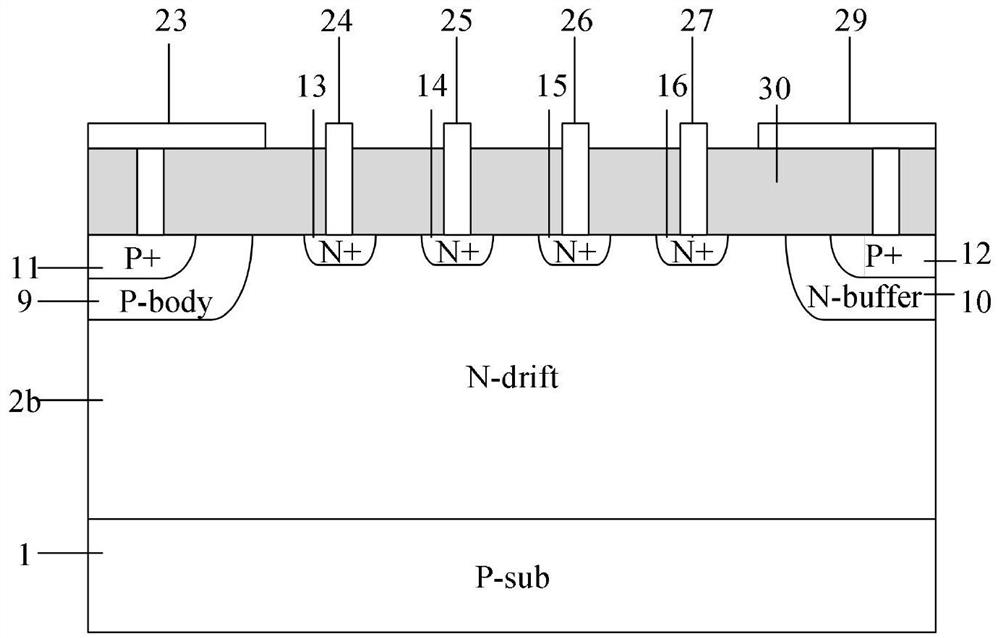

[0024] In general, the silicon carbide lateral double-diffused metal oxide semiconductor field effect transistor with high surface mobility of the present invention is composed of LDMOS with multiple polysilicon field plates and a voltage bias transistor.

[0025] Combine below figure 2 image 3 , the present invention is described in detail:

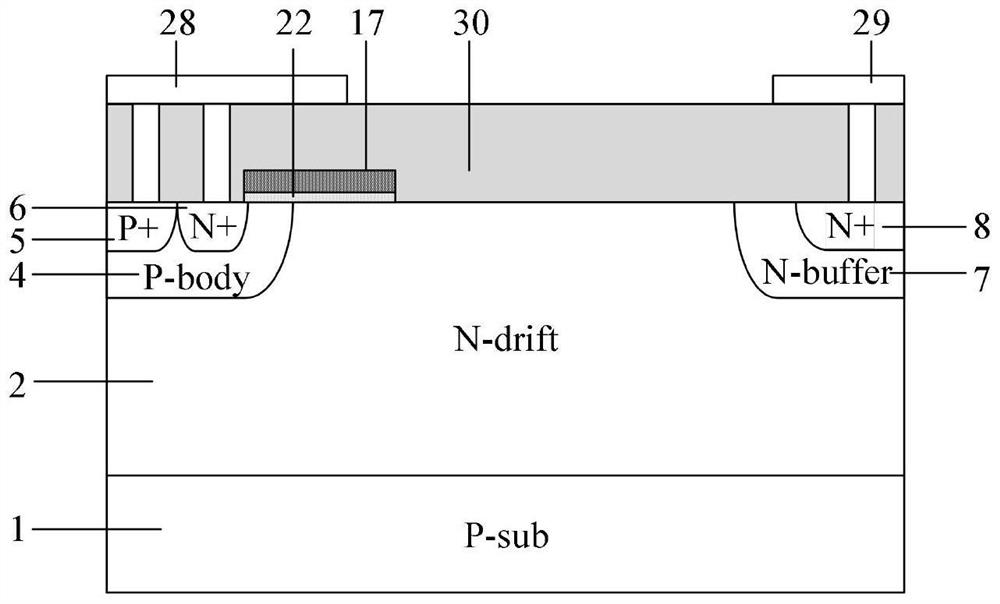

[0026]A device used in the method for improving the surface mobility of silicon carbide lateral double-diffused field effect transistors, comprising: a P-type substrate 1, an N-type drift region 2 is arranged on the P-type substrate 1, and an N-type drift region 2 is arranged on the N-type drift region. A P-type isolation layer 3 is provided in the region 2 and is divided into a first N-type drift region 2a and a second N-type drift region 2b by the P-type isolation layer 3, and a second N-type drift region 2a is respectively provided on the first N-type drift region 2a. A P-type base region 4 and the first N-type buffer layer 7 are ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More