Preparation method of semiconductor structure

A semiconductor and gate structure technology, applied in the field of semiconductor structure preparation, can solve the problems of low yield of high-voltage transistors, exposure, photoresist peeling, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

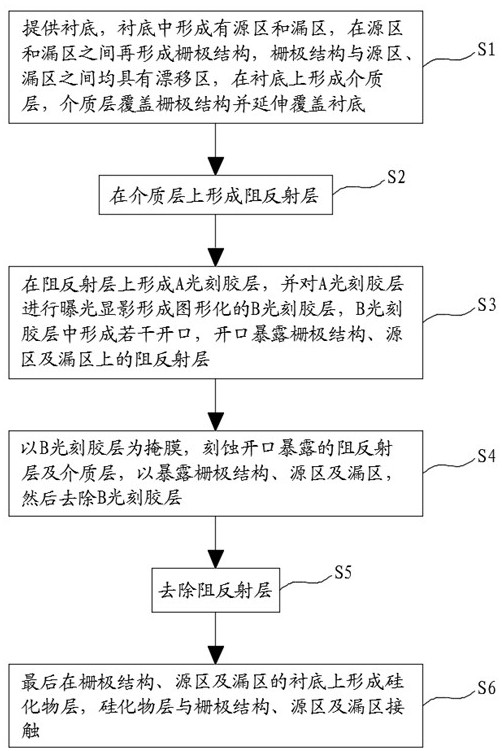

[0053] In this embodiment, a method for preparing a semiconductor structure is proposed, the semiconductor structure is a high-voltage transistor, and the method for preparing the semiconductor structure includes the following steps:

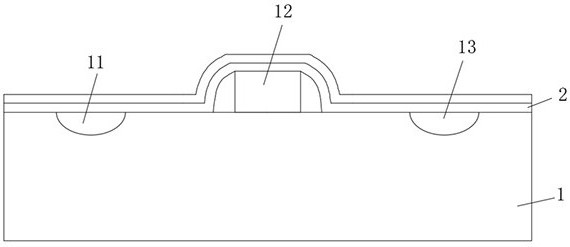

[0054] S1: reference figure 2 , providing a substrate 1, an active region 11 and a drain region 13 are formed in the substrate 1, a gate structure 12 is formed between the source region 11 and the drain region 13, and a gate structure 12 is formed between the source region 11 and the drain region 13. There is a drift region between them, and a dielectric layer 2 is formed on the substrate 1, and the dielectric layer 2 covers the gate structure 12, the source region 11, the drain region 13 and the drift region;

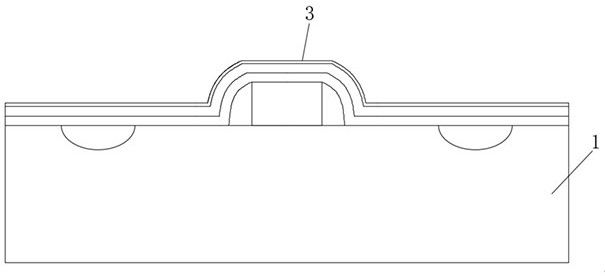

[0055] S2: Reference image 3 , forming an anti-reflection layer 3 on the dielectric layer 2 by vapor deposition;

[0056] S3: Reference Figure 4 and Figure 5 , form A photoresist layer 4 on anti-reflection layer 3, and A photores...

Embodiment 2

[0063] refer to Figure 8 , in this embodiment, a processing device for semiconductor structure preparation is proposed, including a fixed shaft 400, a clamping mechanism 200 and a loading tray 100, the fixed shaft 400 is vertically arranged, and the clamping mechanisms 200 are distributed in a circular array around the fixed shaft 400 , the clamping mechanism 200 is used to clamp the loading tray 100, the loading tray 100 is loaded with components, and the side of the fixed shaft 400 is provided with processing stations, the number of processing stations is the same as that of the clamping mechanism 200 and the positions correspond to each other, the fixed shaft 400 An adjustment mechanism is installed on the top, and the adjustment mechanism is used to adjust the clamping mechanism 200 to intermittently enter and exit each station sequentially. Through the above arrangement, it is possible to adjust the clamping mechanism 200 to move in and out of each station intermittently...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More