Array waveguide grating demultiplexer chip of cladding integrated micro lens and preparation method of array waveguide grating demultiplexer chip

A technology of arrayed waveguide grating and demultiplexer, which is applied in the direction of optical waveguide light guide, optical waveguide coupling, light guide, etc., can solve the problem of low photoelectric conversion efficiency, achieve the effects of convenient operation, reduced beam size, and improved efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

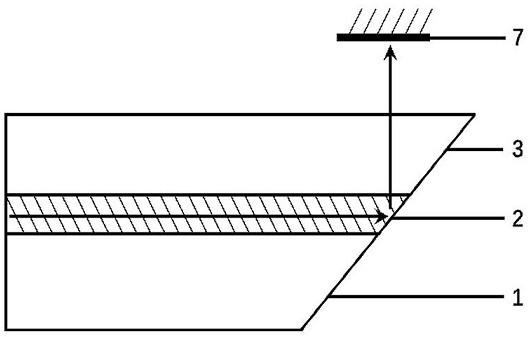

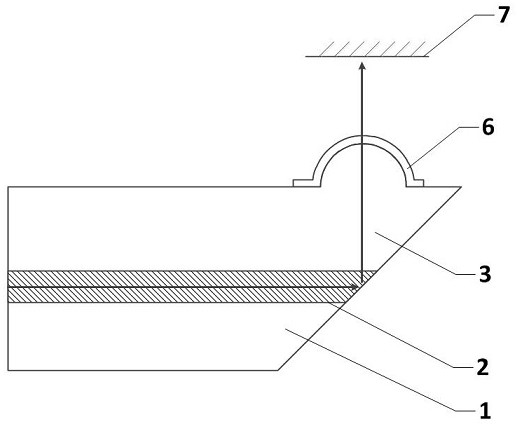

[0043] An arrayed waveguide grating demultiplexer chip with cladding integrated microlens, such as figure 2 As shown, it includes a sample layer 1, a core layer 2 and a cladding layer 3, the cladding layer 3 is located on the sample layer 1, the core layer 2 is located between the sample layer 1 and the cladding layer 3, and the top of the cladding layer 3 is etched with A microlens corresponding to the light beam passing through the core layer 2 . The output waveguide of the chip is provided with a total reflection angle, and the degree of the total reflection angle is 45°. The light beam in the core layer 2 corresponds to the center position of the microlens in the vertical direction after being reflected by the end face of the output waveguide. When the light beam propagates to the output waveguide along the horizontal direction in the core layer 2, it is reflected by the 45° total reflection angle at the output waveguide, and the light beam passes through the cladding 3 a...

Embodiment 2

[0047] A method for preparing an arrayed waveguide grating demultiplexer chip with cladding integrated microlenses, comprising the following steps:

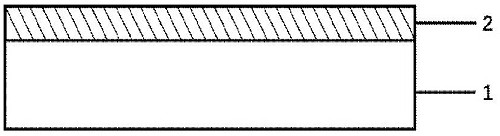

[0048] S1. Grow a germanium-doped silicon dioxide layer on the sample layer 1 prepared from silicon dioxide to obtain the core layer 2, and transfer the AWG demultiplexer waveguide pattern to the core layer by photolithography and etching processes 2 on. Specifically, as shown in Figure 3, a silicon dioxide sample is selected as the sample layer 1, and a core layer 2 of germanium-doped silicon dioxide with a thickness of 4 microns is grown on the surface of the sample layer 1 using PECVD equipment. The specific growth conditions It is: temperature 300°C, pressure 300mTorr, RF power 650W, SiH4 flow rate 15sccm, N2O flow rate 1500sccm, GeH4 flow rate 4sccm, deposition time 25min; use polysilicon as a mask, process arrayed waveguide grating by photolithography, etching and other processes The waveguide pattern of the user chip.

...

PUM

| Property | Measurement | Unit |

|---|---|---|

| angle | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| reflectance | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More