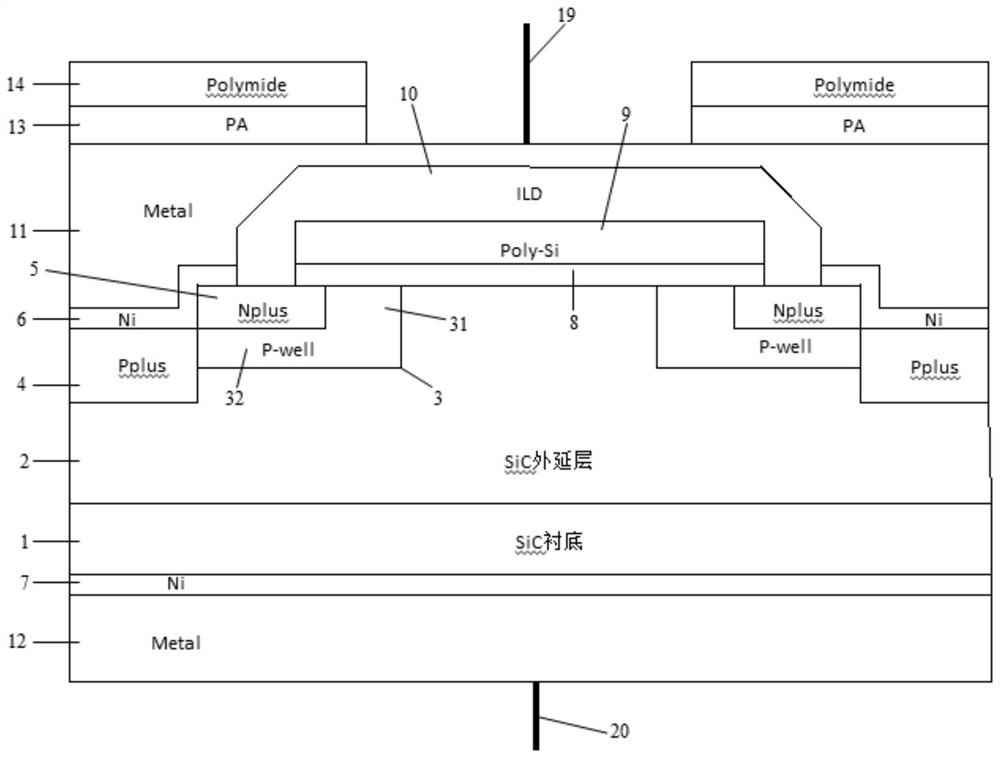

SiC MOSFET structure and manufacturing method thereof

A manufacturing method and epitaxial layer technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as device performance degradation, ohmic contact increase, and reliability reduction, so as to reduce ohmic contact resistance and reduce Effect of specific contact resistance and reduction of device loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

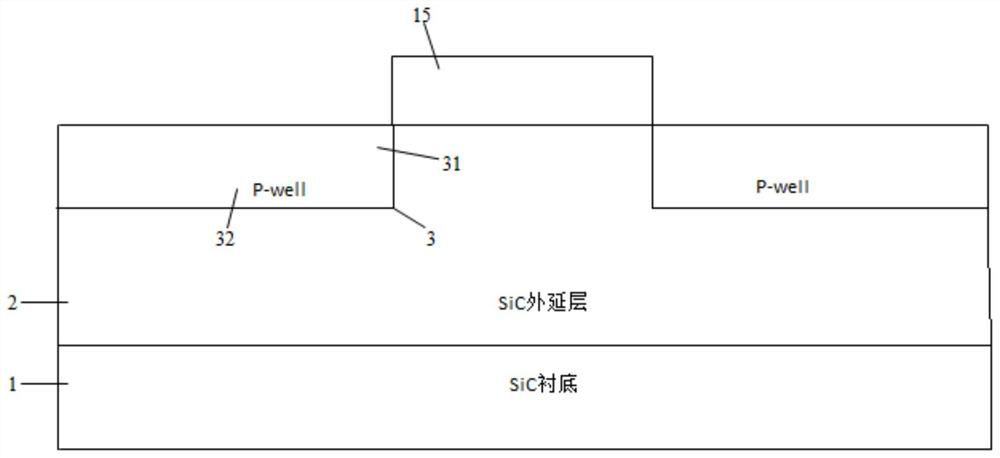

[0077] Such as figure 2 As shown, the RCA method is used to clean the silicon carbide epitaxial wafer, and BOE (buffered oxide etch) or DHF (diluted HF) is used to remove the natural oxide on the silicon carbide surface to obtain a clean silicon carbide epitaxial wafer.

[0078] Such as image 3 As shown, on the clean SiC surface, a mask is deposited by means of deposition. This mask is the P-well implant mask 15. The type of mask can be polysilicon formed by LPCVD deposition, silicon dioxide or PECVD deposition. deposited silicon dioxide, USG, etc., and use photoresist to coat the P-well implantation mask on the P-well implantation mask to protect the P-well implantation mask, and expose the P-well implantation mask 15 corresponding to the P-well implantation area development, and through photolithography and dry etching, the P-well mask pattern is transferred to the mask layer, and Al ion implantation is performed to form a P-well region.

[0079] Such as Pic 4-1 As sho...

Embodiment 2

[0093] Such as figure 2 As shown, the RCA method is used to clean the silicon carbide epitaxial wafer, and BOE (buffered oxide etch) or DHF (diluted HF) is used to remove the natural oxide on the silicon carbide surface to obtain a clean silicon carbide epitaxial wafer.

[0094] Such as image 3 As shown, on the clean SiC surface, a mask is deposited by means of deposition. This mask is the P-well implant mask 15. The type of the mask is polysilicon formed by LPCVD deposition, and it is coated with photoresist. The P-well implantation mask is protected on the P-well implantation mask, and the P-well implantation mask 15 corresponding to the P-well implantation area is exposed and developed, and the P-well implantation is formed by photolithography and dry etching. The mask pattern is transferred to the mask layer, and Al ions are implanted to form a P-well region.

[0095] Such as Figure 4-2 As shown, without removing the P-well mask pattern, put the wafer with the polysi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More