Producing method for shallow ridges separation

A manufacturing method and shallow trench technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., to solve problems affecting component performance, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

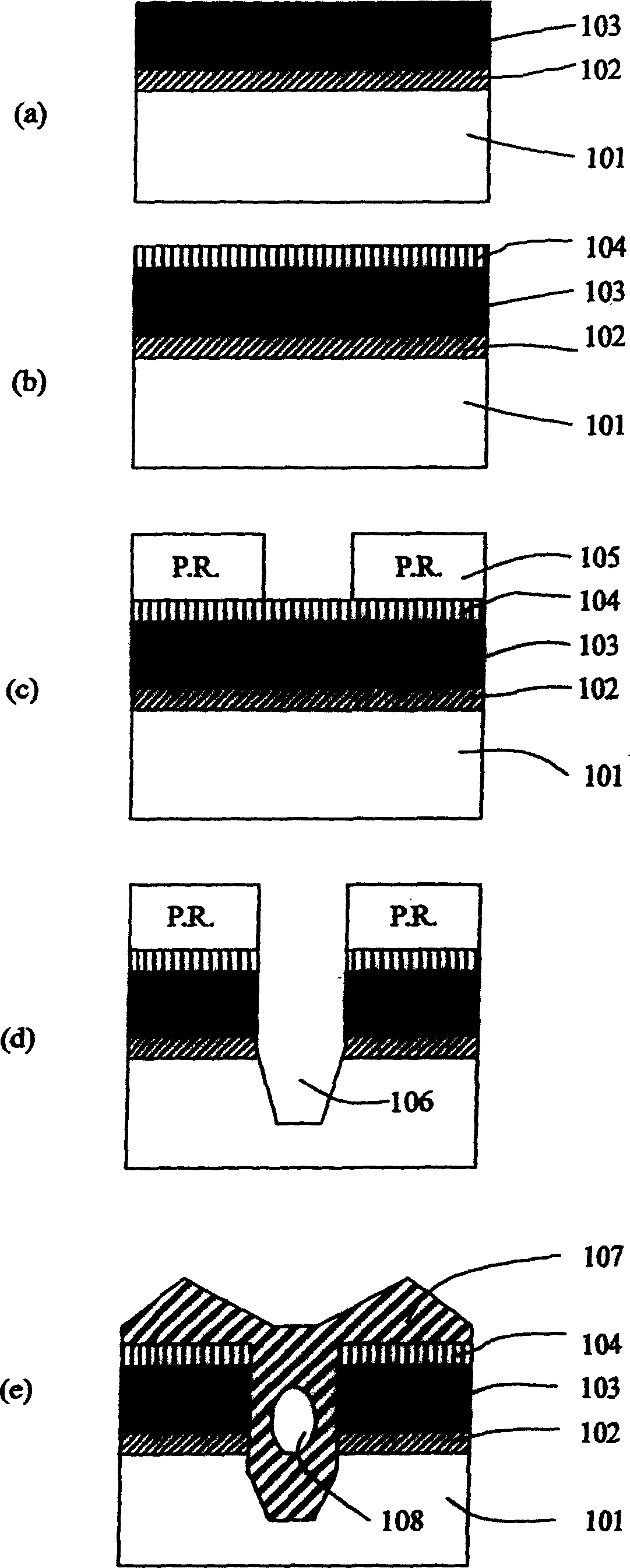

[0025] Please refer to Figure 4 . Figure 4 It is a cross-sectional view of the manufacturing process of the first embodiment of the present invention. Figure 4 (a) shows that a pad oxide layer 102 is grown on a silicon substrate 101 by a dry oxidation method, and its thickness is about 50 Å to 200 Å to reduce defects on the silicon surface and relieve the stress of the subsequently deposited silicon nitride layer 103 , and then deposit a layer of silicon nitride layer 103 on the pad oxide layer 102 by LPCVD or PECVD, with a thickness of about 500 Å to 2000 Å, as a hard mask when etching shallow trenches.

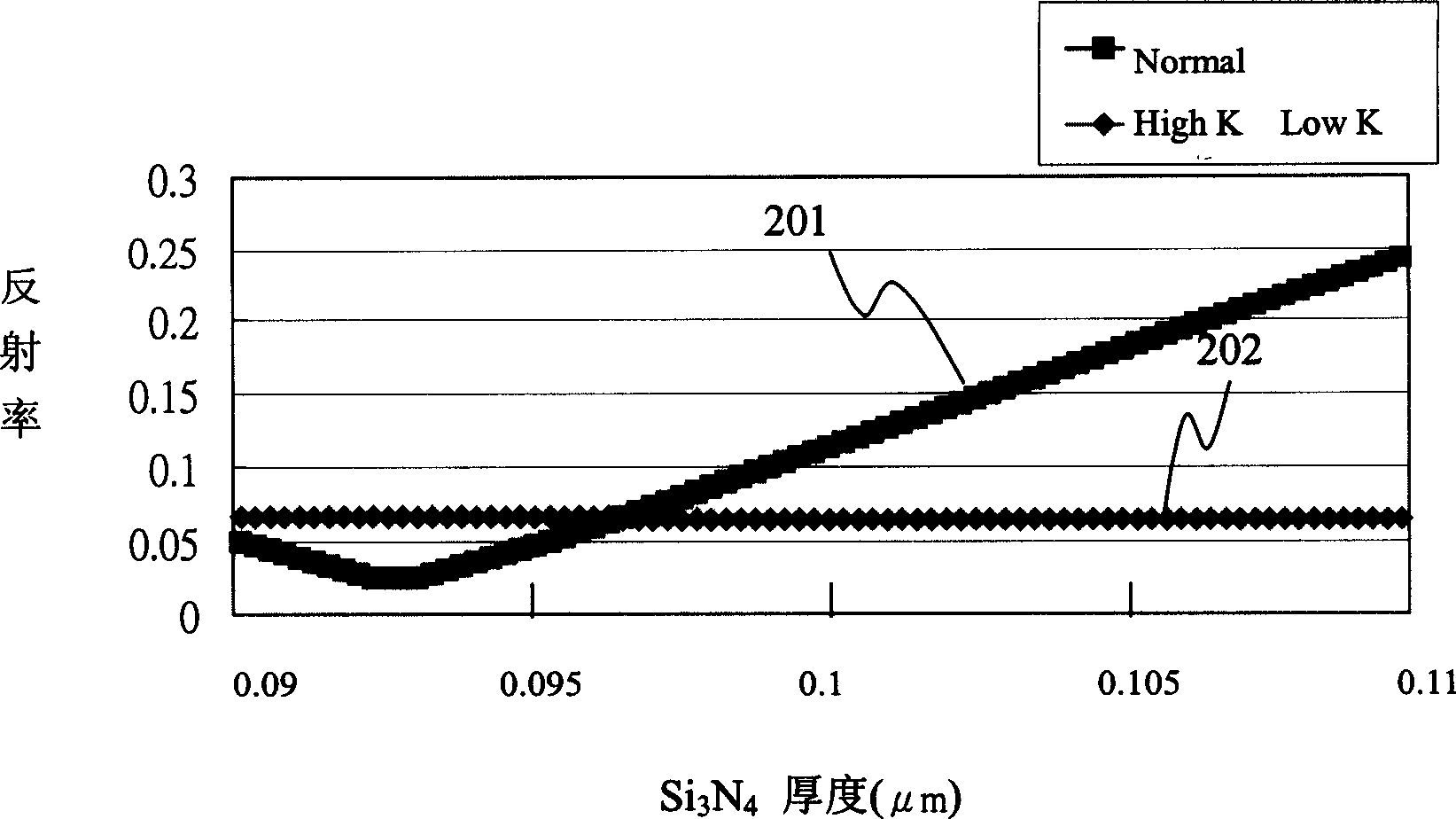

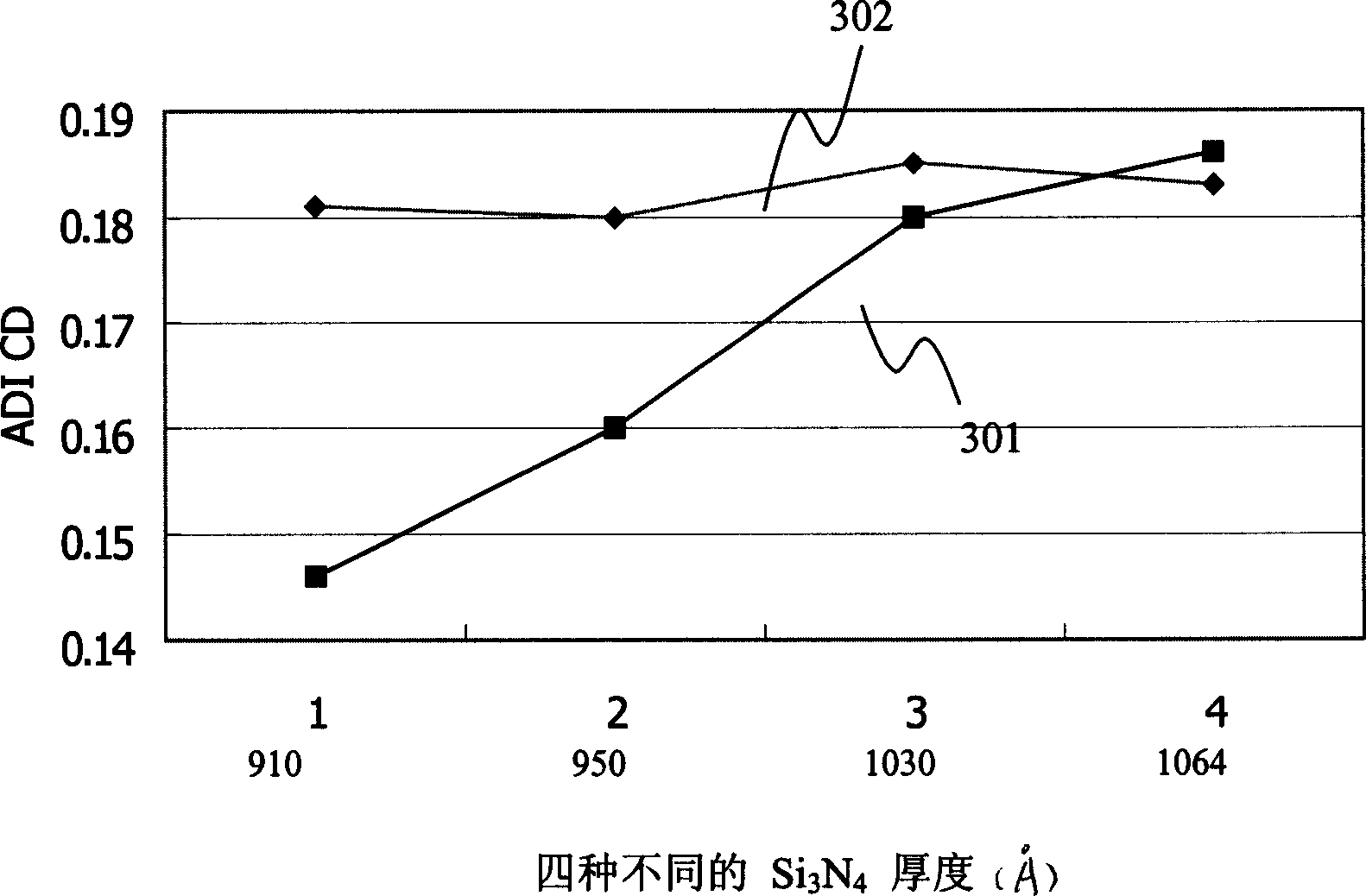

[0026] refer to Figure 4 (b), Figure 4 (b) shows that a silicon oxynitride layer 401 with a high absorption coefficient is deposited on the silicon nitride layer 103 first, and then a silicon oxynitride layer 402 with a low absorption coefficient is deposited as an anti-reflection layer. A method of depositing a silicon oxynitride layer with a high absorption coeffi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More