Method for manufacturing compound semiconductor substrate

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of transistor diode rectification characteristic electronic device performance degradation, reliability degradation, etc., to achieve excellent performance and reliability, temperature Small rise and excellent heat dissipation effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0052] [Manufacturing of compound semiconductor substrates]

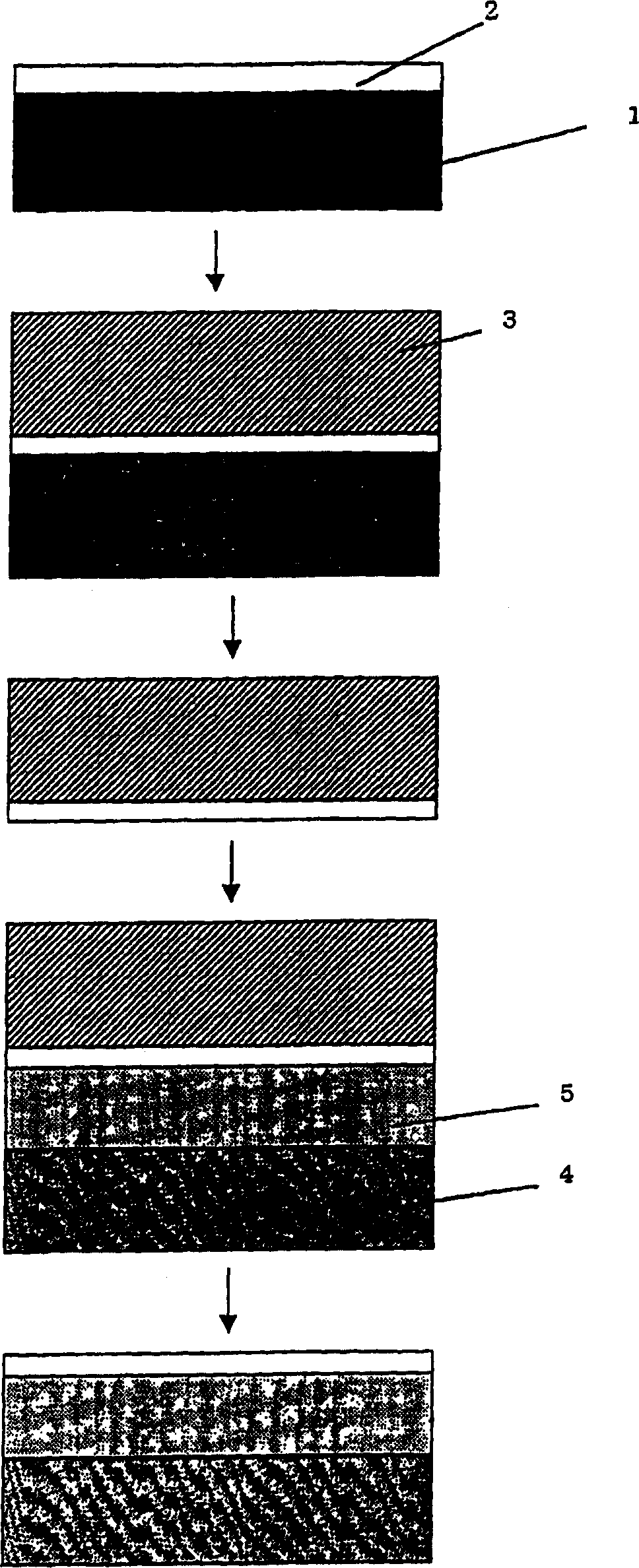

[0053] figure 1 Indicates the process of manufacturing compound semiconductors.

[0054] On a commercially available single crystal semi-insulating GaAs substrate 1 with a diameter of 100mm and a thickness of 630μm, trimethylgallium, triethylgallium, trimethylaluminum, trimethyl Indium, as the starting raw material containing V group elements, uses arsine (arsine) and phosphine trihydride, and as the raw material of the dopant for controlling conductivity, disilane (n-type control), trichlorobromide Methane (p-type control), organometallic vapor phase pyrolysis method used with hydrogen carrier gas, to grow the compound semiconductor functional layer 2 of the heterojunction bipolar transistor, and to manufacture the compound semiconductor substrate. The layer structure of the compound semiconductor functional layer 2 is as follows from the side of the substrate 1:

[0055] Non-doped GaAs layer 50nm

[0056] Non-...

Embodiment 2

[0075] [Manufacturing of compound semiconductor substrates]

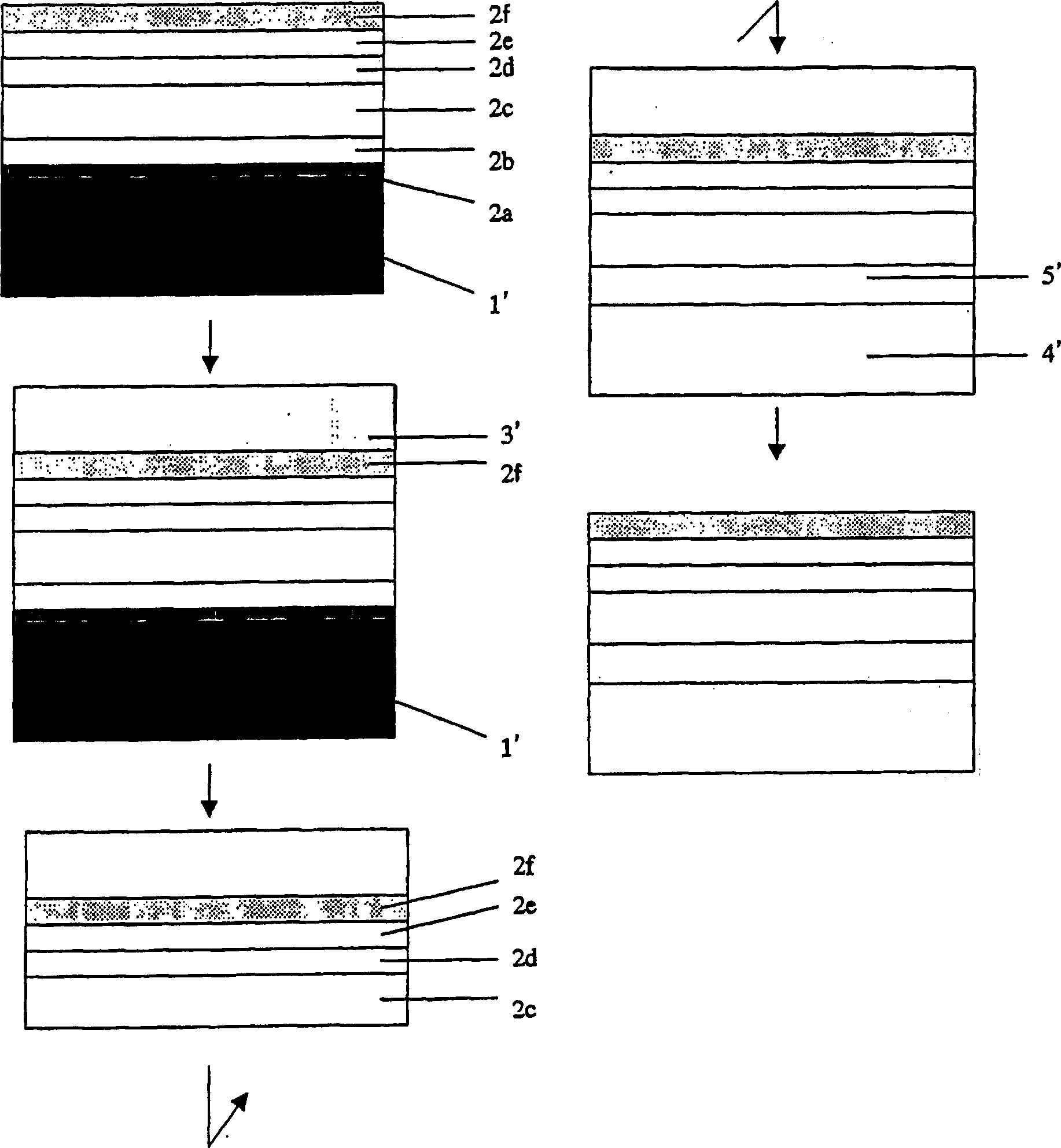

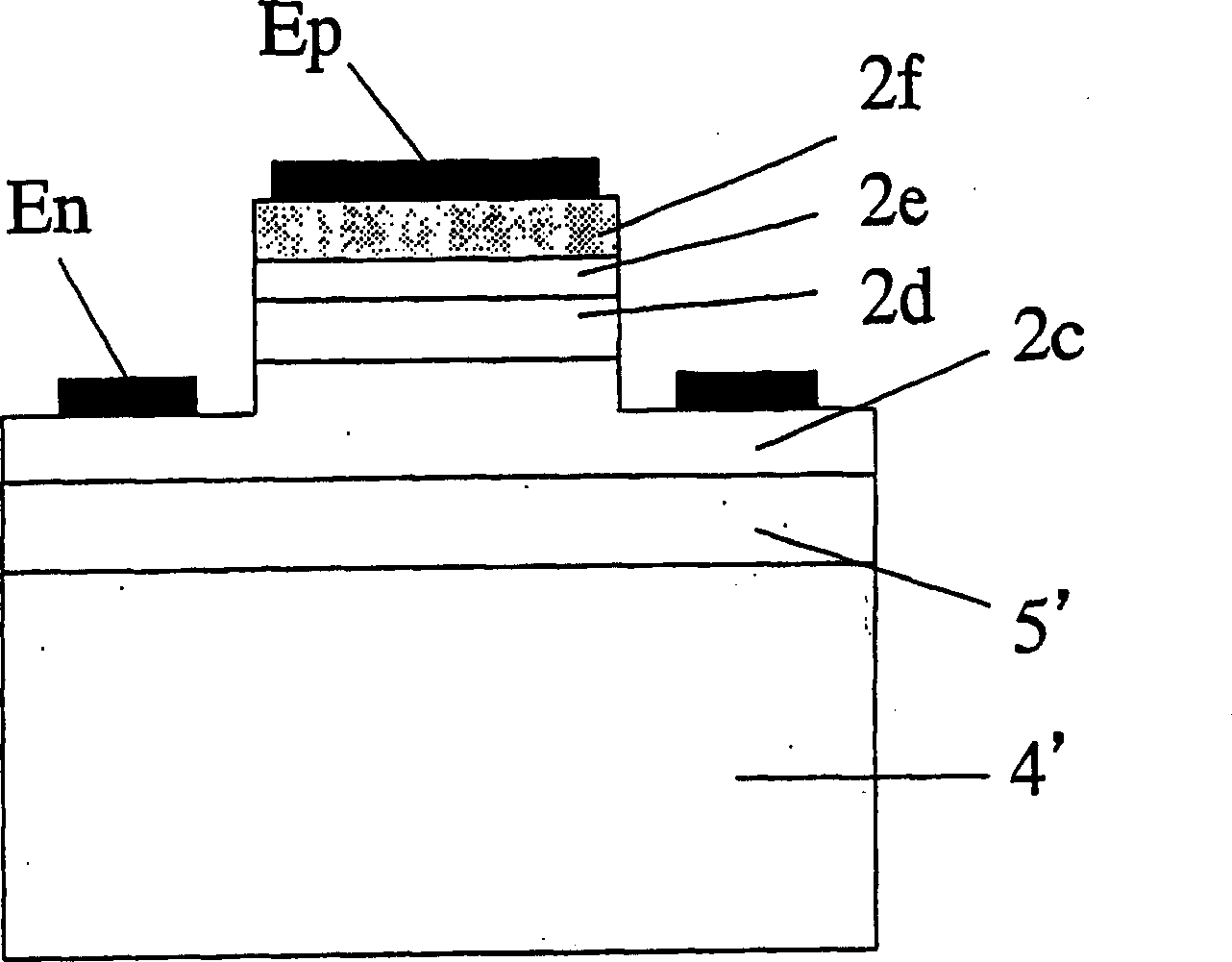

[0076] On a commercially available single-crystal insulating sapphire substrate 1' with a diameter of 50nm and a thickness of 500μm, trimethylgallium and trimethylaluminum were used as starting materials containing group III elements, and trimethylgallium and trimethylaluminum were used as starting materials containing group V elements. As a raw material, ammonia is used as a raw material for dopants to control conductivity, and silane (n-type control), cyclopentadiene-magnesium (p-type control), organometallic vapor phase thermal decomposition used with hydrogen carrier gas In this method, the compound semiconductor functional layer 2' of a pn junction diode is grown to produce a compound semiconductor substrate. The structure of the compound semiconductor functional layer 2' (refer to figure 2 ) from the substrate 1' side as:

[0077] Non-doped GaN buffer layer 2a 20nm

[0078] Non-doped GaN layer 2b 500nm

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More