Manufacturing method for multichip module

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

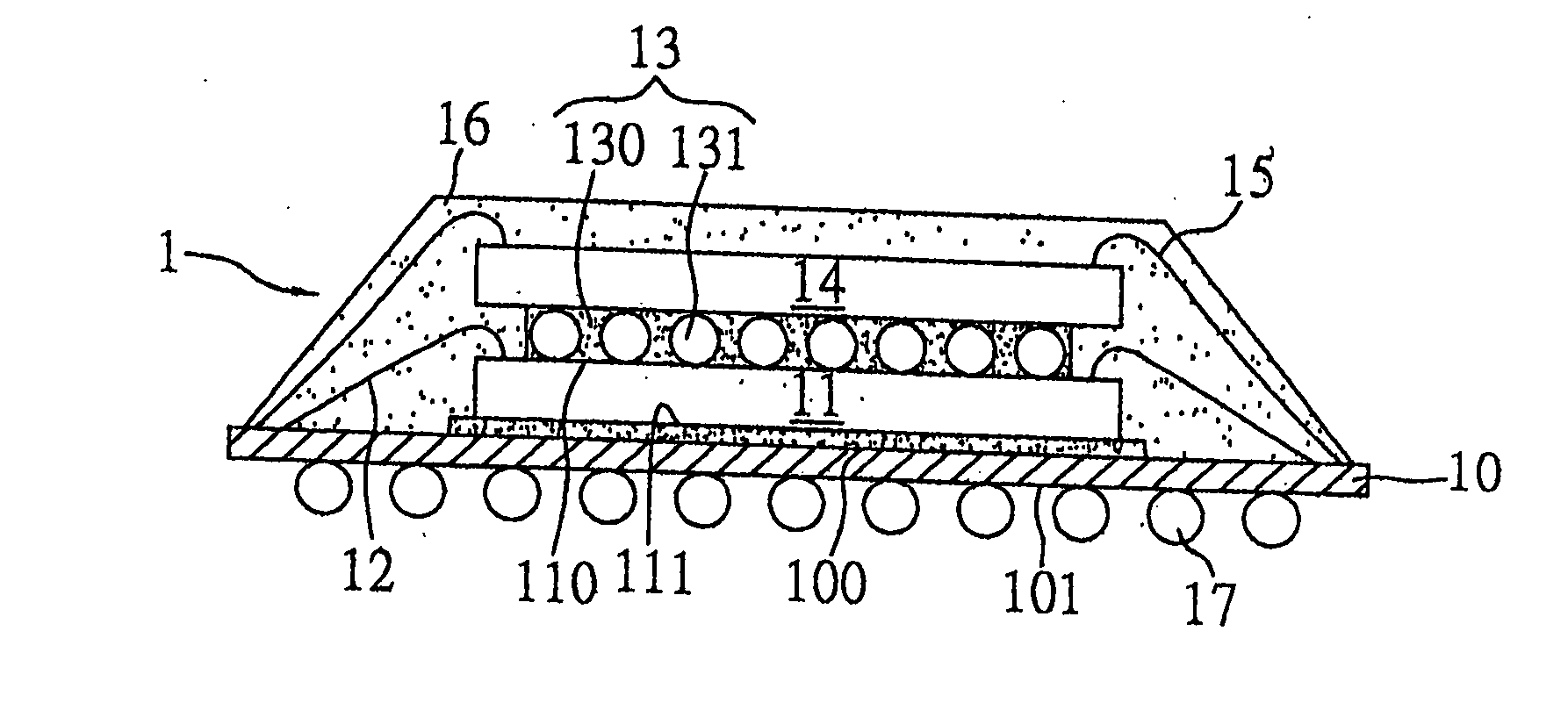

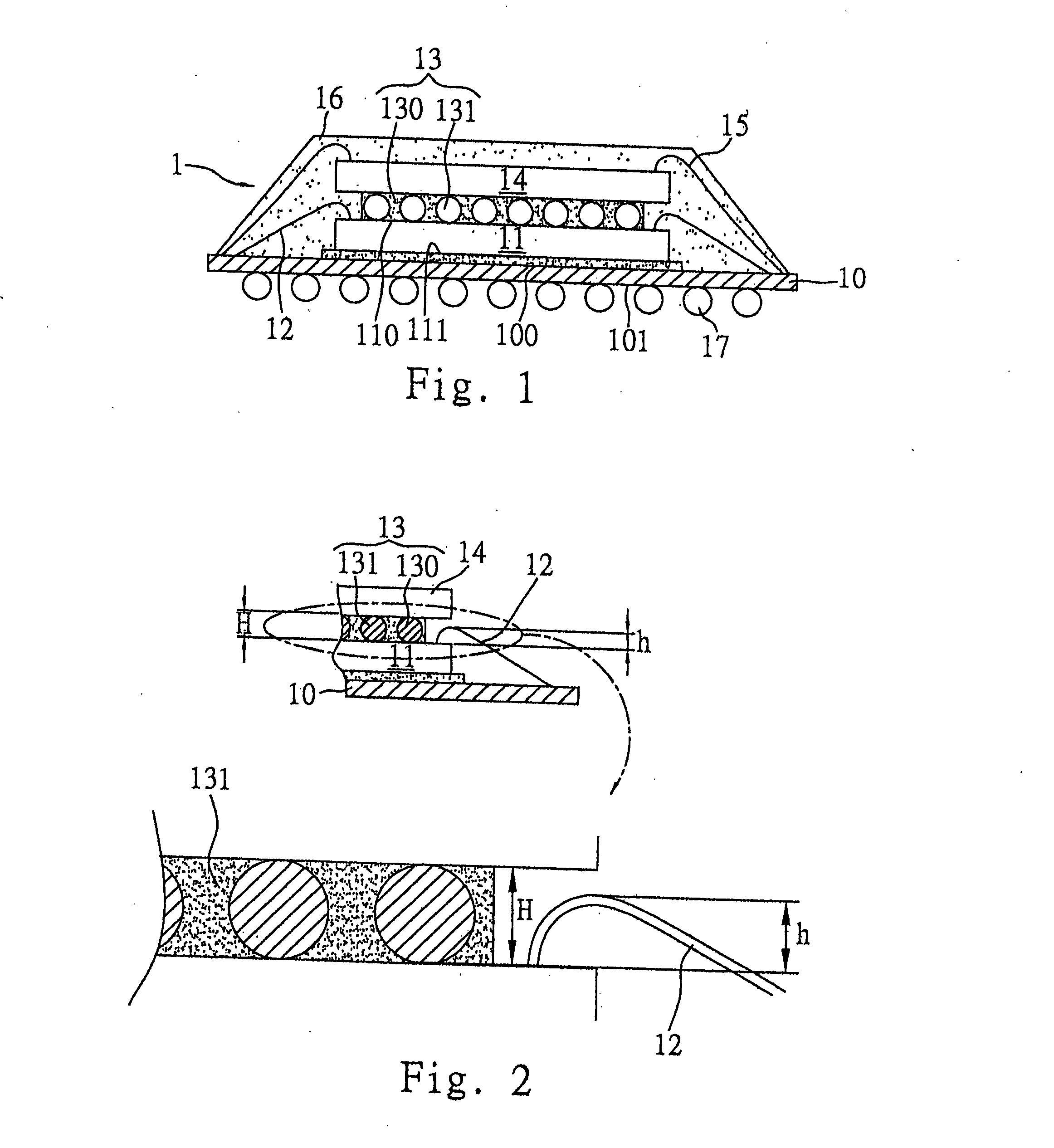

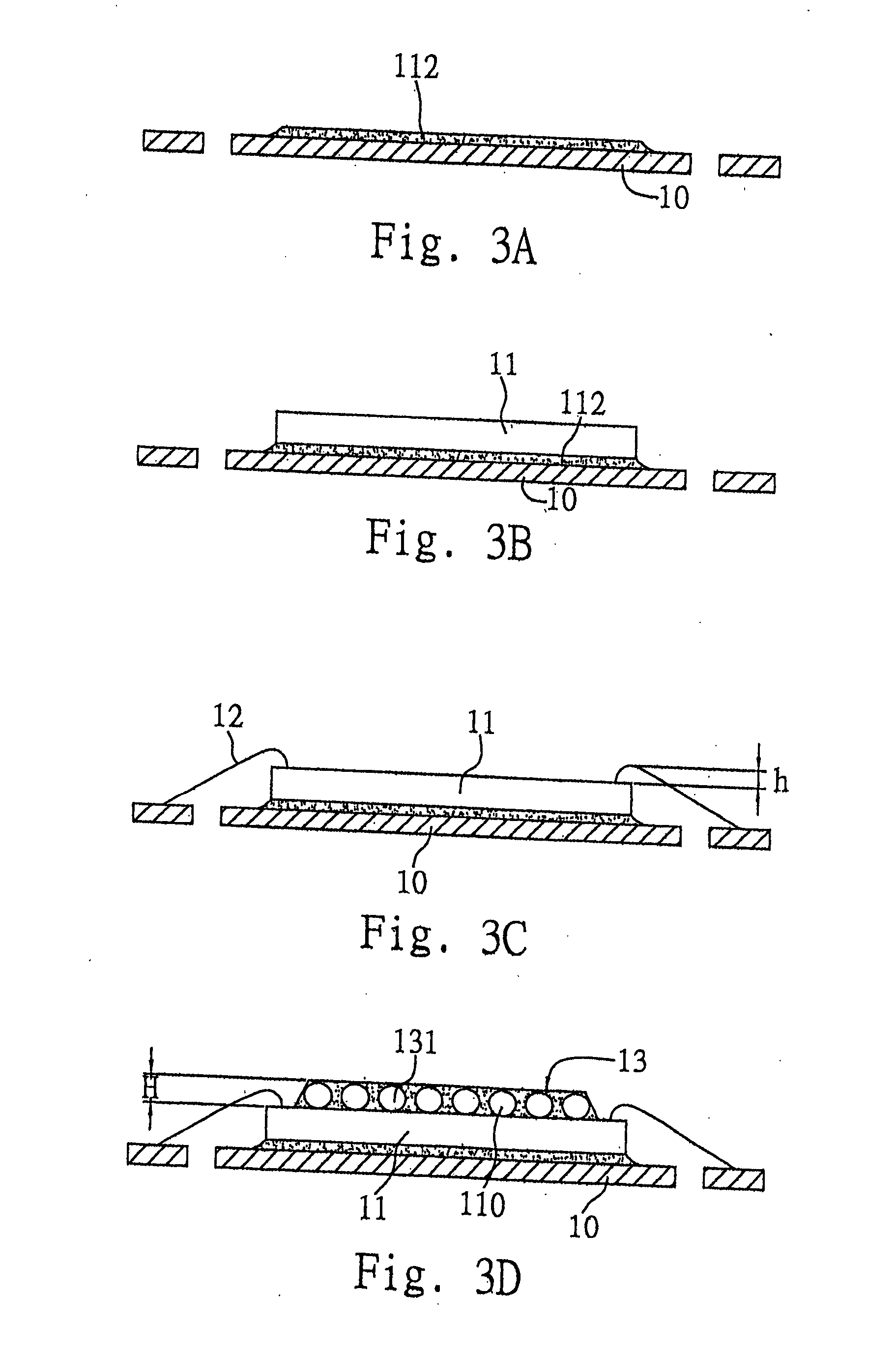

[0032] Illustrated in FIG. 1 is a cross-sectional schematic view of a multichip module according to the present invention. As shown in the diagram, the semiconductor package 1 comprises: a substrate 10; a first chip 11 adhered onto the substrate 10; a plurality of gold wires 12 for providing electrical connection between the substrate 10 and the first chip 11; an adhesive layer 13 applied over the first chip 11; a second chip 14 adhered to the adhesive layer 13; a plurality of second gold wires 15 for providing electrical connection between the second chip 14 and the substrate; and an encapsulant 16 for encapsulating the first chip 11, the first gold wires 12, the second chips 14 and the second gold wires 15.

[0033] The substrate 10 is commonly used as a duel-chip stack substrate or multi-chip stack substrate, which is made by forming a core layer made of materials such as resin, ceramic, or fiberglass and forming conductive trace pattern on the upper and lower surface of the core la...

second embodiment

[0045] Illustrated in FIG. 4 is a cross-sectional schematic view of a multichip module according to the present invention. As shown in the drawing, a multichip semiconductor package 2 of the second preferred embodiment is structurally similar to that of the foregoing first preferred embodiment, with the only difference in that, after wire bonding of the second bonding wires 25, an adhesive 23 is further applied over the active surface 240 of the second chip 24 whereon bonding pads are not disposed. This adhesive layer 23 is used for adhering at least one third chip 28 above the second chip to form a multichip semiconductor module 2 with three chips stacked perpendicularly on a substrate 20. The adhesive 23 applied on the second chip 24 also contains a plurality of fillers 231 of predetermined diameter as such, the diameter of the fillers 231 must be larger than the loop height (h′) of the second bonding wires 25. Thus, like the foregoing second chip 24, the size of a third chip 28 i...

third embodiment

[0047] Illustrated in FIG. 5 is a cross-sectional schematic view of a multichip module according to the present invention. As shown in the drawing, a multichip semiconductor package 3 of the third preferred embodiment is structurally similar to that of the foregoing first preferred embodiment, with the only difference that the wire bonding manner for the first bonding wires 32 utilizes a reverse bonding technique. The reverse bonding technique involves forming studs on each of the bonding pads disposed on the active surface 310 of the first chip 31 and bonding one end of the first gold wires 32 to the bonding pads (not shown) on the substrate 30 and then pulling each gold wires 32 upwardly allowing the other end thereof to be stitch bonded to the studs 320. With the use of the reverse bonding technique, the wire loops can be modified, allowing the loop height above the first chip 31 to become very small (approx. under 2 mils). Thus, fillers 331 of smaller diameter can be used to red...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More