Method of forming a pattern in a semiconductor device and method of forming a gate using the same

a technology of semiconductor devices and patterns, which is applied in the direction of semiconductor devices, instruments, photomechanical treatment, etc., can solve the problems of gate size reduction, gate failure, and uneven thickness of the etched portion of the thin layer, so as to reduce the roughness of the line edge due to the photolithography process, the effect of small line width and small variation in line width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

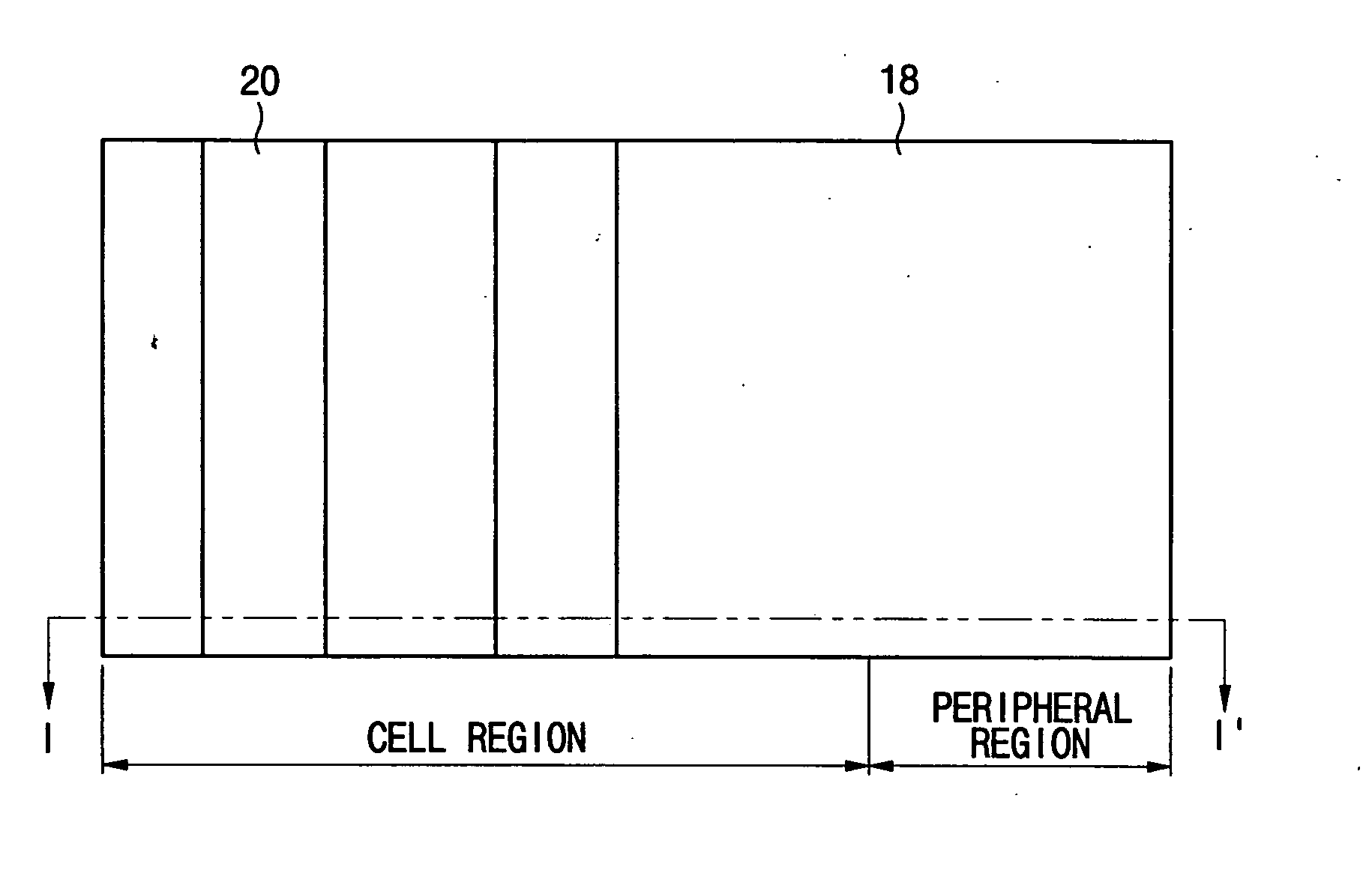

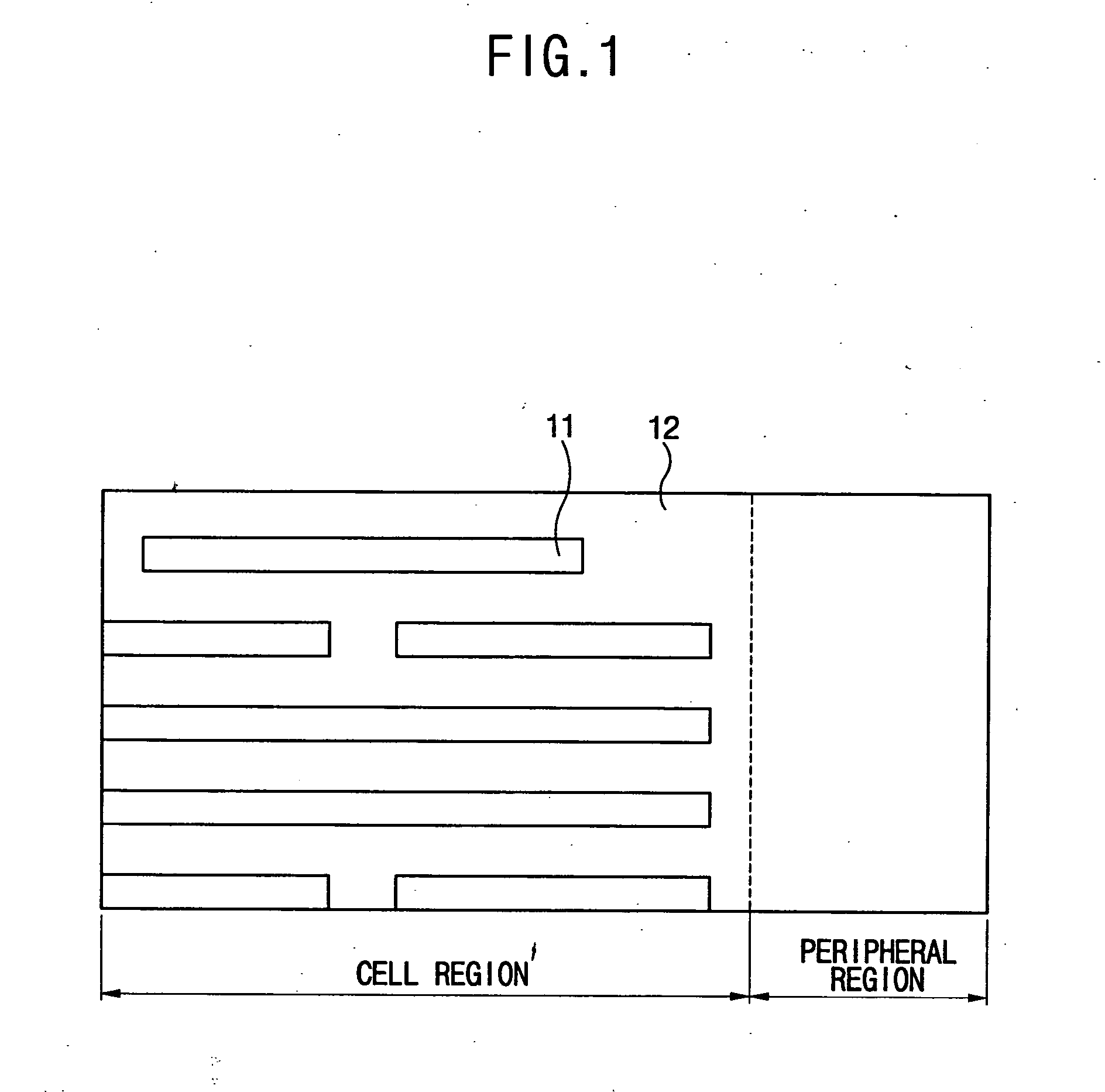

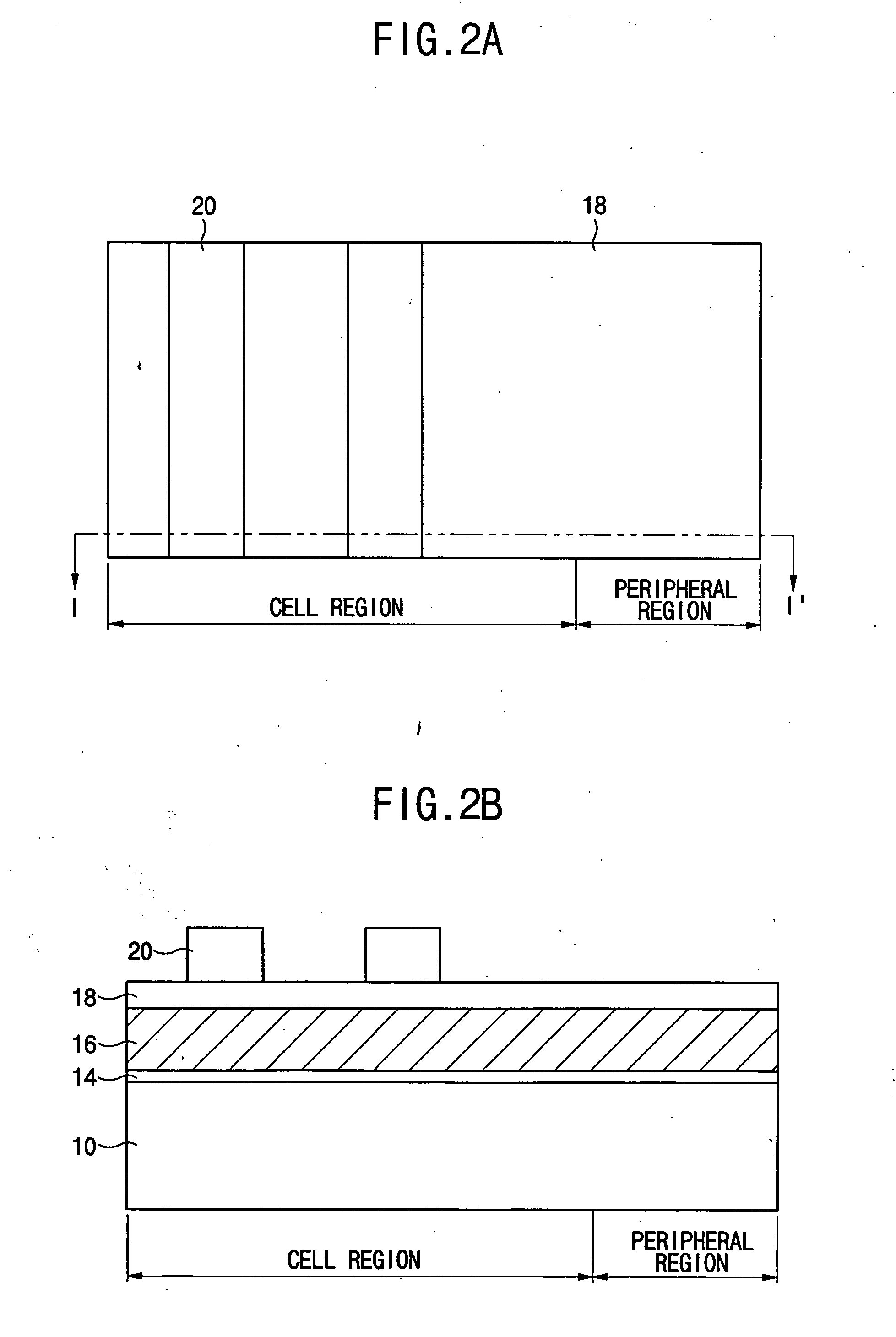

[0041]FIG. 1 is a plan view illustrating a semiconductor substrate that is divided into a cell region and a peripheral region. FIGS. 2A through 8B are plan views and cross sectional views showing processing steps of a method of forming a pattern of an I-type static random access memory (SRAM) device according to a first embodiment of the present invention. Throughout FIGS. 2A through 8B, each capital letter A designates a plan view illustrating the I-type SRAM device, and each capital letter B designates a cross sectional view taken along the line I-I′ of the corresponding figure designated by the capital letter A.

[0042] Referring to FIG. 1, a semiconductor substrate including a cell region and a peripheral region is provided. A unit memory device is positioned in the cell region, and a driving circuit for driving the unit memory device is positioned in the peripheral region. A plurality of N type impurities is selectively supplied to surface portions of the silicon substrate at wh...

embodiment 2

[0061]FIGS. 9A through 11 are plan views and cross sectional views showing processing steps of a method of forming a pattern of an I-type static random access memory (SRAM) device according to a second embodiment of the present invention. Throughout FIGS. 9A through 10B, each capital letter A designates a plan view illustrating the I-type SRAM device, and each capital letter B designates a cross sectional view taken along the line I-I′ of the corresponding figure designated by the capital letter A.

[0062] The present second embodiment of the present invention is the same as the first embodiment of the present invention except that a separation layer is added between the gate electrode layer and the buffer layer.

[0063] Referring to FIGS. 9A and 9B, a semiconductor substrate 10 including a cell region and a peripheral region is provided, and a field region and an active region are defined by the same process as described in the first embodiment with reference to FIG. 1. Therefore, a ...

embodiment 3

[0070]FIGS. 12A through 20B are plan views and cross sectional views showing processing steps of a method of forming a gate of an I-type static random access memory (SRAM) device according to a third embodiment of the present invention. Throughout FIGS. 12A through 20B, each capital letter A designates a plan view illustrating the I-type SRAM device, and each capital letter B designates a cross sectional view taken along the line I-I′ of the corresponding figure designated by the capital letter A.

[0071] Referring to FIGS. 12A and 12B, a semiconductor substrate 10 including a cell region and a peripheral region is provided, and a field region and an active region are defined by the same process as described in the second embodiment with reference to FIGS. 9A and 9B. Therefore, a unit memory device is positioned in the cell region, and a driving circuit for driving the unit memory device is positioned in the peripheral region. The active region is formed into a line shaped pattern on...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More