Compound semiconductor device and manufacturing method thereof

a semiconductor device and manufacturing method technology, applied in semiconductor devices, semiconductor/solid-state device details, electrical devices, etc., can solve the problems of cracking on pad portions, increasing the number of processes and costs,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

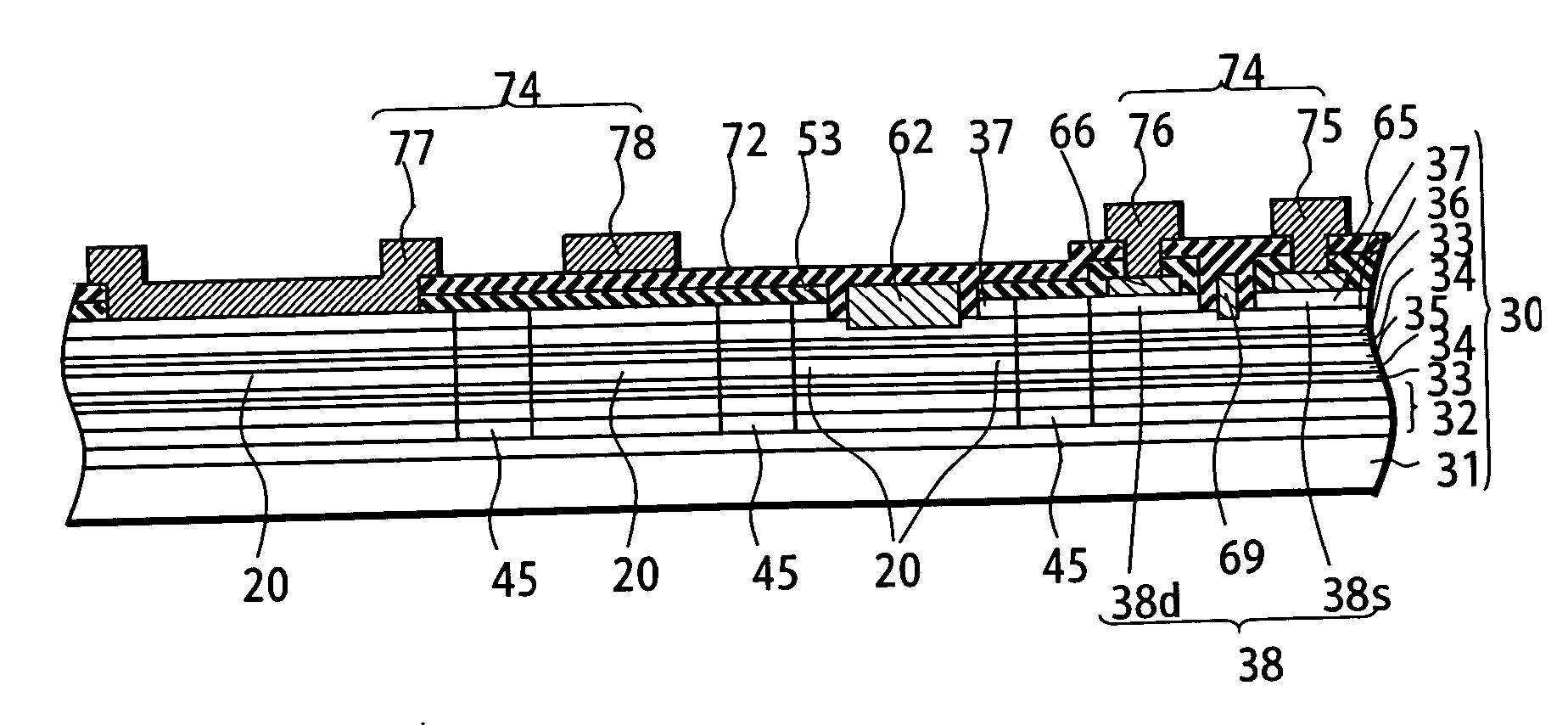

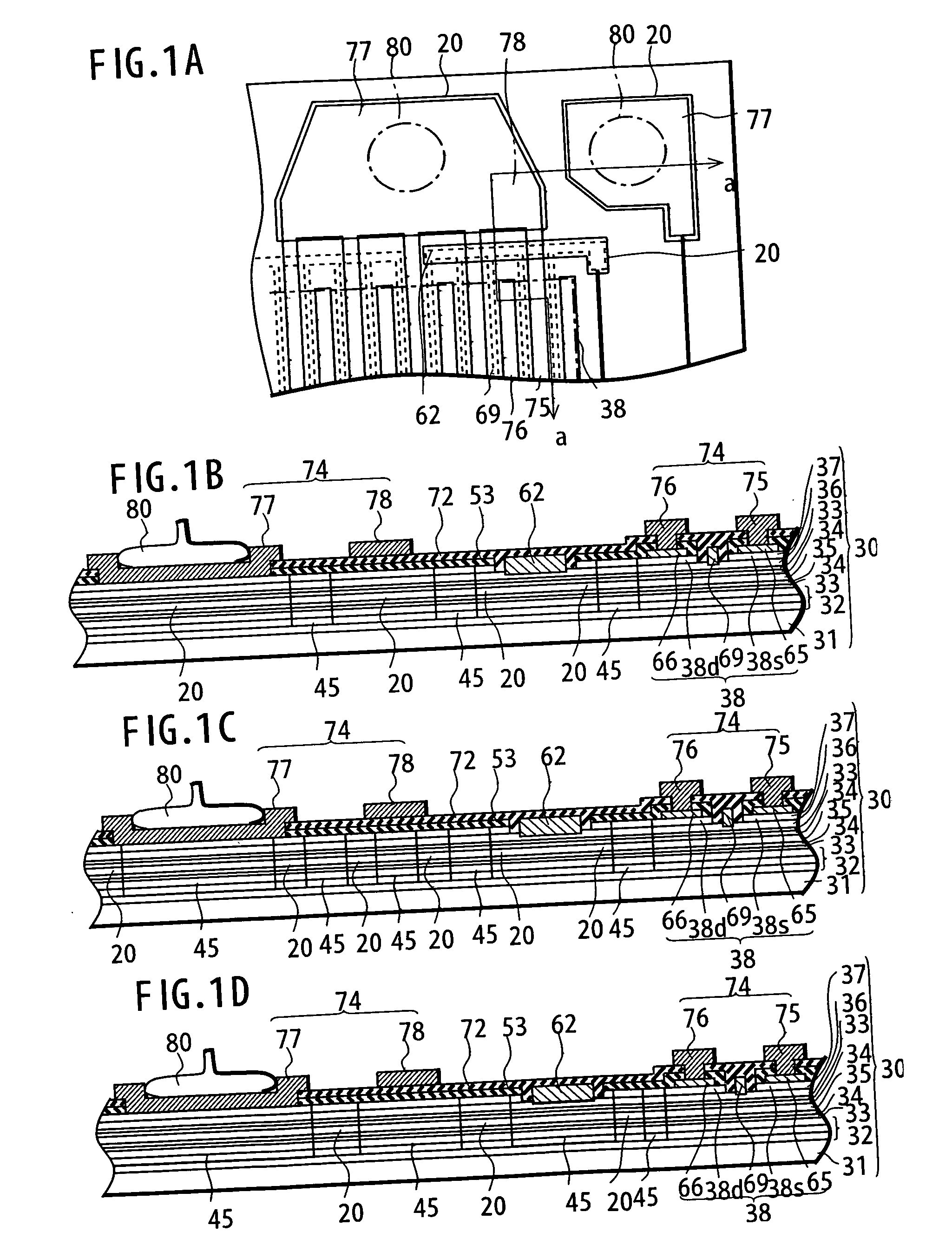

[0043]FIGS. 1A to 1D are views showing an example of a compound semiconductor device of the present invention, in which FIG. 1A is a plan view and FIG. 1B is a cross-sectional view taken along the a-a line. Here, the same formation elements as those in the conventional art are designated by the same reference numerals.

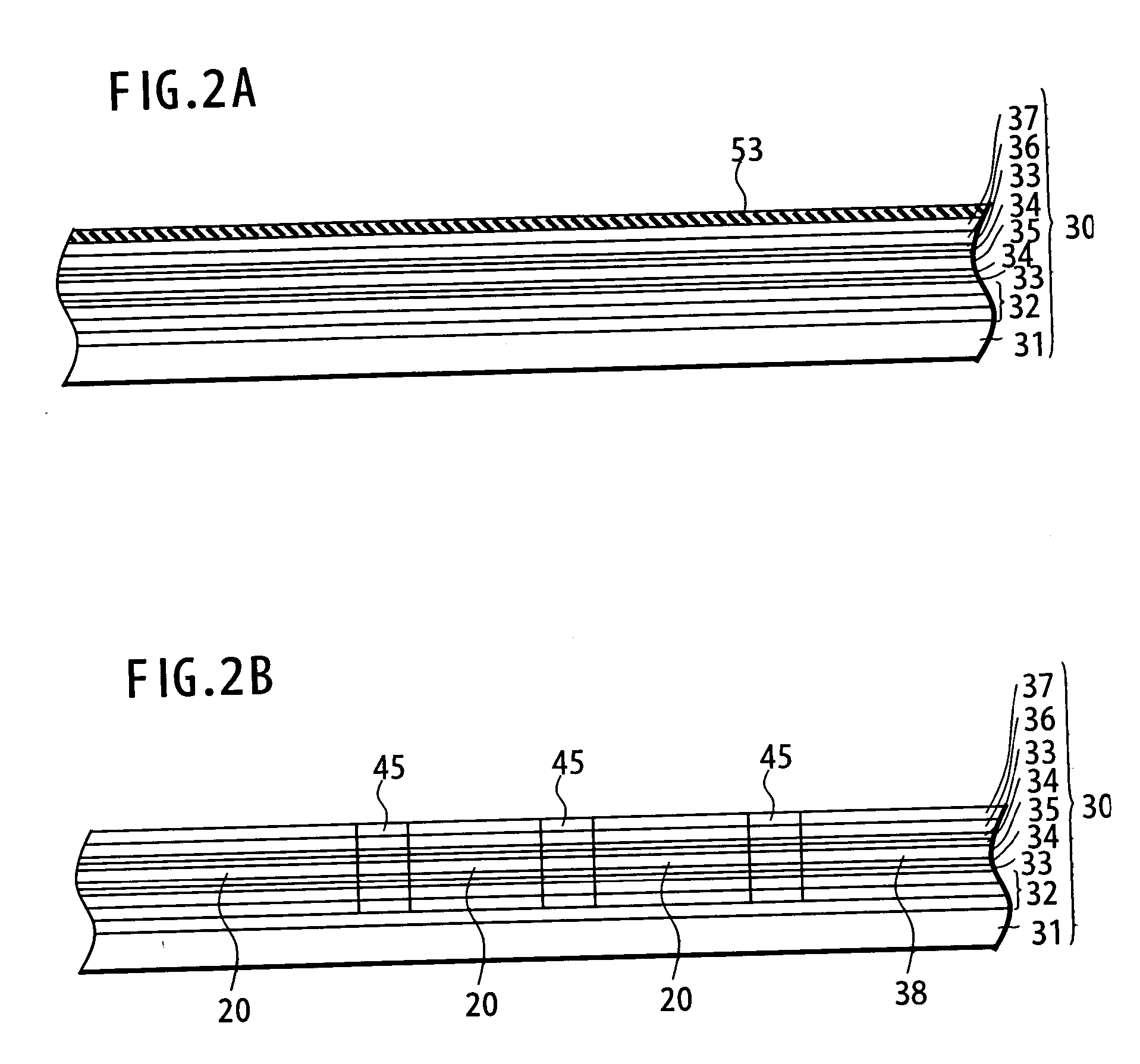

[0044] As shown in FIGS. 1A and 1B, concerning a method of forming substrate 30, first, undoped buffer layer 32 is grown on semi-insulating initial GaAs substrate 31. The buffer layer 32 is frequently formed as a plurality of layers. Then, n+-type AlGaAs layer 33 to be an electron supply layer, undoped InGaAs layer 35 to be an electron transimtting layer, and n+-type AlGaAs layer 33 to be another electron supply layer are sequentially grown on the buffer layer 32. Meanwhile, spacer layer 34 is disposed between the electron supply layer 33 and the electron transmitting layer 35.

[0045] Undoped AlGaAs layer 36 to be a barrier layer is grown on the electron supply layer 3...

second embodiment

[0111] That is, operating region 18 in the second embodiment is formed of source region 56 and drain region 57 formed by implanting ions of an n-type impurity (29Si+) into the n-type epitaxial layer 42, and of channel layer 52 between the both regions.

[0112] Then, ions of the n-type impurity (29Si+) are also implanted below the pad electrode 77, pad wiring 78, and gate wiring 62 to provide high concentration impurity region 60.

[0113] First source electrode 65 and first drain electrode 66 made of an ohmic metal layer 64 (AuGe / Ni / Au) of a first layer are provided on the source region 56 and the drain region 57.

[0114] Meanwhile, gate electrode 69 is provided by evaporating a gate metal layer (Pt / Mo) of a second metal layer to the channel layer 52. Moreover, second source electrode 75 and second drain electrode 76 made of pad metal layer 74 (Ti / Pt / Au) of a third metal layer are provided on the first source electrode 65 and the first drain electrode 66. Note that FIG. 6 shows one set o...

PUM

| Property | Measurement | Unit |

|---|---|---|

| distance | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| conducting | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More