Semiconductor device and method of manufacturing the same

a semiconductor and semiconductor technology, applied in the field of semiconductor devices, can solve the problems of insufficient performance of polycrystalline silicon transistors to form high-performance devices required for integrating systems, heat resistance, and limitations in the manufacturing process and device structure, and achieve the effects of no surface damage, easy formation, and uniform thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0047] The following will describe an embodiment of a semiconductor device of the present invention and a method of manufacturing the same.

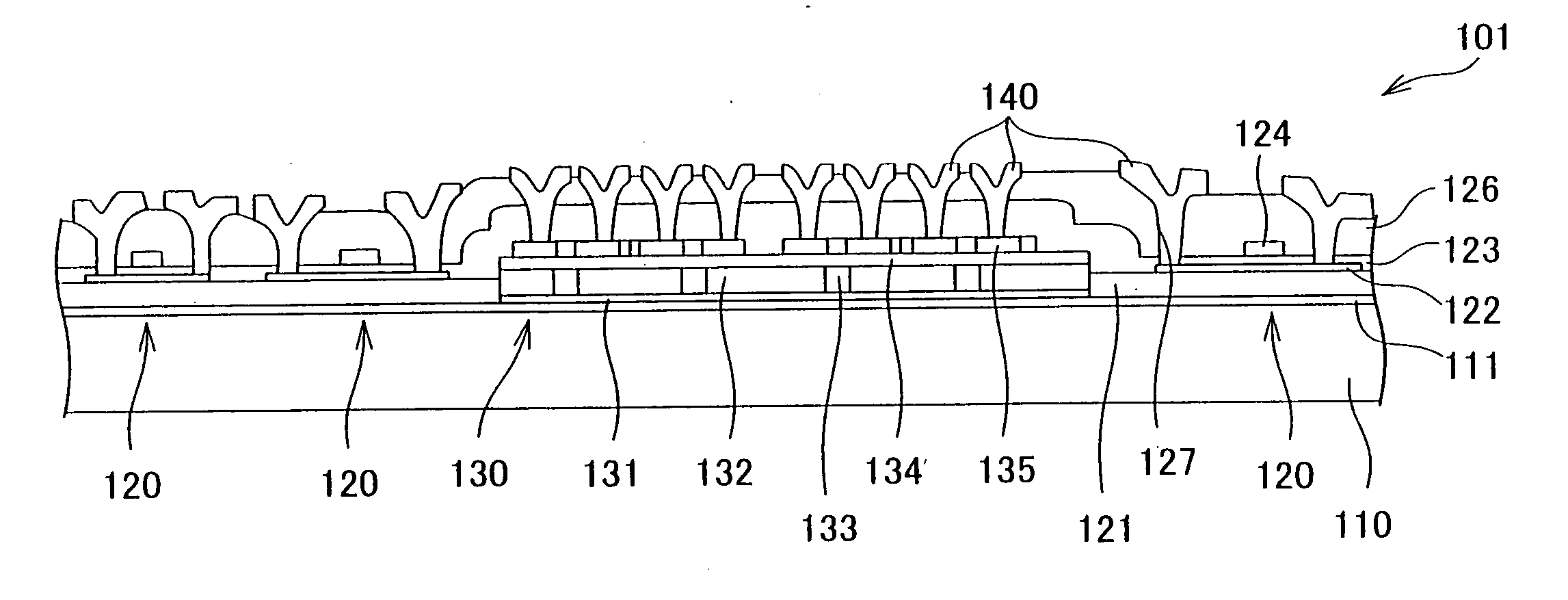

[0048] A semiconductor device 101 of the present embodiment is arranged in such a manner that a polycrystalline silicon thin-film transistor (non-single-crystal silicon thin-film transistor; non-single-crystal silicon thin-film device) 120 and a MOS (Metal Oxide Semiconductor) single-crystal silicon thin-film transistor (single-crystal silicon thin-film device) 130 are integrated on different regions on an insulating substrate. As FIG. 7 shows, the semiconductor device 101 can be further integrated, as a driving circuit 710, on an active matrix substrate 700 having a display section 720.

[0049] As illustrated in FIG. 8, the semiconductor device 101 is arranged so that, on an insulating substrate 110, an SiO2 (oxidized silicon) film (oxidized film) 111, the MOS polycrystalline silicon thin-film transistor 120 including a polycrystalline silicon t...

embodiment 2

[0102] The following will discuss another embodiment of a semiconductor device of the present invention and a manufacturing method thereof, with reference to figures. By the way, members having the same functions as those described in the semiconductor device 101 of Embodiment 1 are given the same numbers, so that the descriptions are omitted for the sake of convenience.

[0103] Being similar to the semiconductor device 101 of Embodiment 1, a semiconductor device 201 of the present embodiment is arranged in such a manner that a polycrystalline silicon thin-film transistor 120 and a MOS single-crystal silicon thin-film transistor 230 are integrated in different regions on an insulating substrate, and the device 201 is utilized for, for instance, an active matrix substrate. For this reason, the semiconductor device 201 is arranged identical with the semiconductor device 101 of Embodiment 1.

[0104] However, the semiconductor device 201 is different from the semiconductor device 101 of E...

embodiment 3

[0144] The following will describe a further embodiment of a semiconductor device of the present invention and a method of manufacturing the same. By the way, members having the same functions as those described in the semiconductor device 101 of Embodiment 1 are given the same numbers, so that the descriptions are omitted for the sake of convenience.

[0145] As shown in FIG. 10, a semiconductor device 301 of the present embodiment is identical with the semiconductor device 101 of Embodiment 1 to the extent that a single-crystal silicon thin film device and a non-single-crystal silicon thin film device are formed in different regions on an insulating substrate.

[0146] Note that, however, the semiconductor device 301 is different from the semiconductor device 101 of Embodiment 1 to the extent that the non-single-crystal silicon thin film device is formed from a continuous grain silicon thin film 322. The continuous grain silicon is polycrystalline silicon formed in such a way that, by...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More