However, due to relatively low solar

cell efficiencies (e.g., less than 12% for most thin-film technologies and roughly 12% to 18% for most

crystalline silicon solar

cell technologies), high costs of raw materials (e.g.,

silicon for

crystalline silicon wafer solar cells) and manufacturing processes, limitations on cost-effective and efficient electrical storage, and a general lack of infrastructure to support solar

cell proliferation, to date there has been limited use of this energy solution (currently,

electricity generation by solar

photovoltaics accounts for less than 0.1% of total worldwide

electricity generation).

Crystalline silicon wafers offer higher performance, but at higher costs (due to the relatively high cost of starting monocrystalline and multicrystalline

silicon wafers).

Thin-film technologies may offer lower manufacturing costs, but typically at lower performance levels (i.e., lower efficiencies).

For both approaches, the price-per-

watt typically increases as cell efficiencies rise (due to higher material and / or manufacturing costs).

Due to a rapid

annual growth rate of more than 40% during the past ten years and the concurrent demands for

silicon material by both

semiconductor microelectronics and solar PV industries, the solar PV industry has been experiencing a shortage of polysilicon feedstock supply.

The polysilicon feedstock shortage has significantly constrained the solar PV industry growth, particularly during the past several years.

In fact, the solar cell industry currently consumes over half of the worldwide production of high-purity polysilicon feedstock.

This has led to large increases in the price of monocrystalline and multicrystalline silicon wafers, which now account for roughly half of the total

solar module manufacturing cost.

This

wafer thickness reduction, however, presents additional challenges related to mechanical rigidity, manufacturing yield, and

solar cell efficiency.

While very-high-volume solar fabs in the range of 100 MWp to 1 GWp should facilitate longer term cost reductions (including LCOE) through high-volume manufacturing economies of scale, the relatively high initial fab investment costs, which may easily exceed $100M, may impose certain limits on solar photovoltaic fab construction options.

TFSCs typically offer low cost, reduced module weight, reduced materials consumption, and a capability for using flexible substrates, but are usually much lower in efficiency (e.g., usually 5% to 12%).

In the case of prior art thin

crystalline silicon films, there are a number of major problems and challenges with the use of flat silicon films (such as epitaxially growth silicon films with thicknesses below 50 microns) for low-cost, high-performance solar cells.

These include: relatively low

solar module efficiencies (typically 7% to 12%), field degradation of module efficiencies, scarce and expensive absorber materials (e.g., In and Se for CIGS and Te for CdTe), limited validation of

system field reliability, and adverse environmental

impact of non-silicon technologies such as CIS / CIGS and CdTe.

With regard to the prior art crystalline silicon (c-Si) thin-film solar cell (TFSC) technology, there are difficulties associated with sufficient surface texturing of the thin silicon film to reduce surface reflectance losses, while reducing the crystalline silicon film thickness.

This places a limit on the minimum flat (co-planar)

monocrystalline silicon thickness due to production yield and cell performance (efficiency) considerations.

In the case of a flat or co-planar film, it is essential to use surface texturing since the reflectance of an untextured crystalline silicon film is quite excessive (can be greater than 30%) and results in substantial

optical reflection losses and degradation of the external

quantum efficiency.

In addition, substantially reduced mean

optical path lengths in thin planar crystalline silicon films result in reduced

photon absorption, particularly for photons with energies near the

infrared bandgap of silicon (800 to 1100 nanometers), resulting in reduced solar cell

quantum efficiency (reduced short-circuit current or Jsc).

The back reflectance provided by these techniques may not be great (e.g., roughly 70% effective near-IR rear reflectance), constraining the performance

gain that would have otherwise been achieved by an optimal

back reflector.

The problem with this approach is that the primary

incident beam always passes the crystalline silicon film only once.

There is also the problem of lack of rigidity and mechanical support of the thin film during cell and module

processing steps.

This problem relates to the

mechanical strength of a large-area (e.g., 200 mm×200 mm) thin silicon film.

It is well known that reducing the large-area crystalline silicon

wafer thickness to below 100 microns results in a substantial loss of TFSC substrate

mechanical strength / rigidity, and such thin wafers tend to be flexible and very difficult to

handle without breakage during

cell fabrication process flow.

One approach is to grow and retain the thin epitaxial film on a relatively low-cost (e.g., metallurgical-grade) silicon substrate (over which the epitaxial layer is grown); however, this approach suffers from some inherent problems constraining the ultimate

solar cell efficiency.

This approach may suffer from any

thermal coefficient of expansion (TCE) mismatch between the support /

handle substrate and silicon film during any high-temperature oxidation and anneal processes, as well as potential

contamination of the thin

epitaxial silicon film from the non-silicon support substrate (both creating possible manufacturing yield and performance / efficiency degradation problems).

However, this would present various challenges for fabrication of planar silicon thin-film solar cells.

As stated, thinner co-planar (flat) epitaxial films (e.g., in the range of much less than 30 microns) produce a number of problems and challenges, including a lack of film

mechanical strength, constraints limiting

effective surface texturing of thin silicon films for low surface reflectance and reduced

optical reflectance losses, relatively short

optical path lengths, and reduced cell quantum efficiencies.

This is very difficult to achieve in the co-planar (flat) c-Si thin film solar cells.

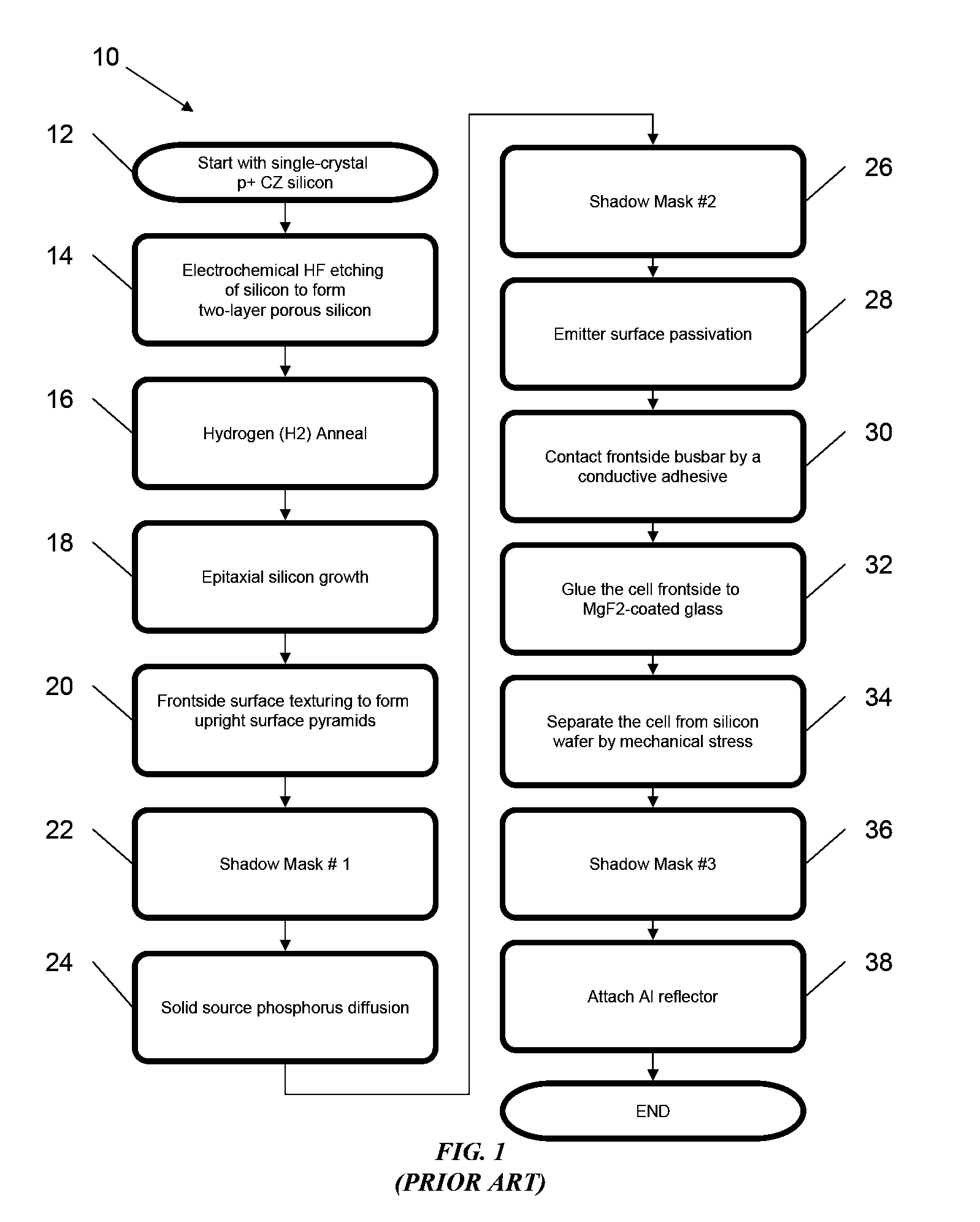

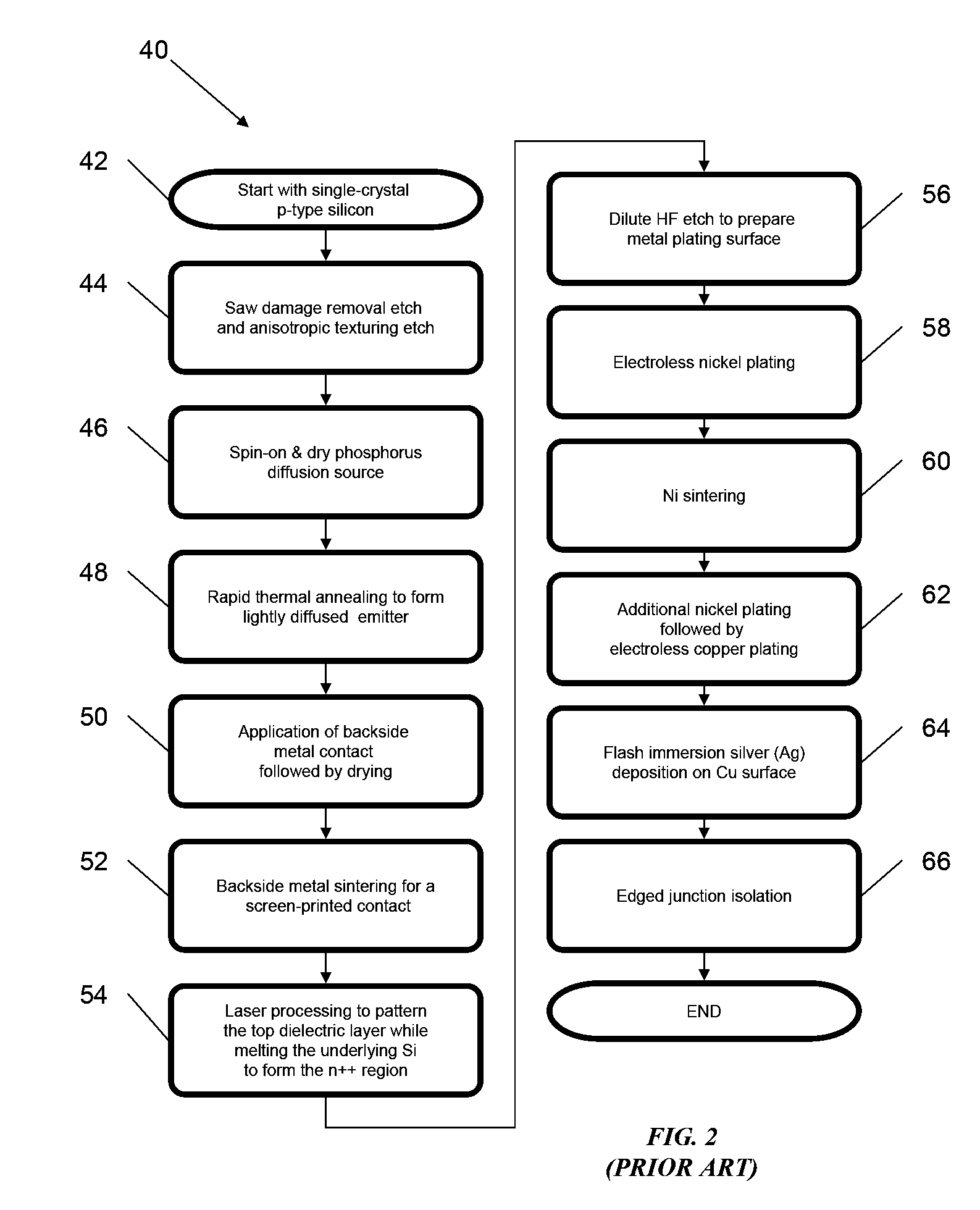

The use of

photolithography and / or

screen printing and / or shadow-

mask deposition patterning steps usually increases the manufacturing process flow complexity and cost, and may also detrimentally

impact the fabrication yield as well as the ultimate achievable solar cell efficiency.

This includes the problem of lack of rigidity and mechanical support of the thin film substrate during cell and module

processing steps, thus, necessitating the use of support or

handle substrates (made of silicon or another material) for the TFSC substrates.

This further includes the cost of the

epitaxial silicon film growth process, particularly for thicker epitaxial films required for planar crystalline silicon TFSCs.

This further includes the requirement of multiple

photolithography and / or

screen printing and / or shadow-

mask processing / patterning steps which usually increase the manufacturing process flow complexity and cost, and may also detrimentally

impact the fabrication yield as well as the ultimate achievable solar cell efficiency.

Login to View More

Login to View More  Login to View More

Login to View More