Formation of nanoscale wires

a nano-scale wire and wire technology, applied in the direction of polycrystalline material growth, crystal growth process, chemically reactive gas, etc., can solve the problems of irregular shape and size, difficult to achieve, and wire-like structur

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

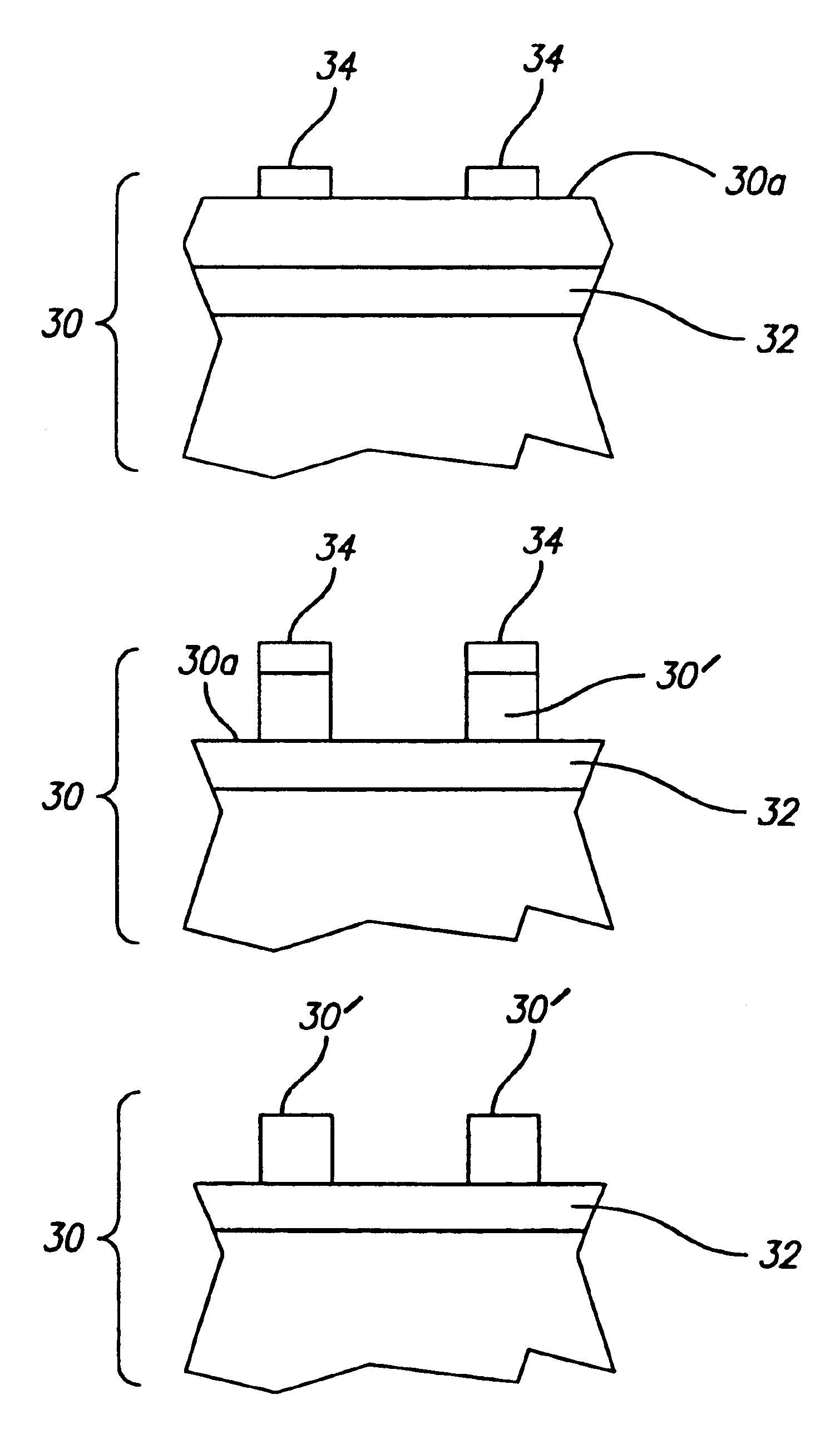

Image

Examples

example 1

Growth of ErSi.sub.2 on Si.

The following example demonstrates that by utilizing an epitaxial overlayer that has a carefully chosen lattice mismatch to complement the host substrate, in this case erbium disilicide (ErSi.sub.2) on Si(001), it is possible to grow nanowires. Due to its high conductivity (2.9.times.10.sup.4 (.OMEGA.cm).sup.-1) and low Schottky barrier to n-type Si, ErSi.sub.2 thin films grown on Si substrates have been studied extensively. These studies involved continuous thin films on Si(001) that were several nanometers thick, and they revealed oriented crystallites with a hexagonal AlB.sub.2 -type crystal structure that were thermodynamically stable in contact with Si below 800.degree. C. The [0001] axis of the ErSi.sub.2 was oriented along a (110) axis of the Si(001) substrate, and the [1120] of the ErSi.sub.2 was oriented along the perpendicular (110) axis, with lattice mismatches of +6.5% and -1.3%, respectively, which nearly satisfies the proposed growth conditio...

example 2

Growth of EtSi.sub.2, ScSi.sub.2, DvSi.sub.2, and GdSi.sub.2 on Si and Their Comparison.

In the following experiments, device quality "flat" Si(001) substrates were prepared as in Example 1.

As measured from STM images, the average terrace widths along [110].sub.Si and [110].sub.Si were 57.8 nm and 21.3 nm, respectively, implying that the normal direction of the surface of the Si substrate used in these experiments was misoriented from [001].sub.Si toward [120].sub.Si by about 0.4.degree..

The final state of the nanowires was influenced by their growth conditions, such as deposition and annealing temperature, deposition rate, coverage of deposited atoms, and annealing time. The physical properties of Sc, Er, Dy, and Gd are similar (e.g., their melting points are 1539.degree. C., 1522.degree. C., 1409.degree. C., and 1314.degree. C. respectively), and the experimentally-determined growth conditions for producing dislocation-free nanowires are also very close. The optimum substrate tempe...

example 3

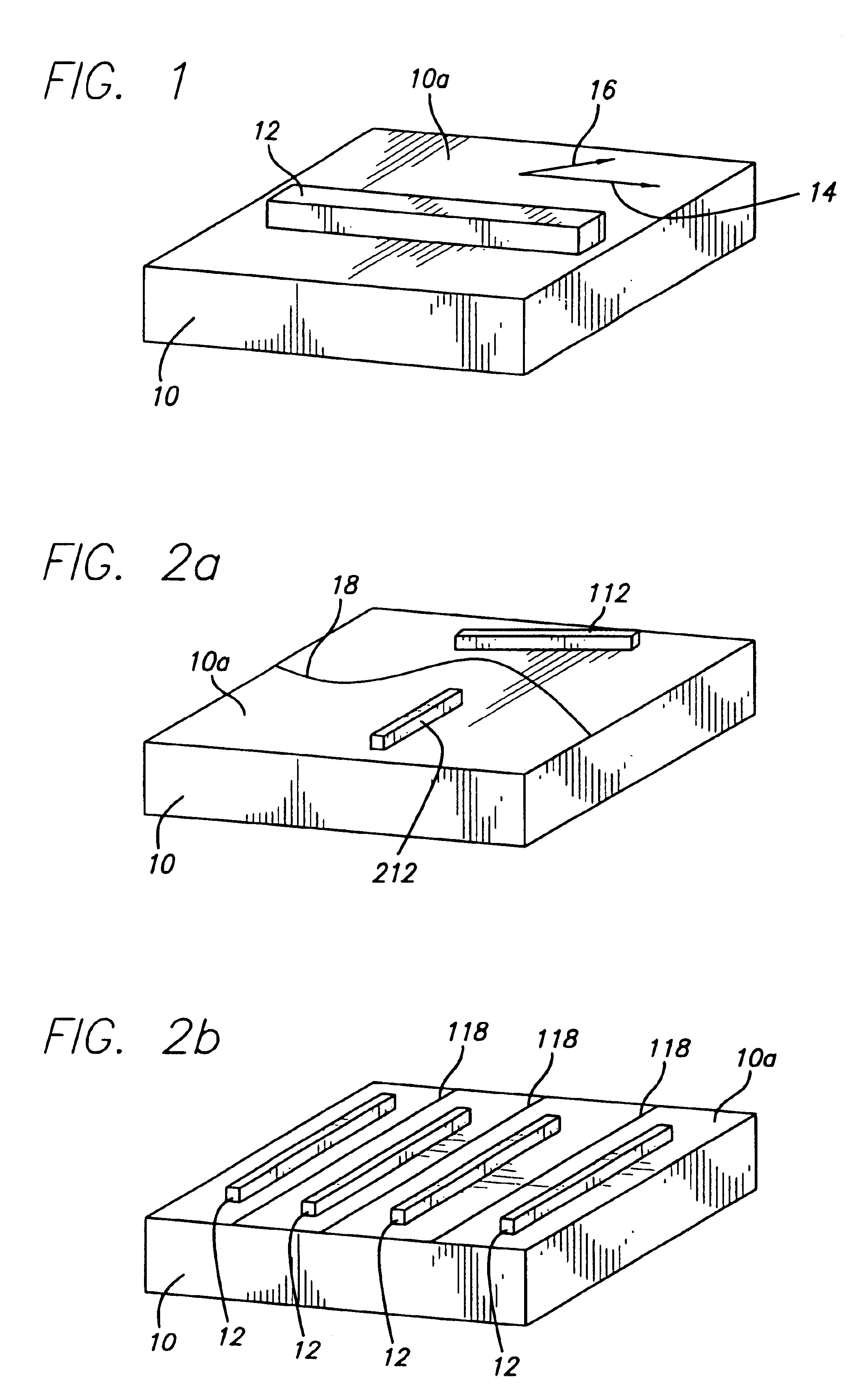

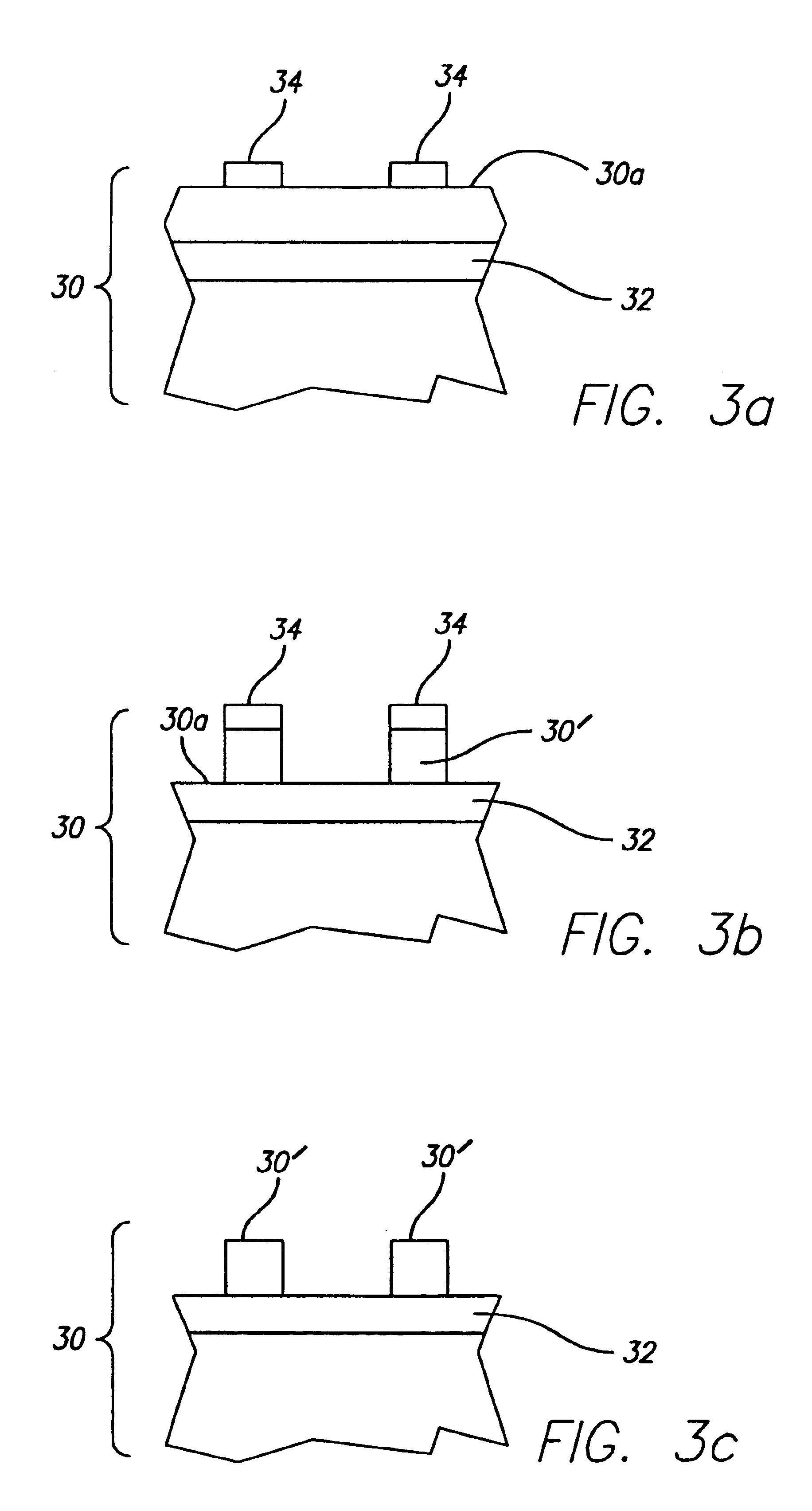

Patterning Silicon to Form Silicon Nanowires.

ErSi.sub.2 nanowires, about 1 nm thick, were grown on a Si(001) substrate, as described in Example 1. FIG. 6a is a scanning electron microscope (SEM) image of the ErSi.sub.2 self-assembled nanowires grown on the Si substrate. The ErSi.sub.2 lines appear to be weaker in FIG. 6a than the Si lines in FIG. 6b, due to the fact that the ErSi.sub.2 wires are less than 1 mm and their interaction with the e-beam in the SEM are very weak.

Using the ErSi.sub.2 nanowires as a mask, the silicon was anisotropically etched away in the area without the coverage of the ErSi.sub.2 nanowires. The etching was carried out by RIE for 5 minutes in CF.sub.4, SF.sub.6, and Ar gases with their flowing rates as CF.sub.4 :SF.sub.6 :Ar=25 sccm:125 sccm:60 sccm, at a pressure of 50 mTorr and a power of 100 W. ErSi.sub.2 was subsequently removed from the tops of the Si nanowires, using HF. The resulting silicon nanowires were about 9 nm in height. FIG. 6b is an SEM imag...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Angle | aaaaa | aaaaa |

| Angle | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More