Method of manufacturing SOI substrate

a technology of soi substrate and manufacturing method, which is applied in the direction of semiconductor/solid-state device manufacturing, basic electric elements, electric apparatus, etc., can solve the problem of preventing productivity improvement, and achieve the effect of efficient reprocessing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

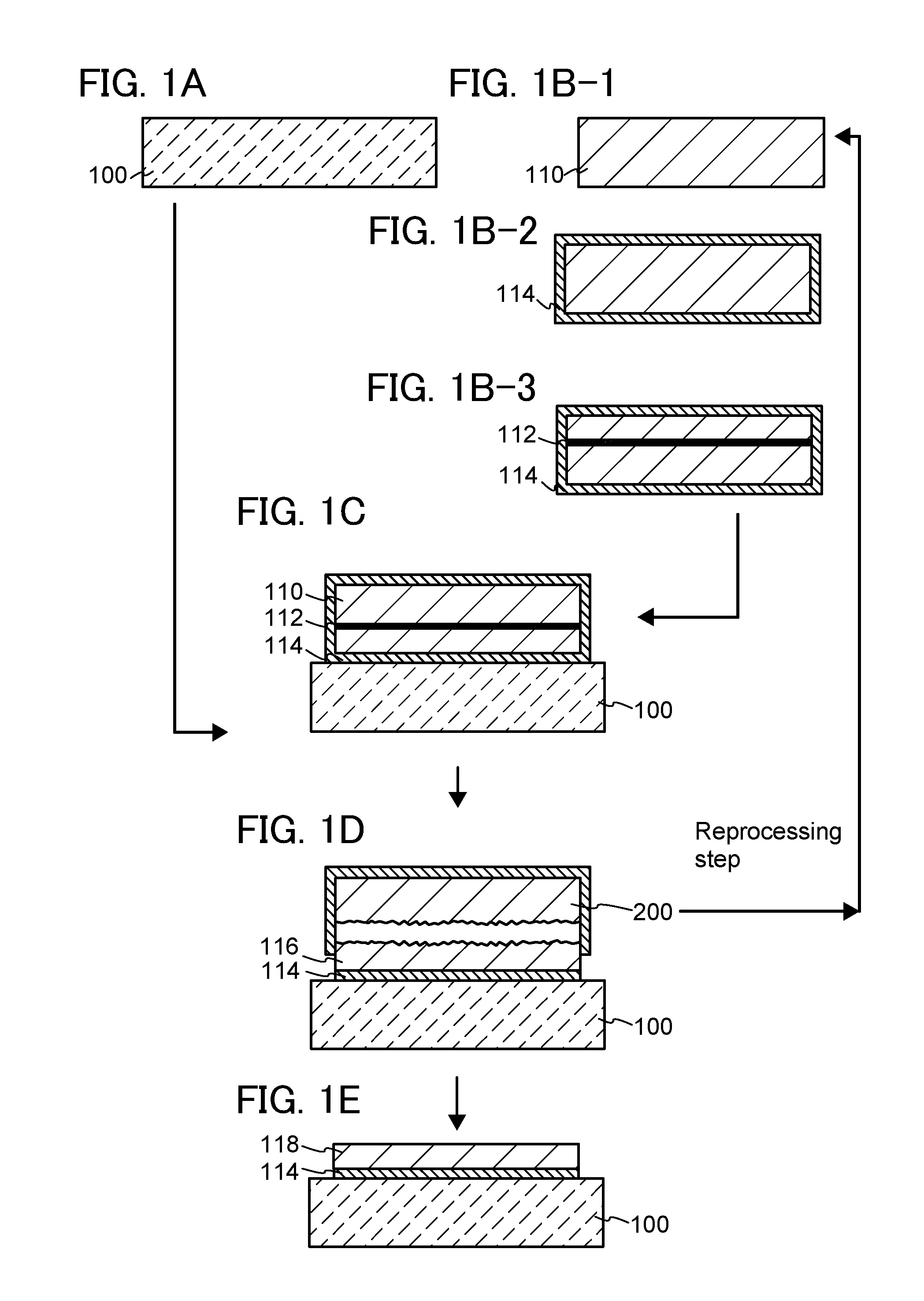

[0030]In this embodiment, an example of a method for manufacturing an SOI substrate is described with reference to FIGS. 1A, 1B-1 to 1B-3, 1C, 1D, and 1E and FIG. 2.

[0031]First, a base substrate 100 is prepared (see FIG. 1A). As the base substrate 100, it is possible to use a light-transmitting glass substrate used for a liquid crystal display device or the like. As the glass substrate, a substrate having a strain point of 580° C. or higher (preferably 600° C. or higher) may preferably be used. Further, the glass substrate is preferably a non-alkali glass substrate. The non-alkali glass substrate is formed using a glass material such as aluminosilicate glass, aluminoborosilicate glass, or barium borosilicate glass, for instance.

[0032]Note that as the base substrate 100, it is possible to use an insulating substrate such as a ceramic substrate, a quartz substrate, or a sapphire substrate, a substrate formed of a semiconductor such as silicon, a substrate formed of a conductor such as...

embodiment 2

[0075]In this embodiment, another example of a manufacturing method of an SOI substrate is described with reference to FIGS. 3A-1, 3A-2, 3B-1 to 3B-3, 3C, 3D, and 3E. This embodiment is different from Embodiment 1 in that an insulating layer 101 is formed over a base substrate. Therefore, this point is mainly described below.

[0076]First, the base substrate 100 is prepared (see FIG. 3A-1), and the insulating layer 101 is formed over the base substrate (see FIG. 3A-2). Refer to FIG. 1A for the base substrate 100.

[0077]There is no particular limitation on the method for forming the insulating layer 101, to which a sputtering method, a plasma CVD method, or the like can be applied, for example. Since the insulating layer 101 has a surface for bond, the insulating layer 101 is preferably formed such that this surface has high planarity. The insulating layer 101 can be formed using one or more materials selected from a silicon oxide, a silicon nitride, a silicon oxynitride, a silicon nitr...

embodiment 3

[0098]In this embodiment, a manufacturing method of a semiconductor device using the SOI substrate according to the aforementioned embodiment will be described with reference to FIGS. 4A to 4E and FIGS. 5A to 5D. In this embodiment, a manufacturing method of a semiconductor device including a plurality of transistors will be described as an example of the semiconductor device. Various semiconductor devices can be formed with the use of transistors described below in combination.

[0099]FIG. 4A is a cross-sectional view illustrating a part of the SOI substrate manufactured using the method described in aforementioned embodiment.

[0100]The semiconductor layer 118 corresponds to the semiconductor layer 118 in FIG. 3E and has a surface whose planarity is improved.

[0101]In order to control the threshold voltage of the transistor, a p-type impurity element such as boron, aluminum, or gallium, or an n-type impurity element such as phosphorus or arsenic may be added to the semiconductor layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More