Patents

Literature

34results about How to "Phase detection error is small" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Phase-locked loop applicable to power grid voltage unbalance and distortion states

ActiveCN105743109AGuaranteed Steady State PerformanceFast dynamic responseVoltage-current phase anglePolyphase network asymmetry elimination/reductionCompensation effectIntegral controller

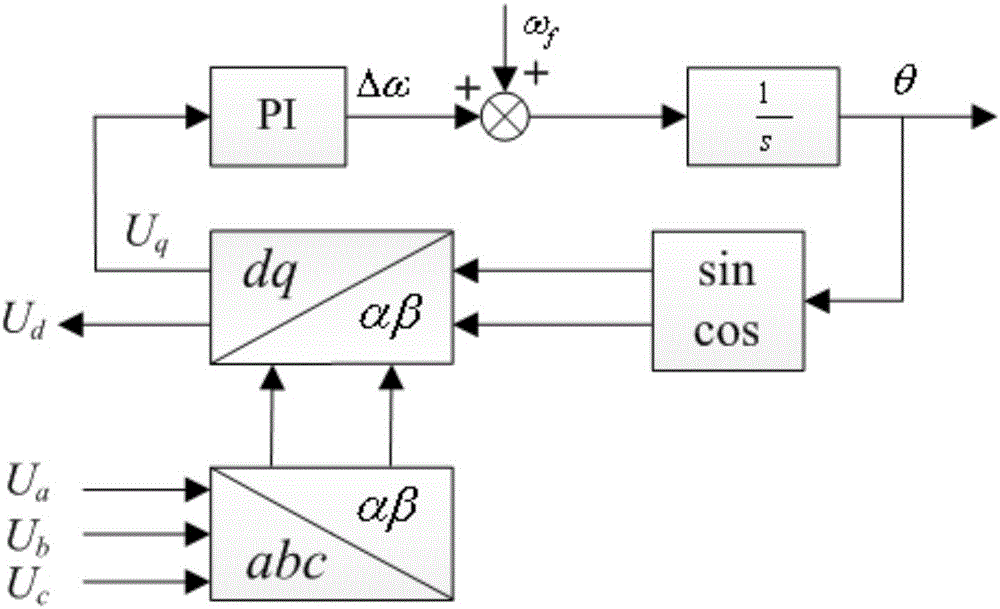

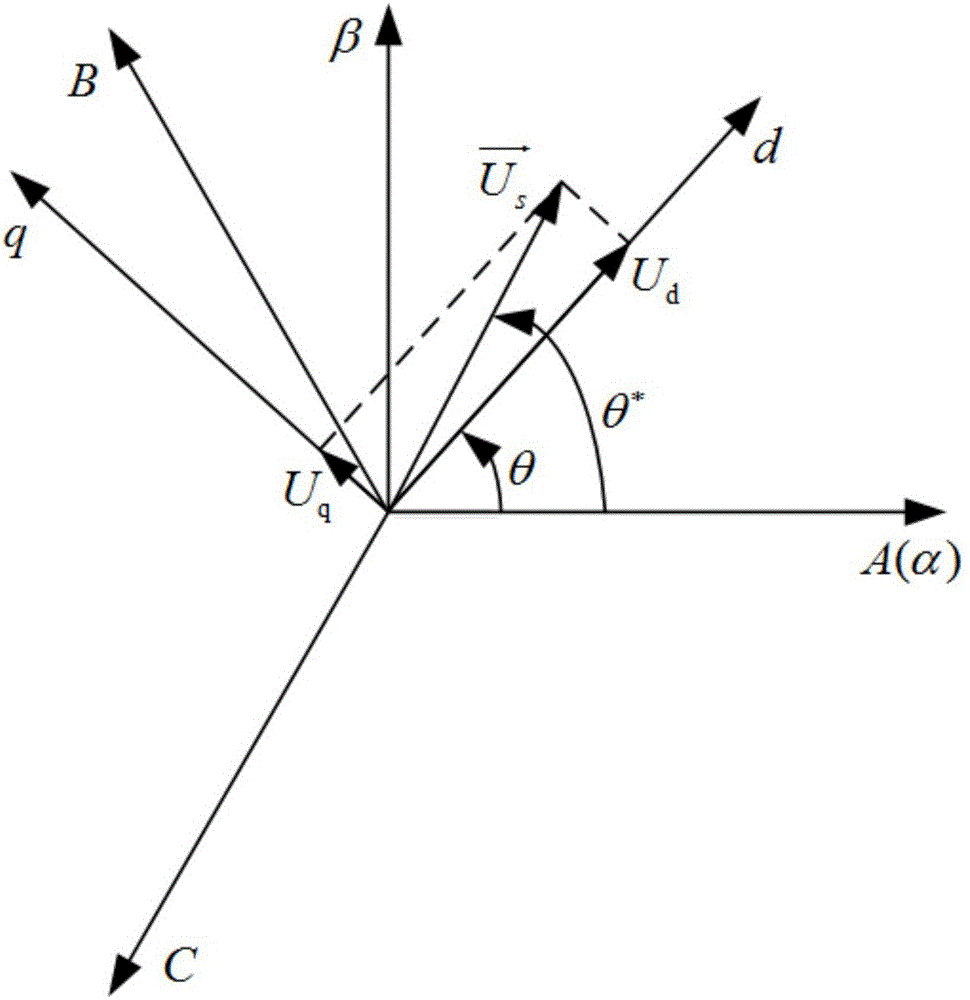

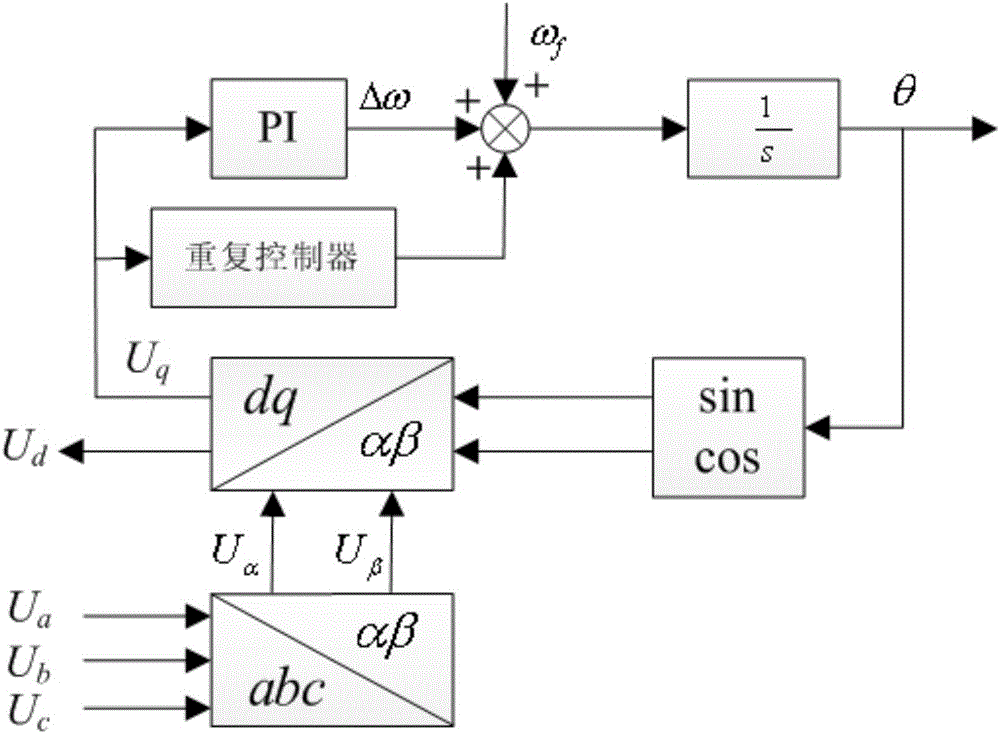

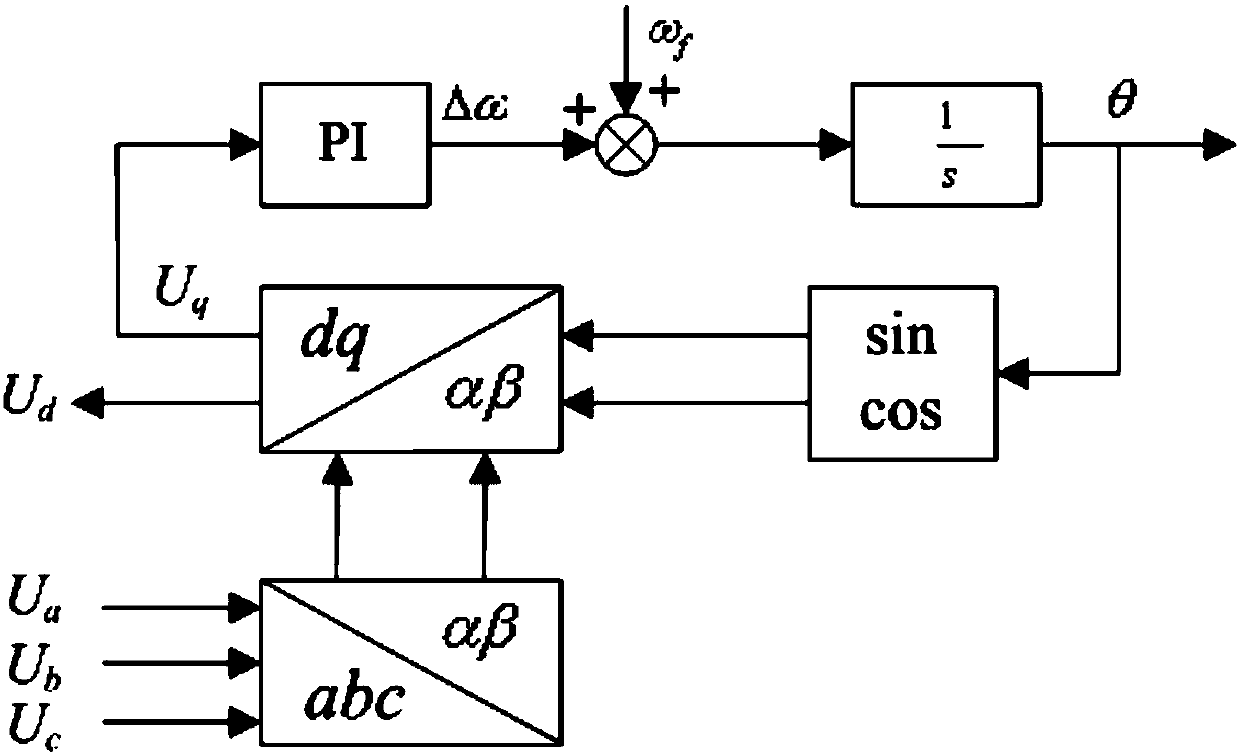

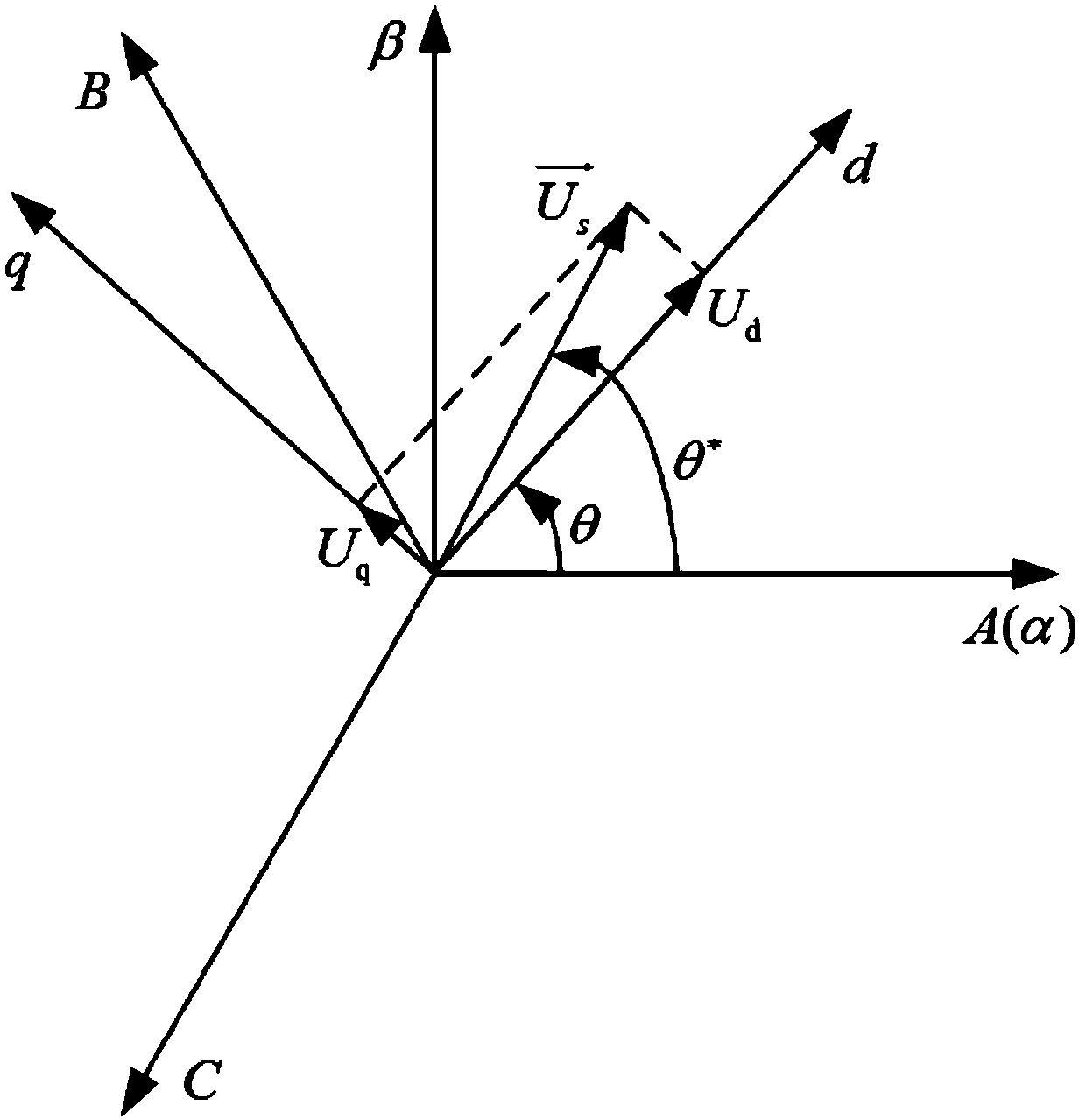

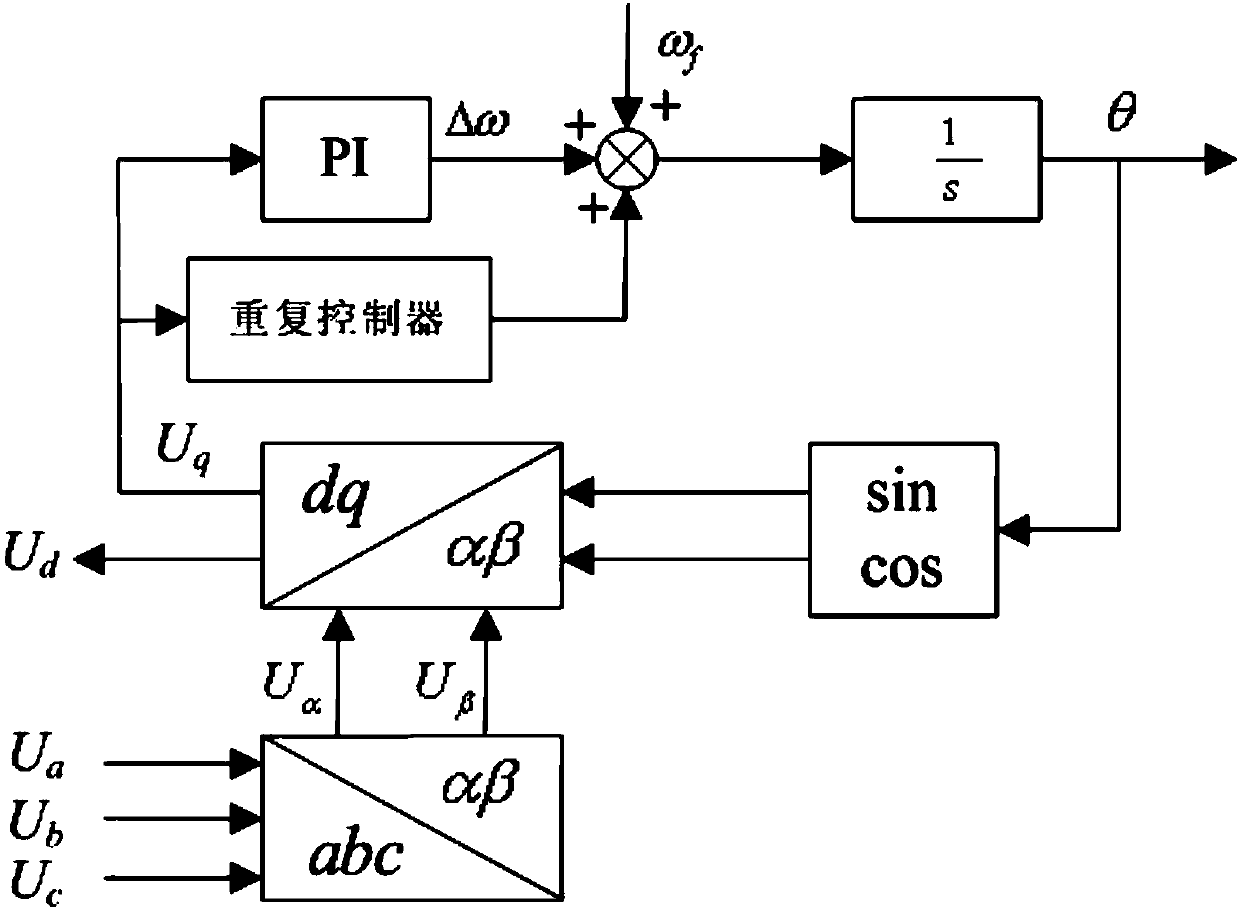

The invention discloses a phase-locked loop applicable to power grid voltage unbalance and distortion states, and belongs to the related technical fields of power grid voltage phase signal detection and power grid load harmonic current extraction. The phase-locked loop provided by the invention aims to solve the problem as follows: the conventional synchronous rotating reference frame based three-phase digital phase-locked loop cannot accurately detect the phase value of the three-phase voltage fundamental wave positive-sequence component under power grid voltage unbalance and distortion states; consequently, the precision of a related harmonic current extraction algorithm is lowered, and the compensation effect of a harmonic compensation apparatus is weakened. The phase-locked loop provided by the invention improves the conventional three-phase digital phase-locked loop, and a repetition controller is introduced; the repetition controller is connected with a proportional integral controller in parallel to form a new controller, so that the excellent steady-state performance of the repetition controller is combined with the excellent dynamic performance of the proportional integral controller; and therefore, the phase-locked loop has the advantages of high dynamic response, high detection precision and the like. The phase-locked loop is mainly applied to voltage phase detection under power grid voltage unbalance and distortion states.

Owner:DALIAN UNIV OF TECH

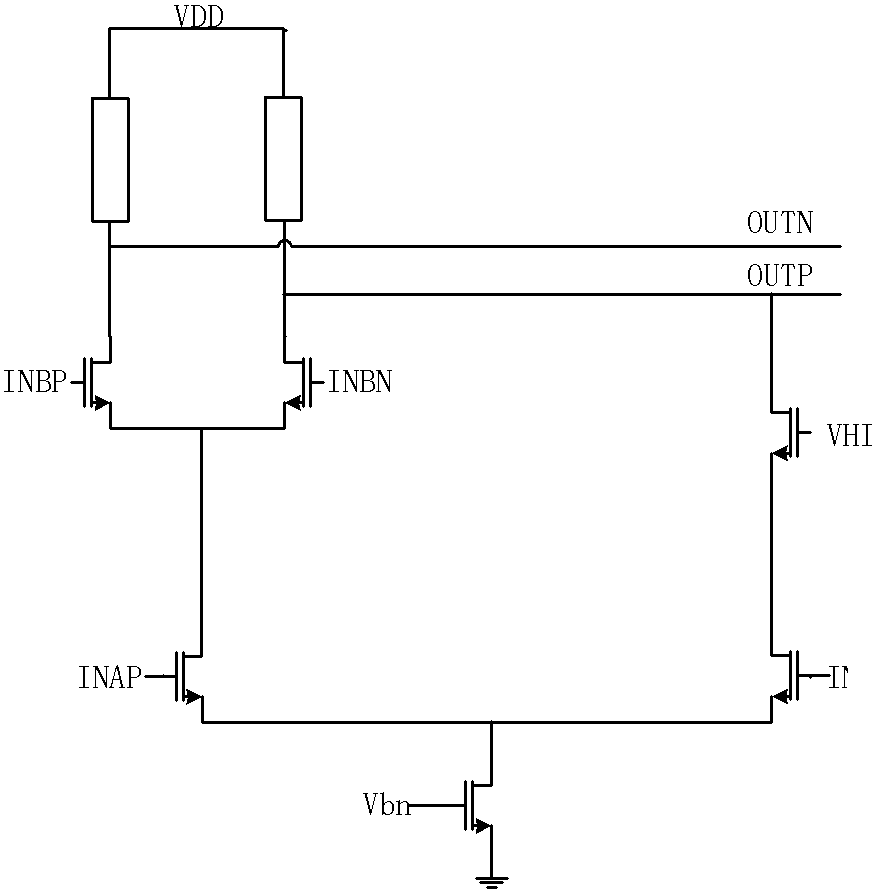

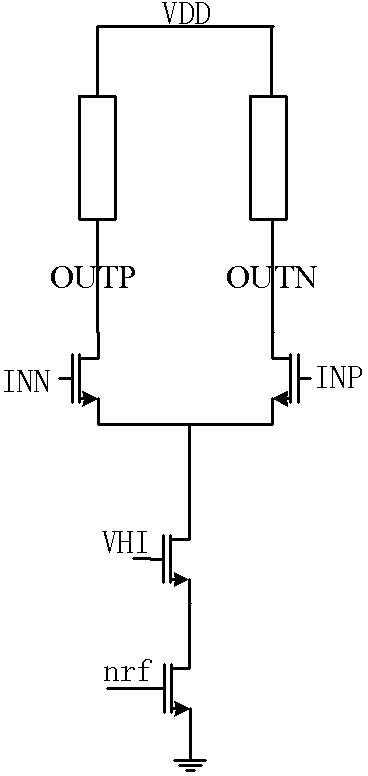

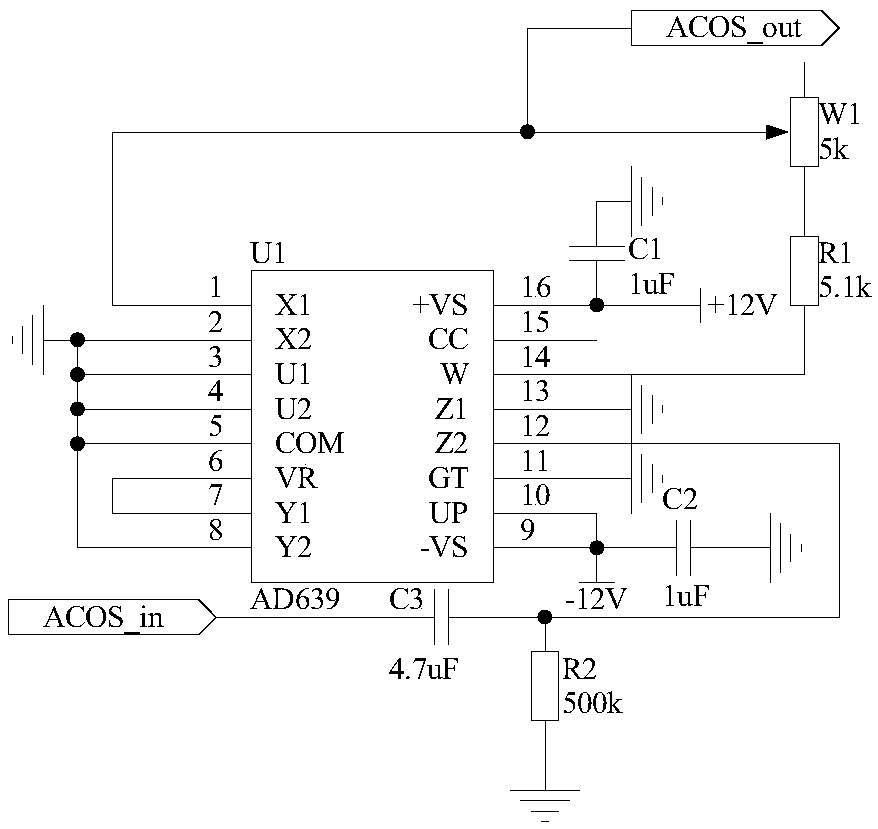

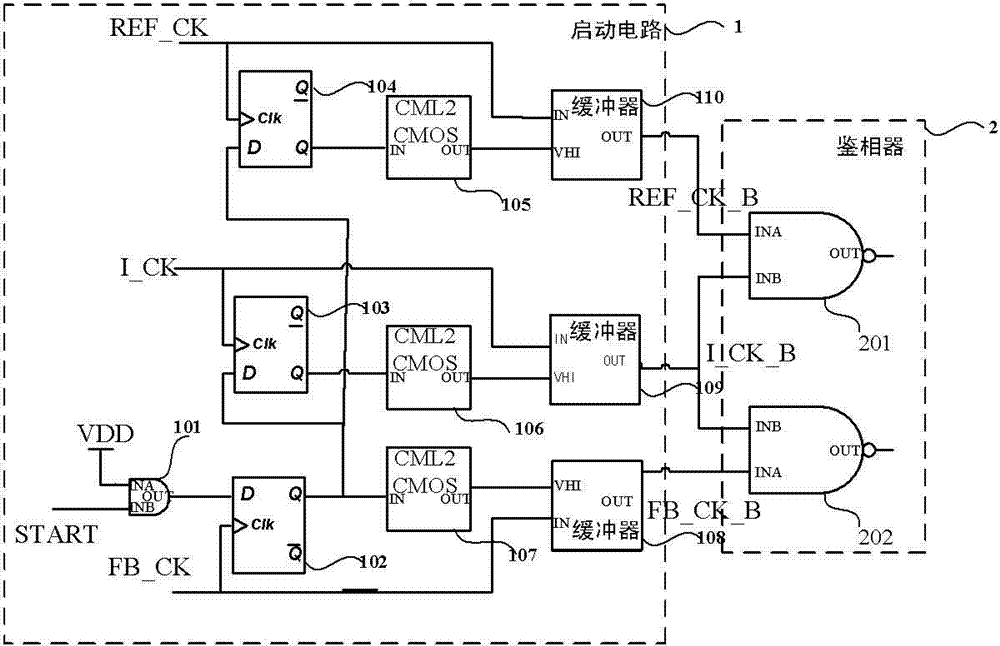

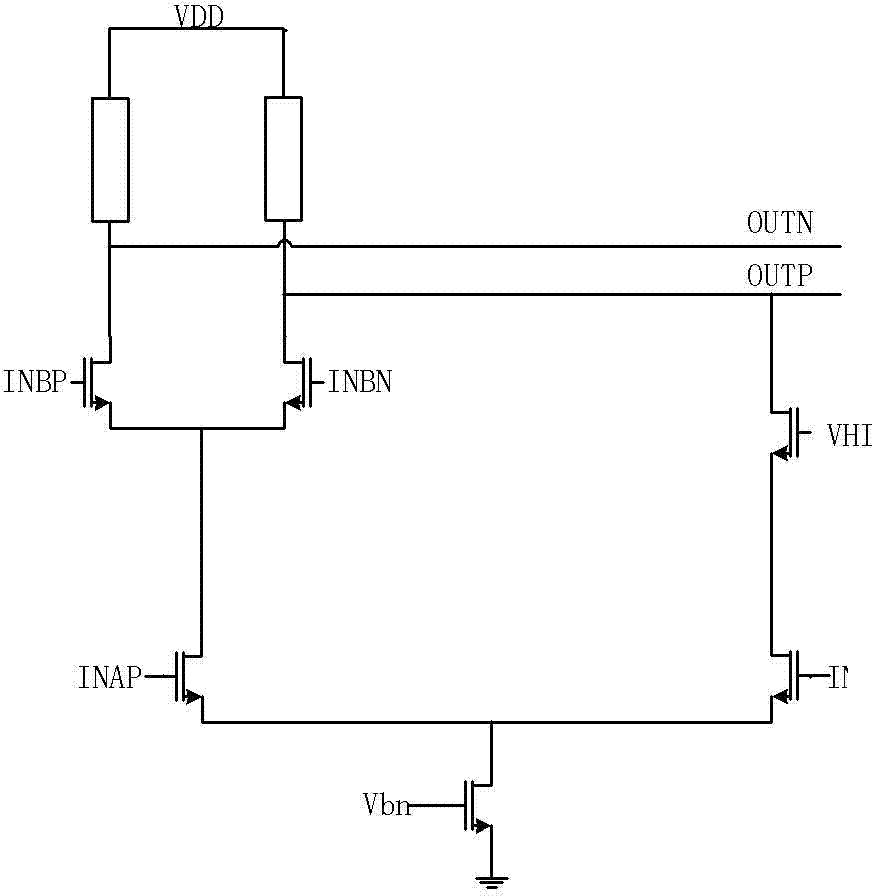

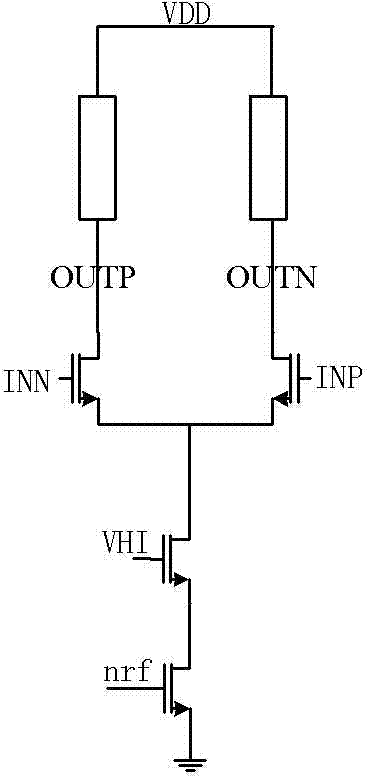

Phase detection and starting circuit used in multiphase clock generating circuit of high-speed serial interface

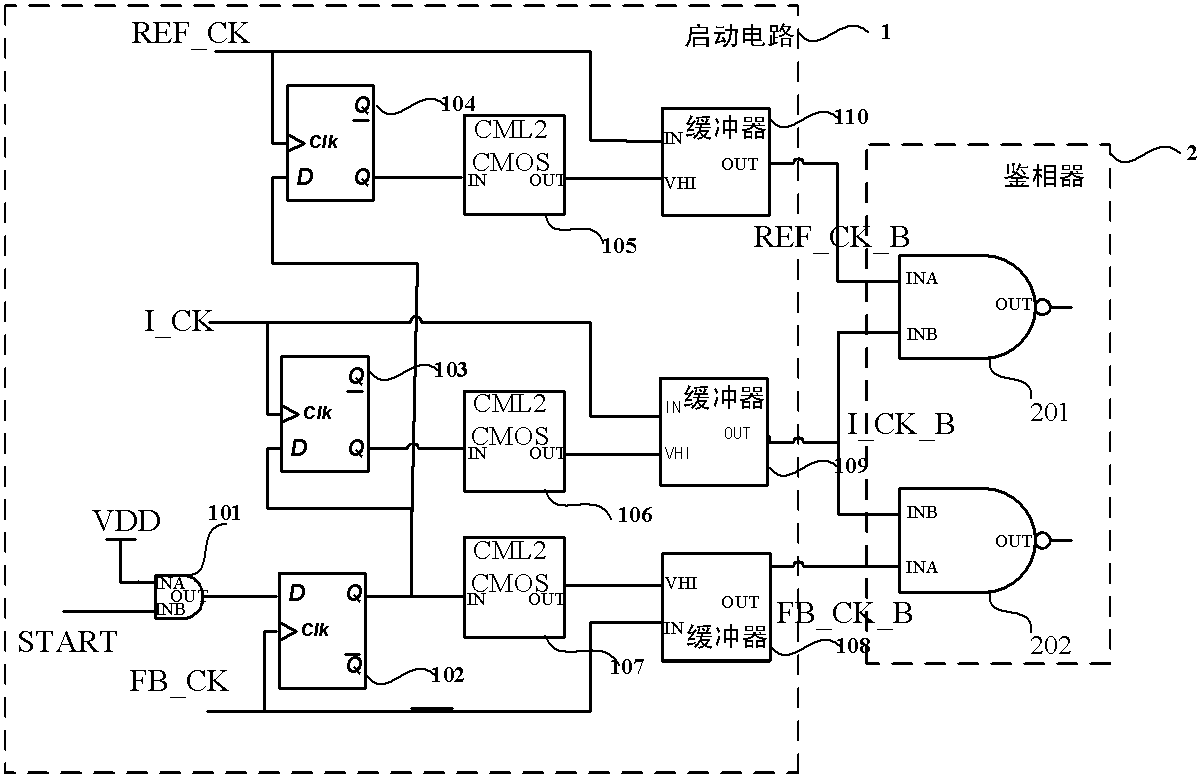

A phase detection and starting circuit used in a multiphase clock generating circuit of a high-speed serial interface comprises a phase detector and a starting circuit, wherein the phase detector is provided with three input ends and two output ends, the starting circuit is connected with the input end of the phase detector, and the starting circuit comprises an AND gate, a first D trigger, a second D trigger, a third D trigger, a first CML2CMOS circuit, a second CML2CMOS circuit, a third CML2CMOS circuit, a first buffer, a second buffer and a third buffer. The circuit controls initial states of clock signals entering the phase detector when the multiphase clock generating circuit starts working, so that the wrong locking and the harmonic locking of the multiphase clock generating circuit can be effectively prevented, the phase detector adopts the current mode logic technology, the working efficiency is high, and the incoming mismatching jittering is low.

Owner:SHENZHEN GRADUATE SCHOOL TSINGHUA UNIV

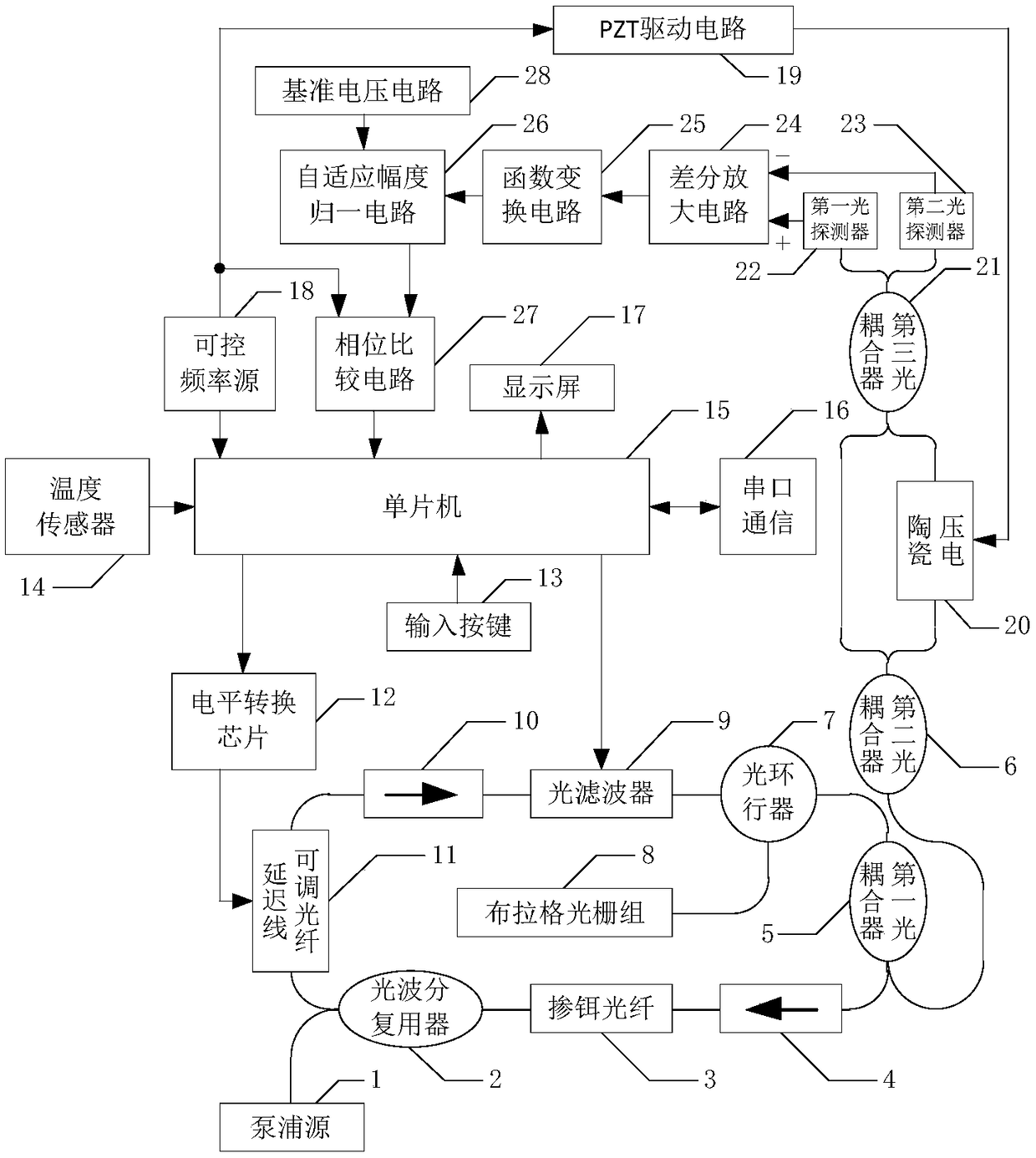

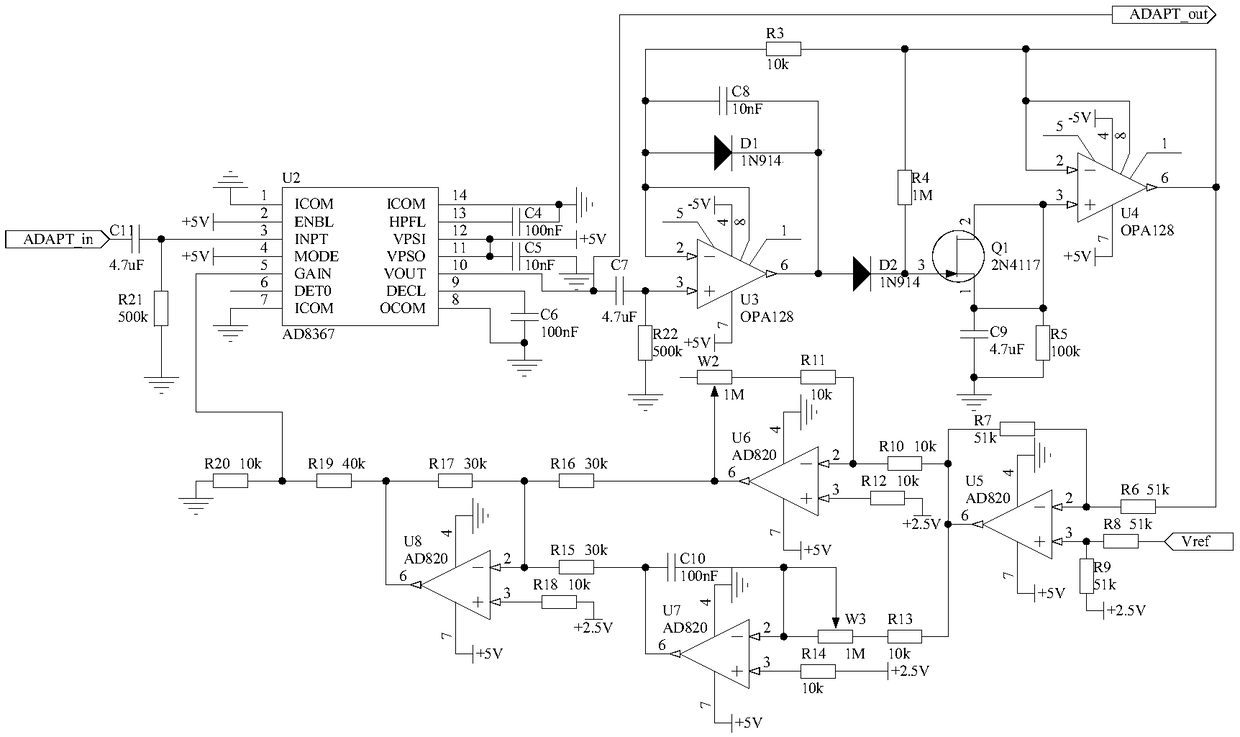

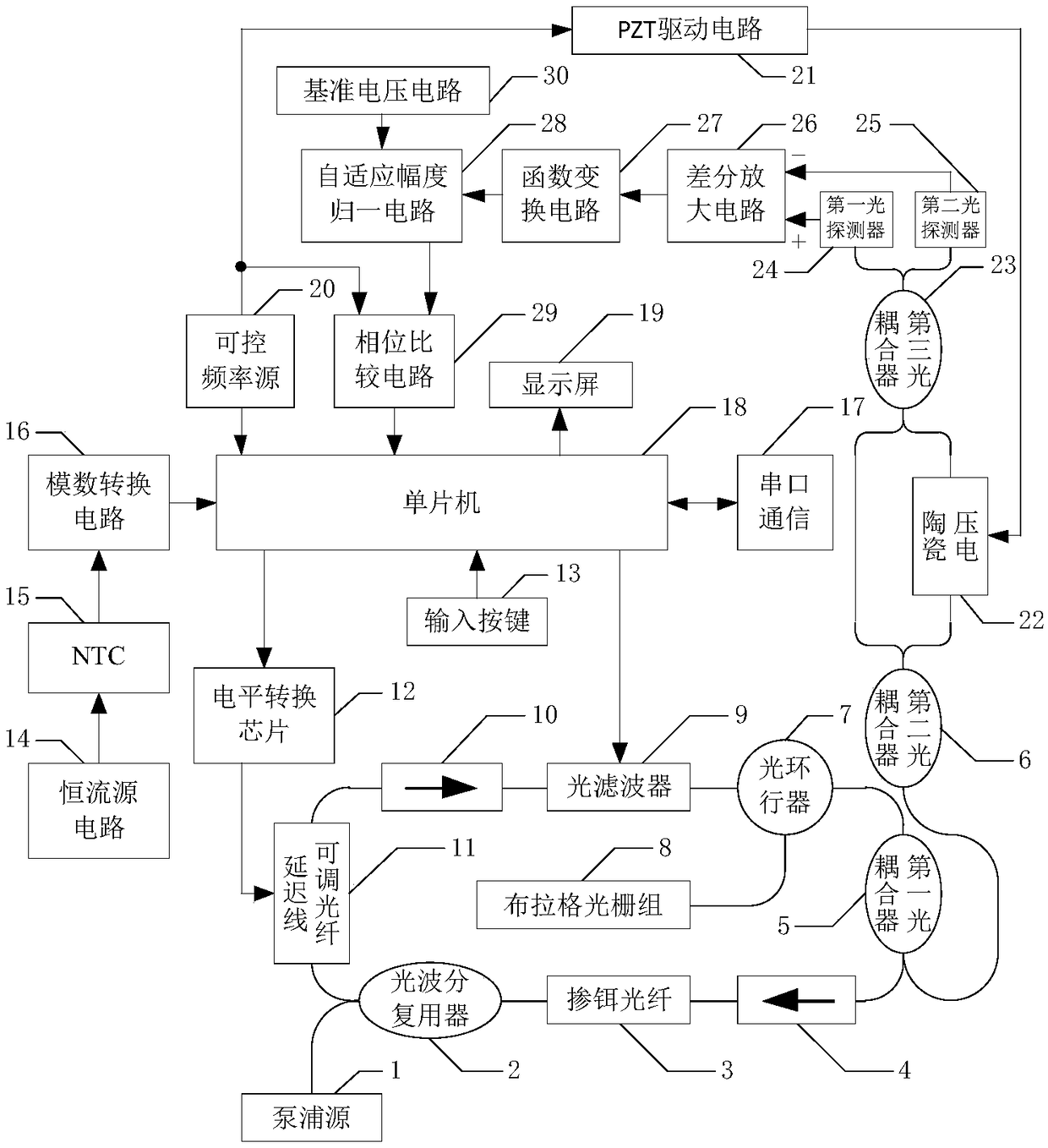

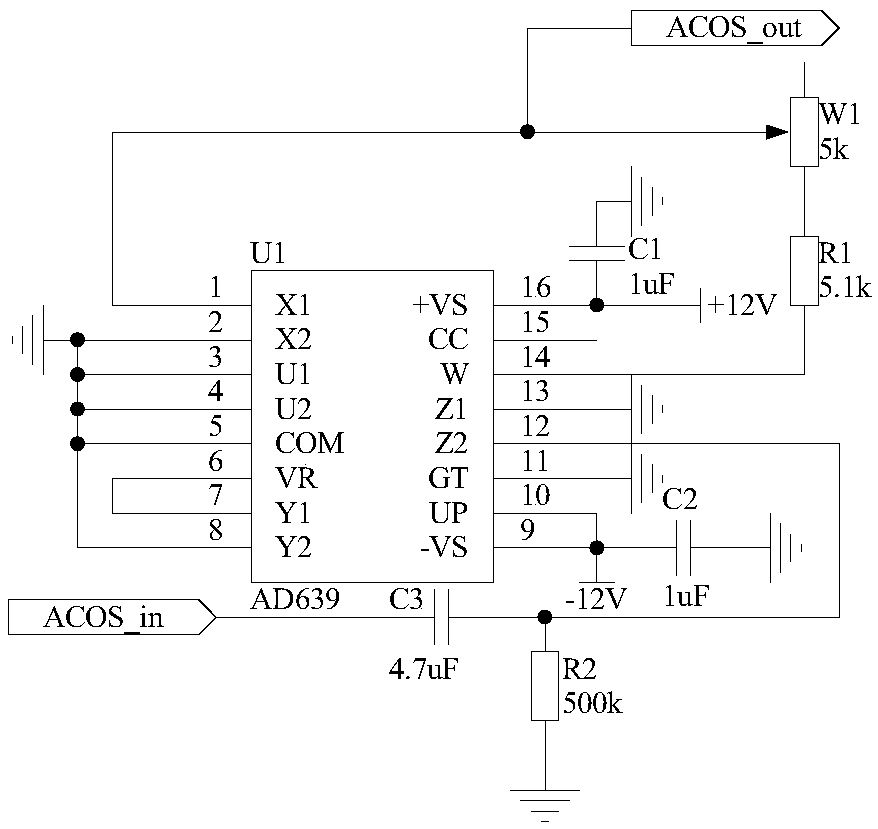

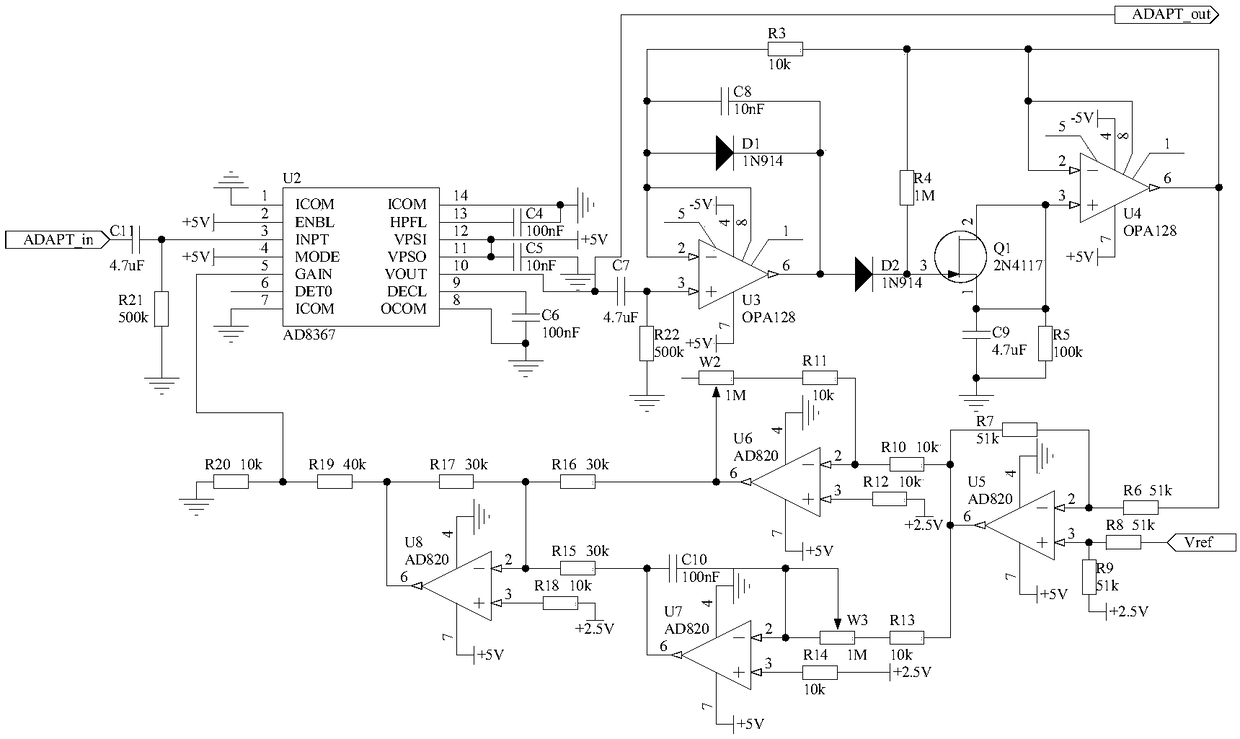

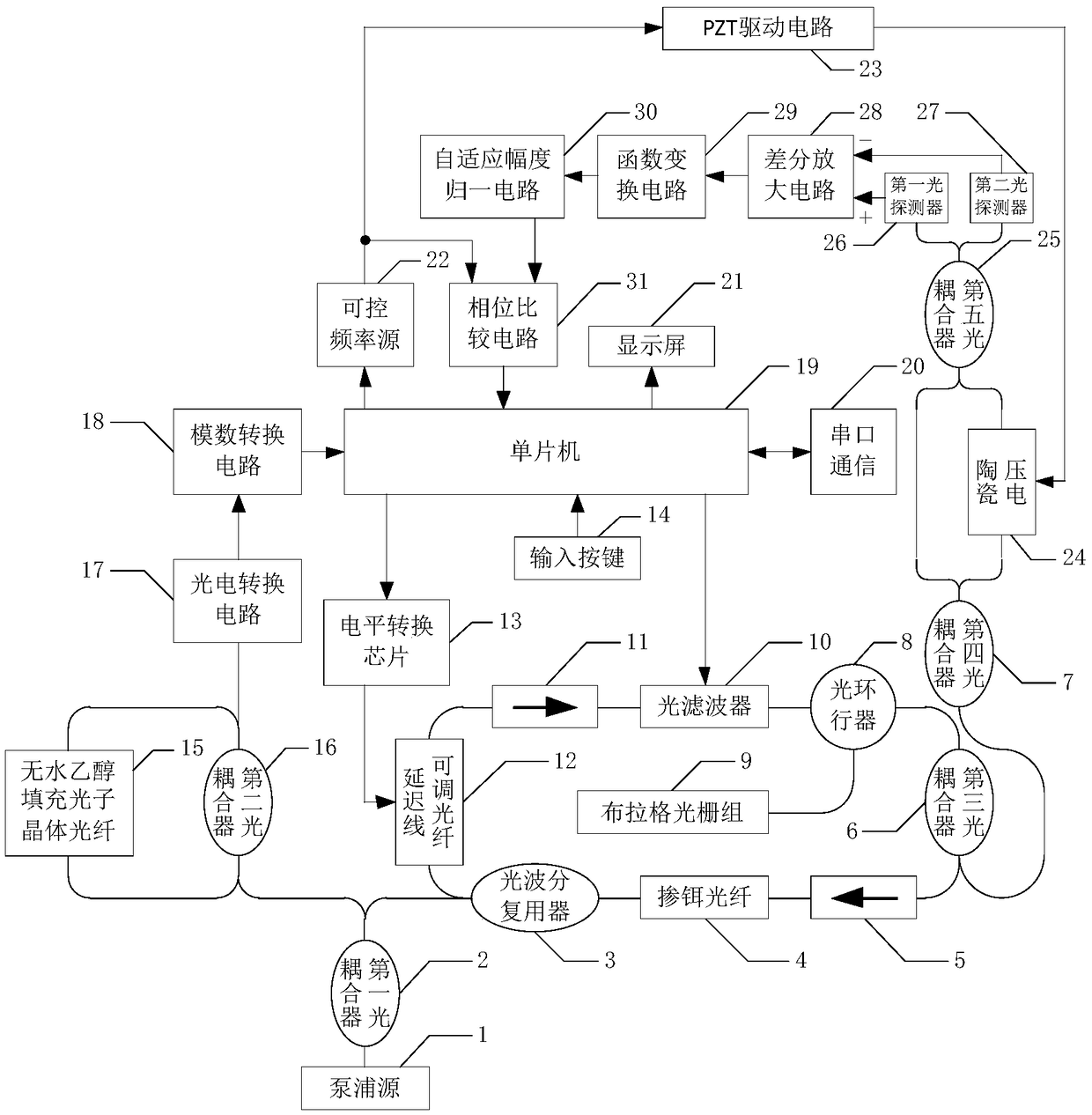

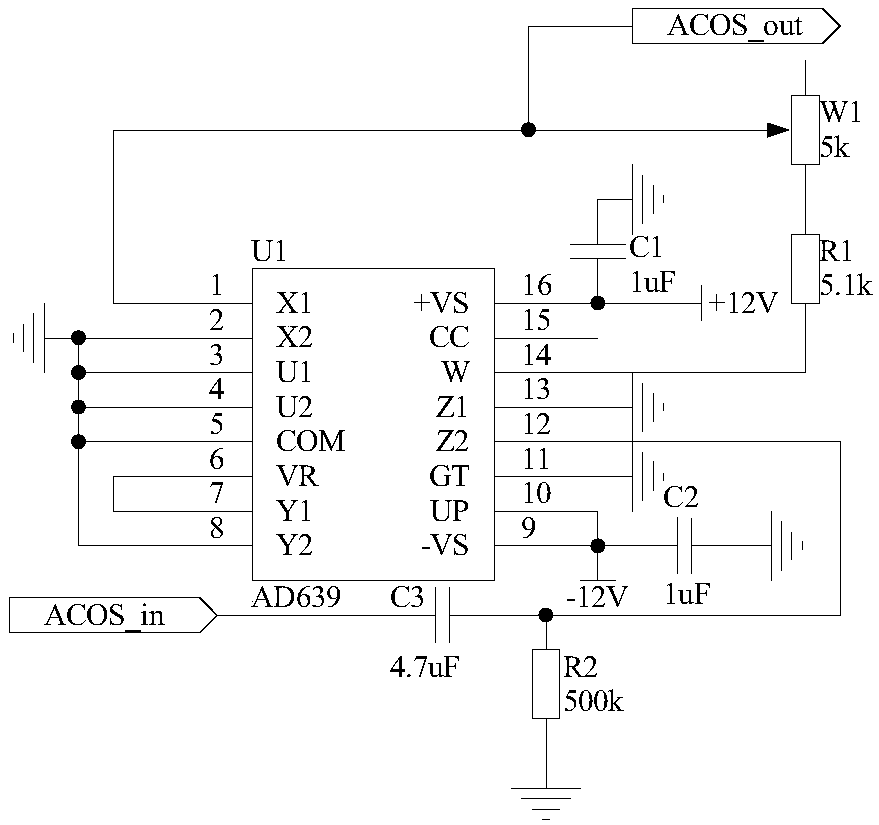

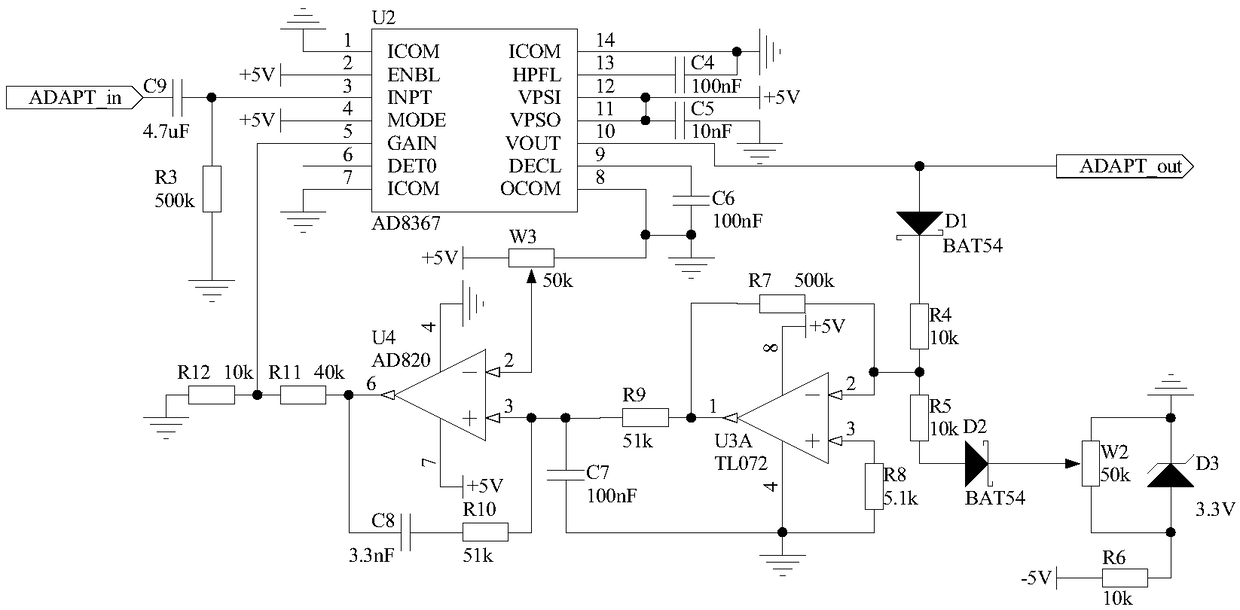

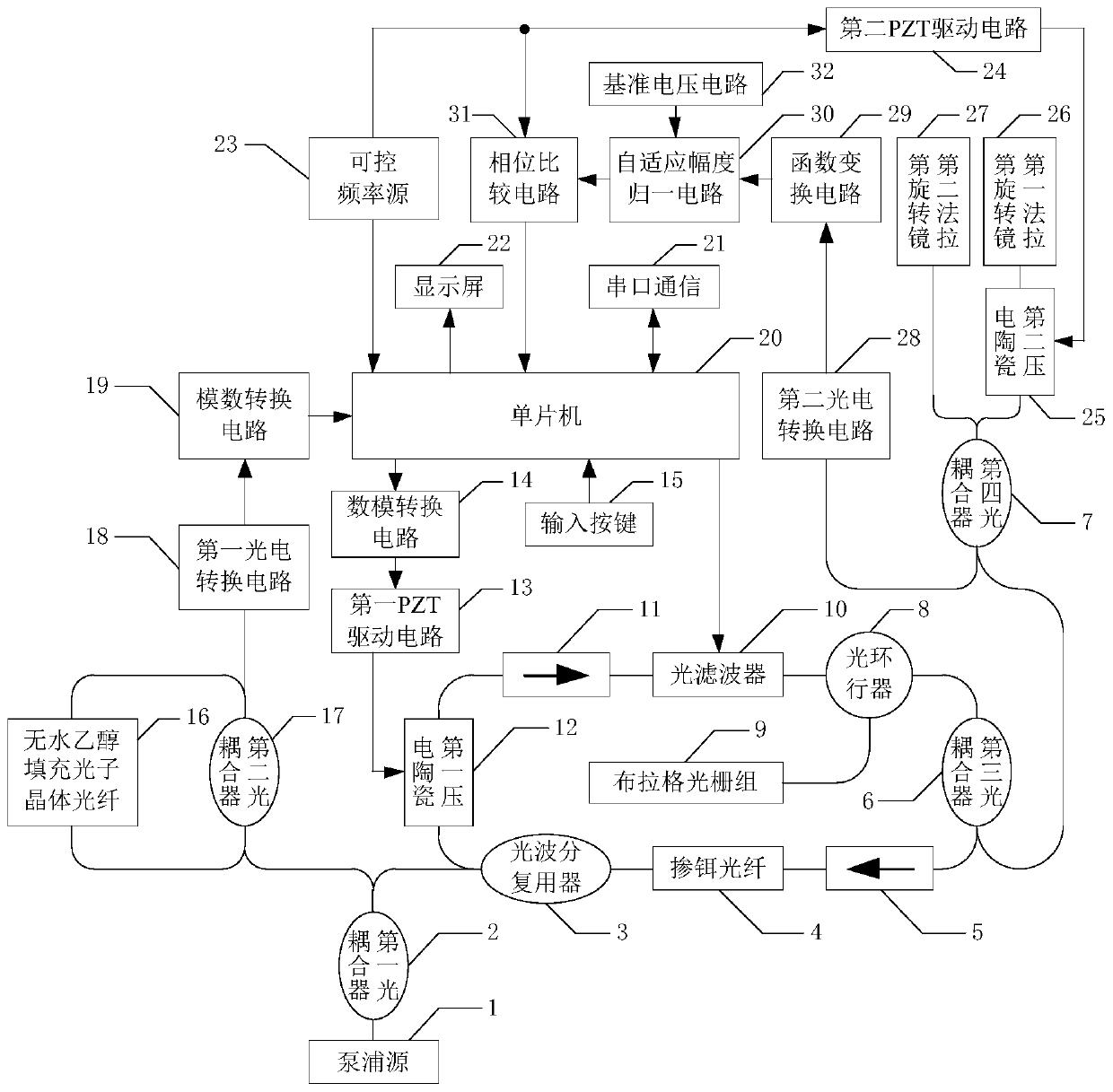

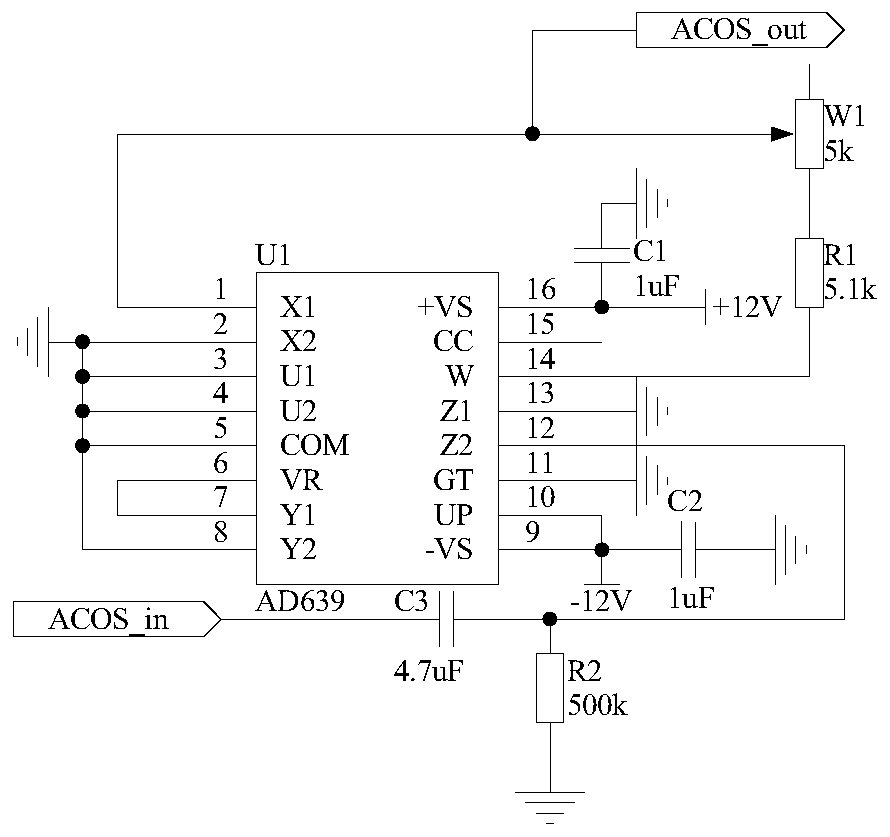

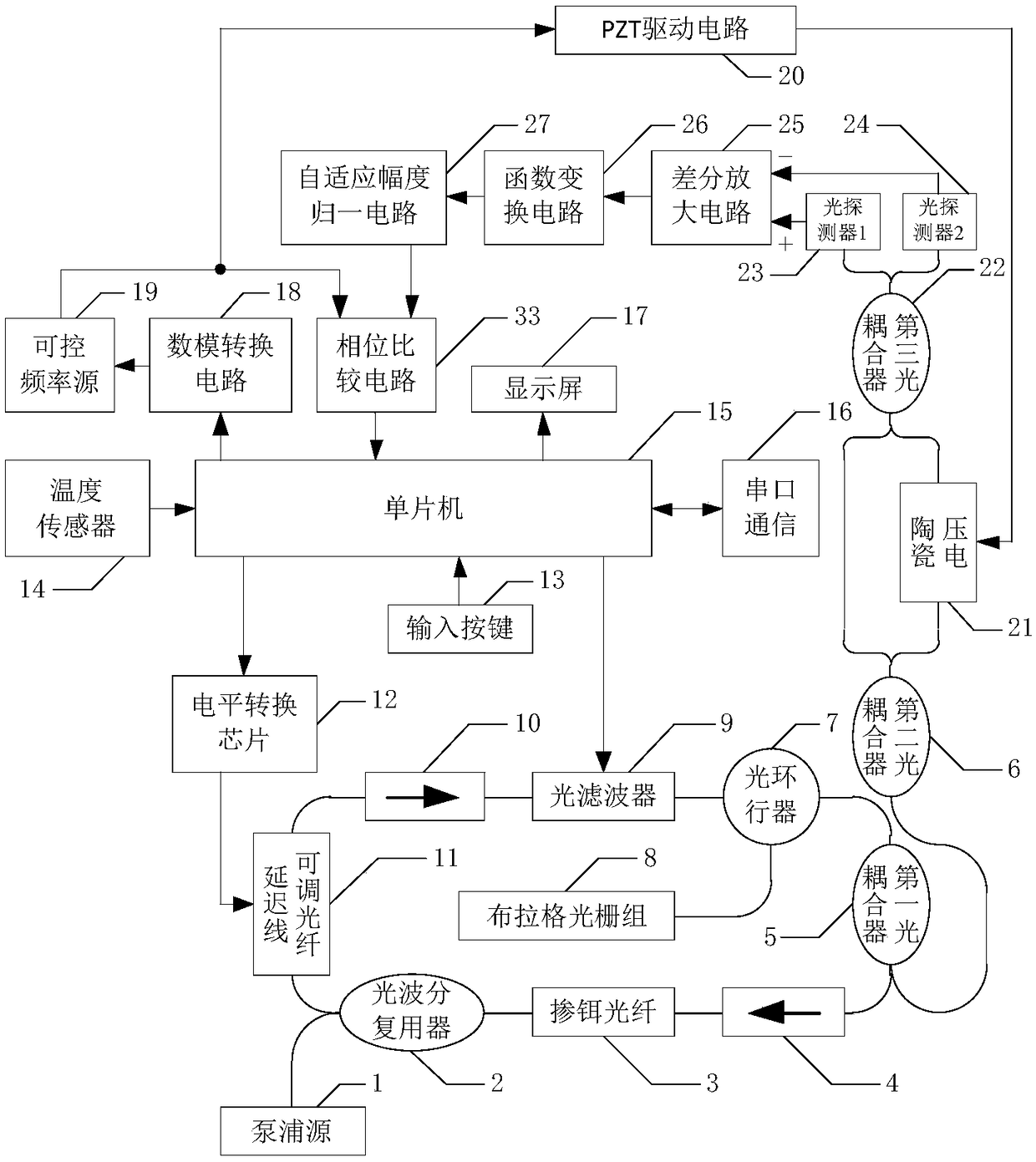

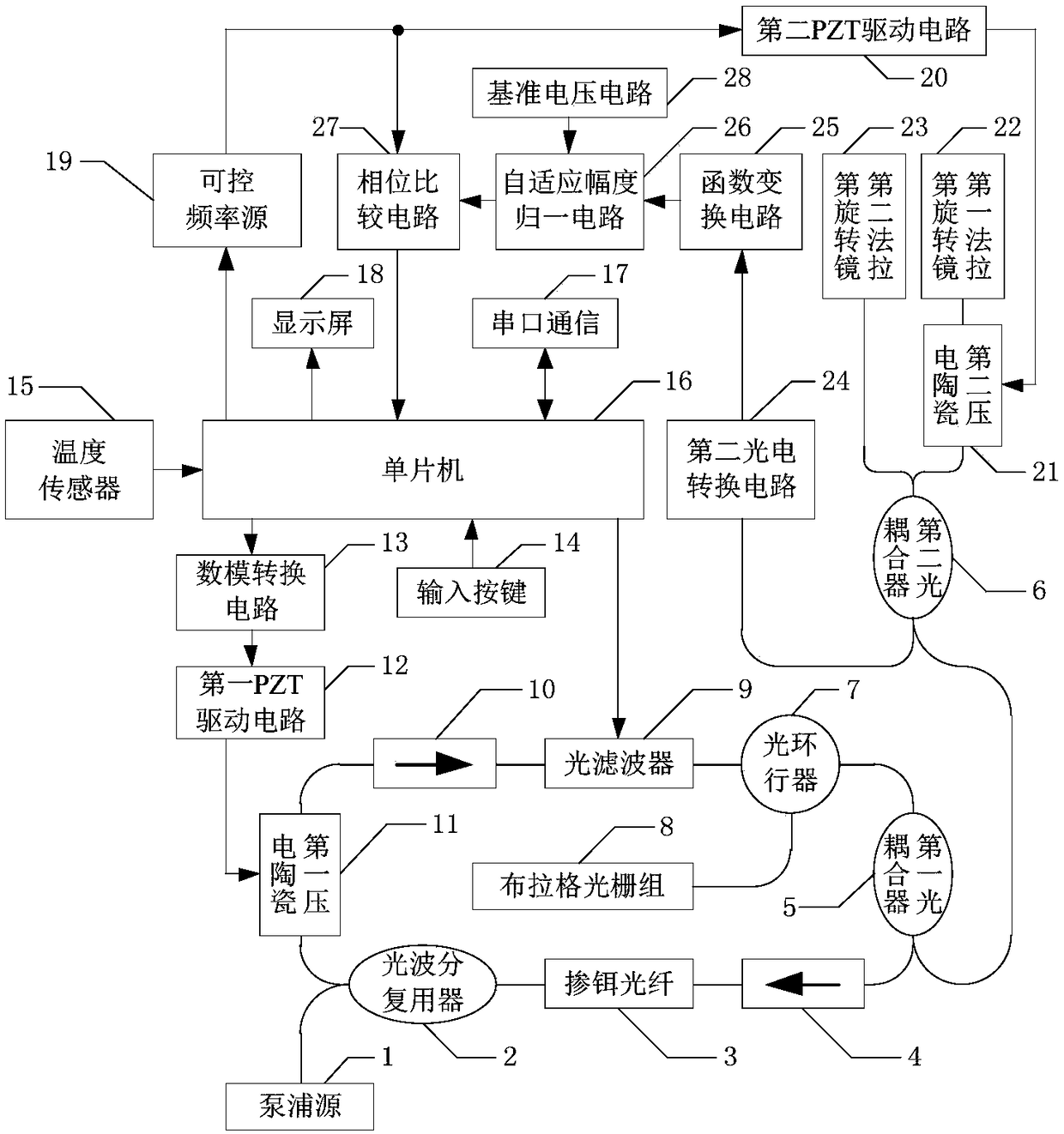

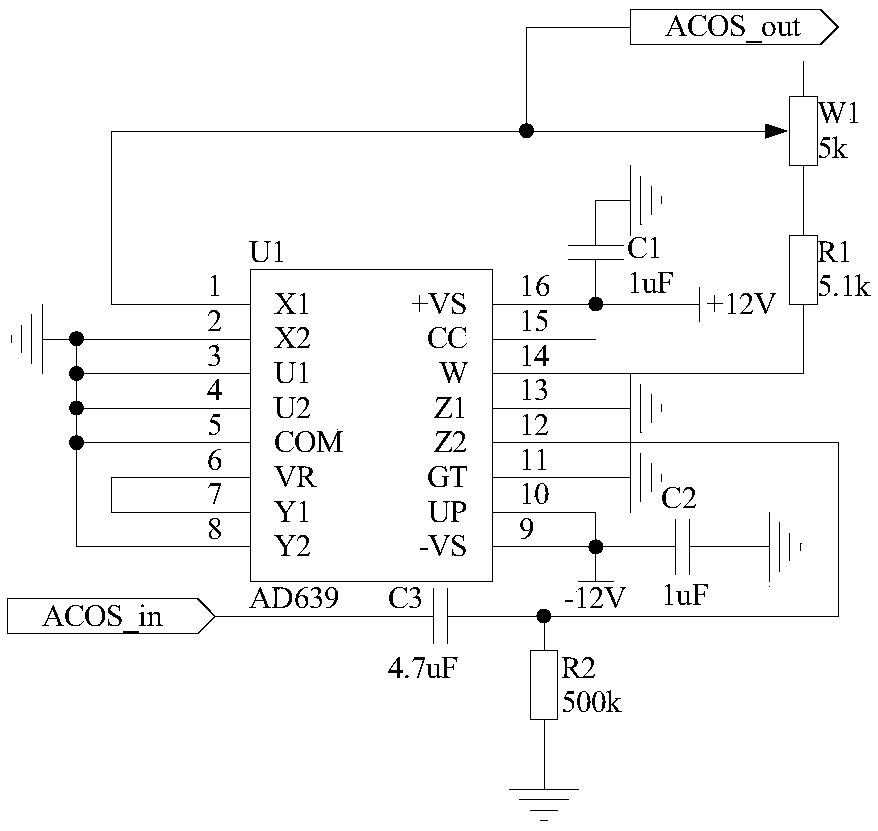

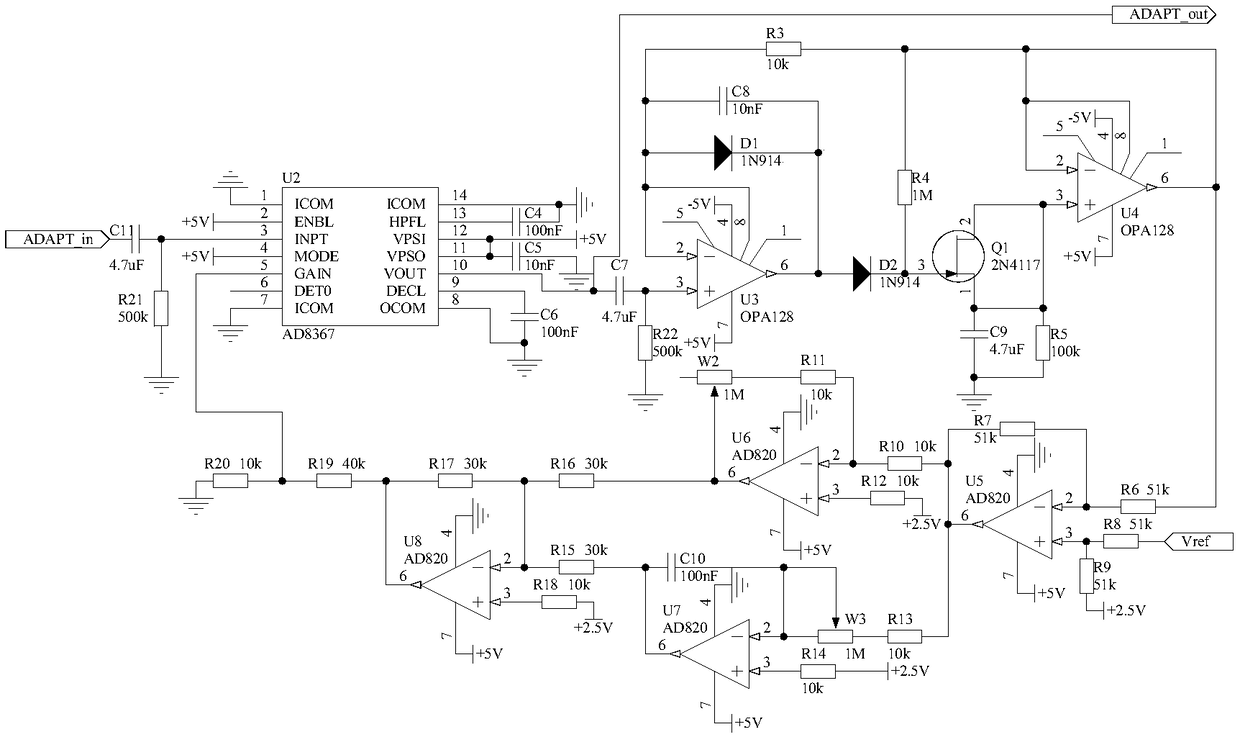

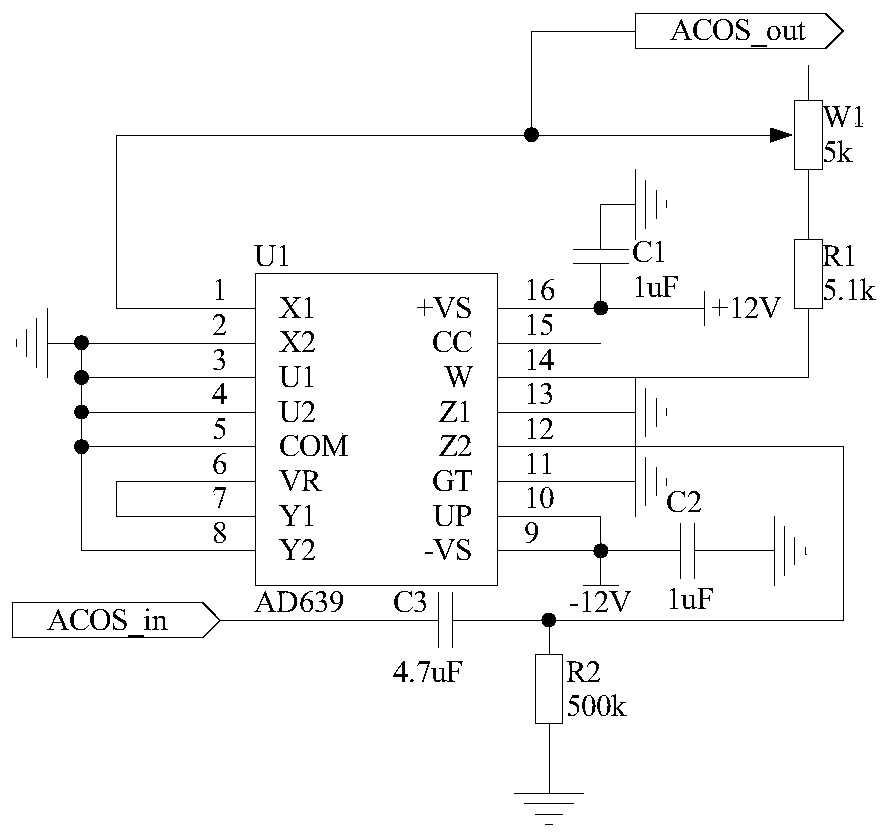

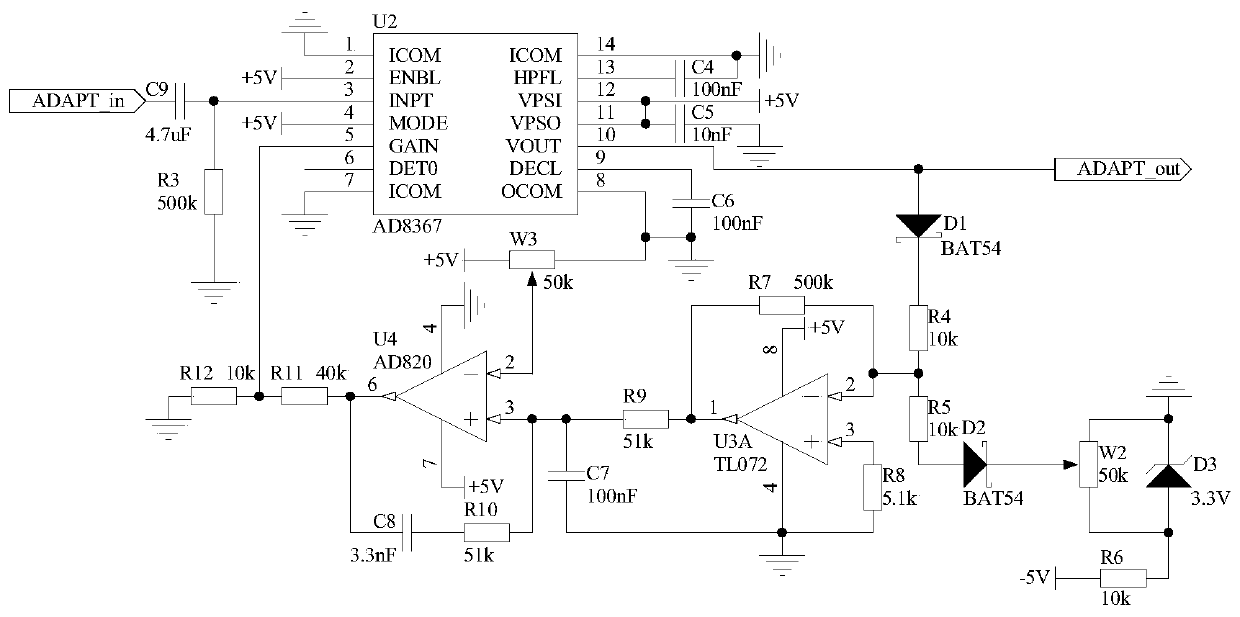

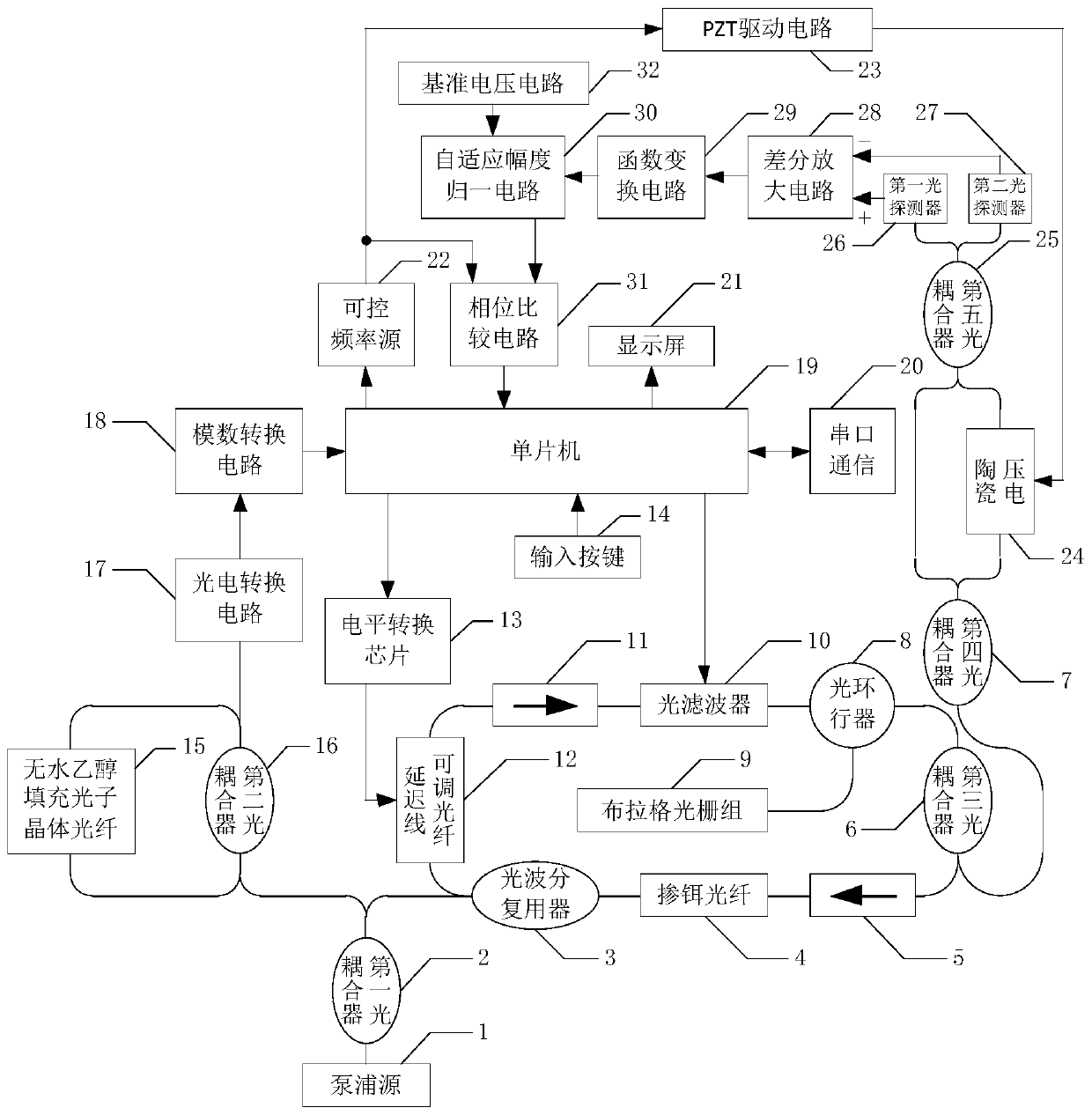

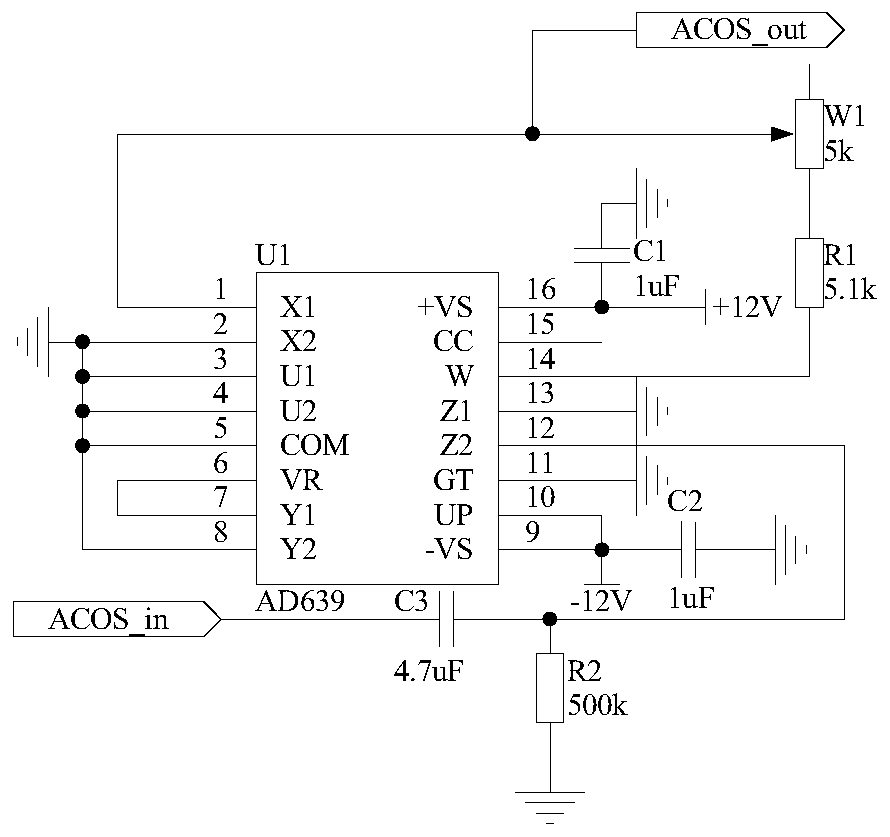

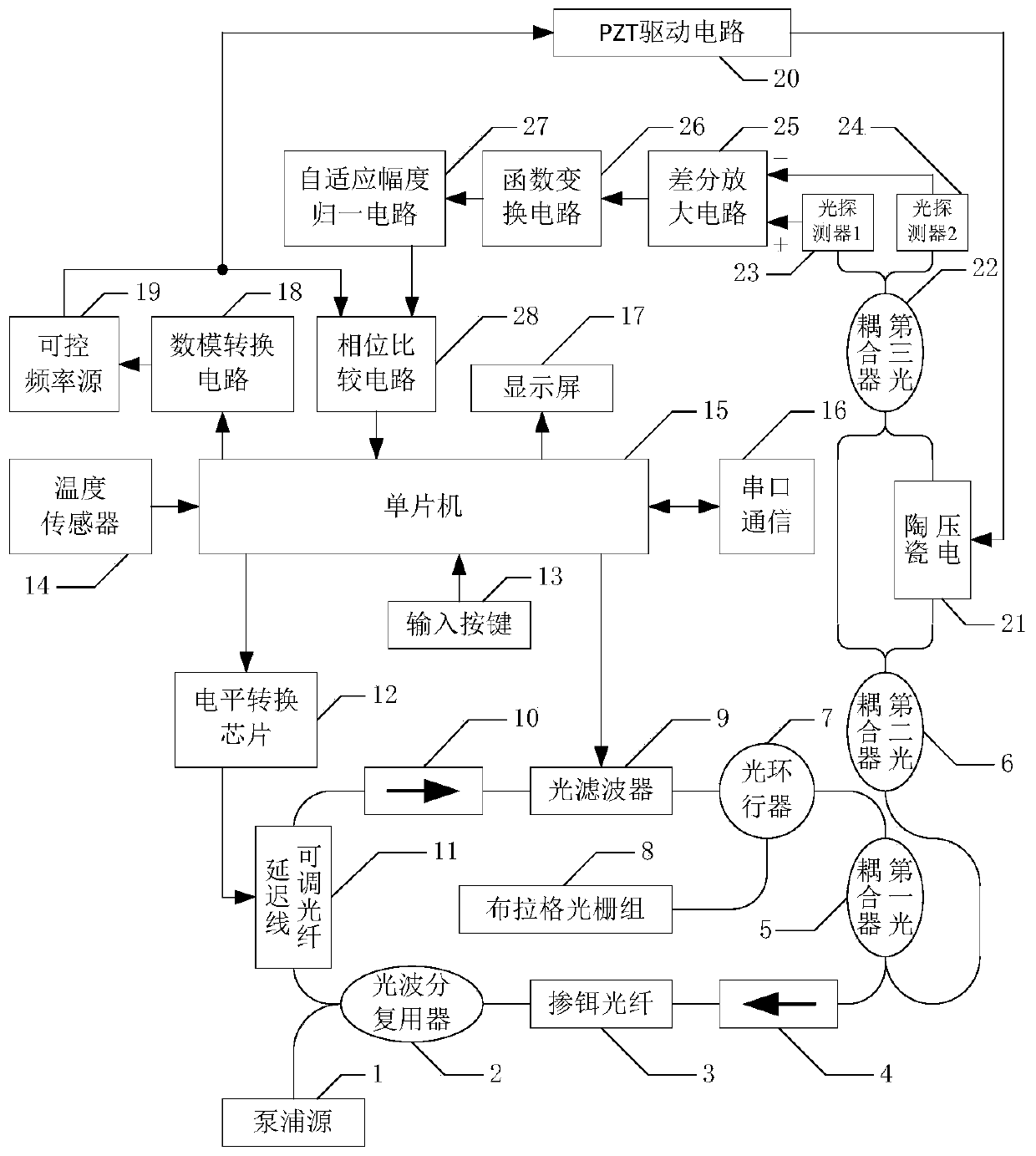

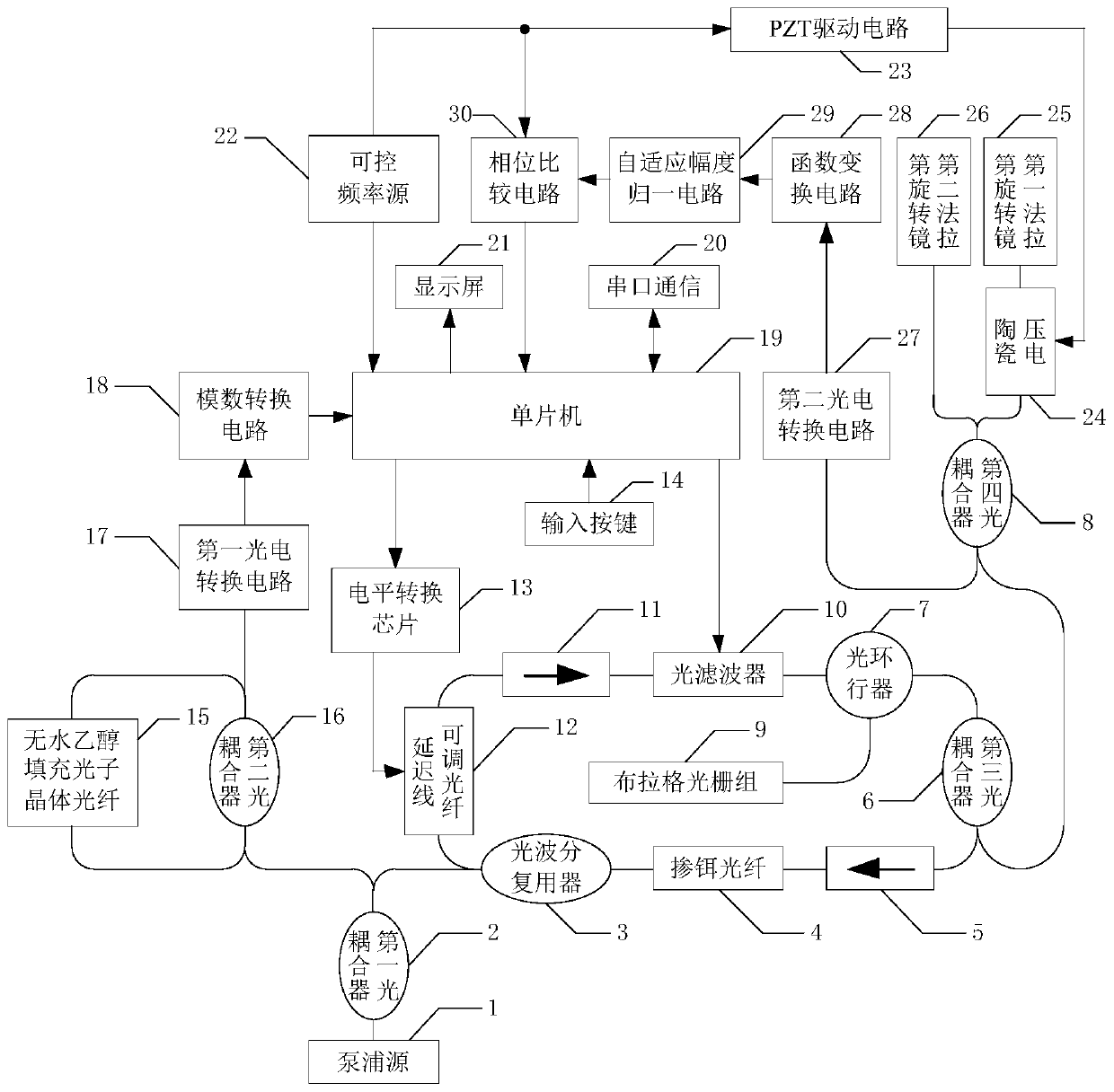

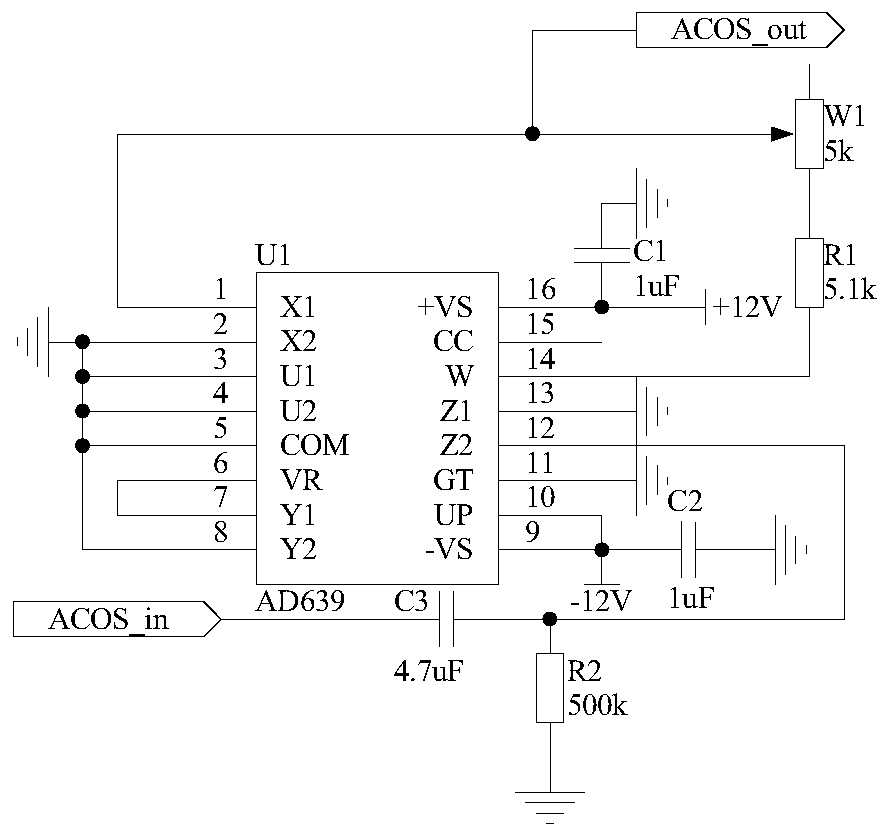

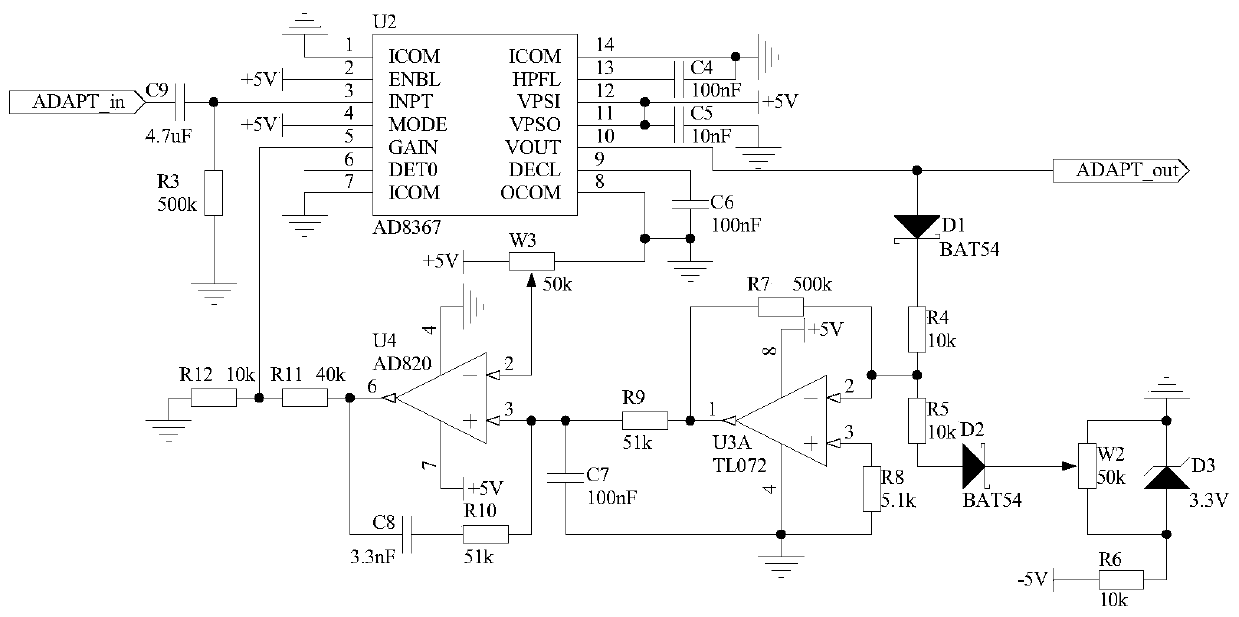

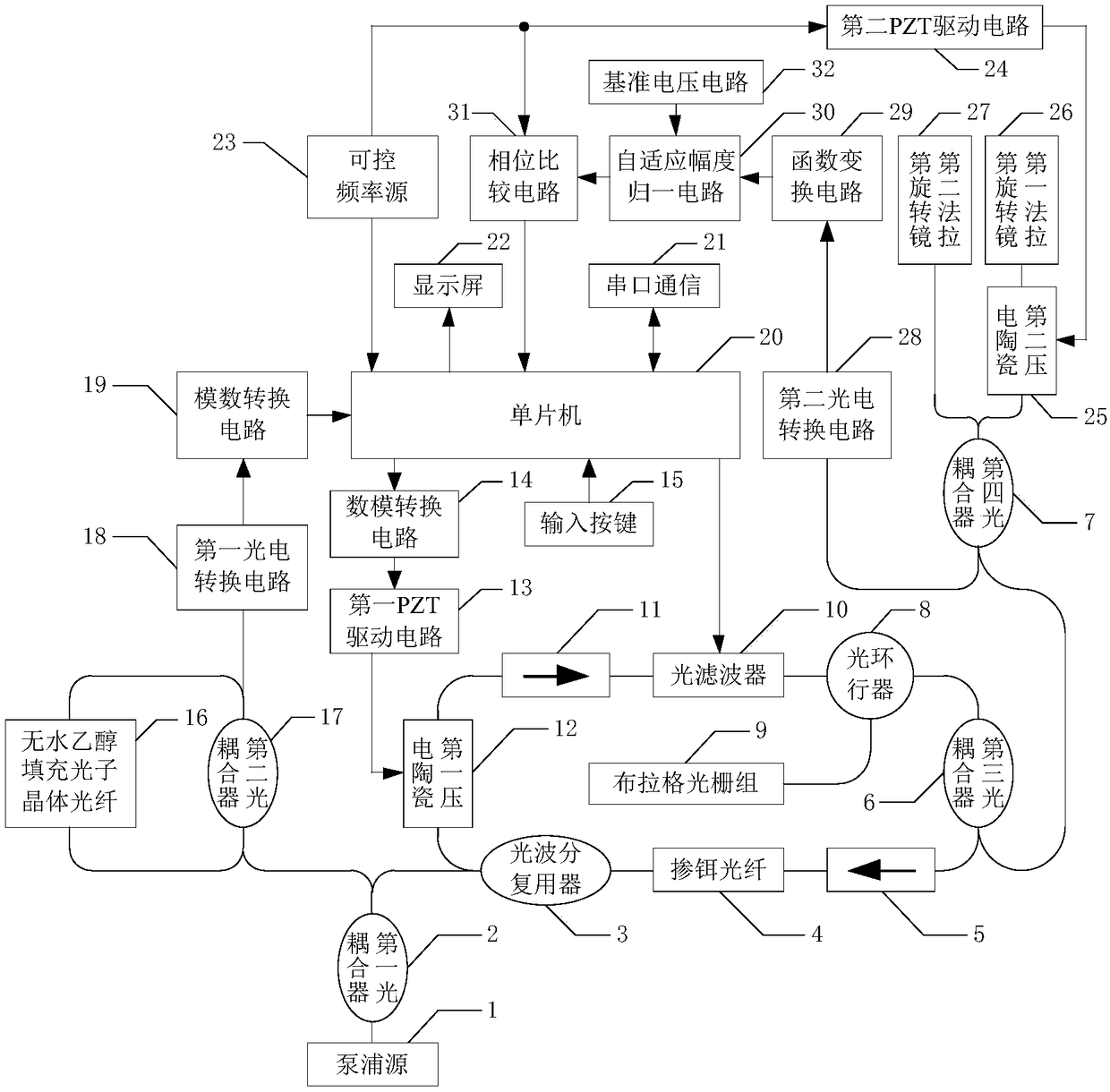

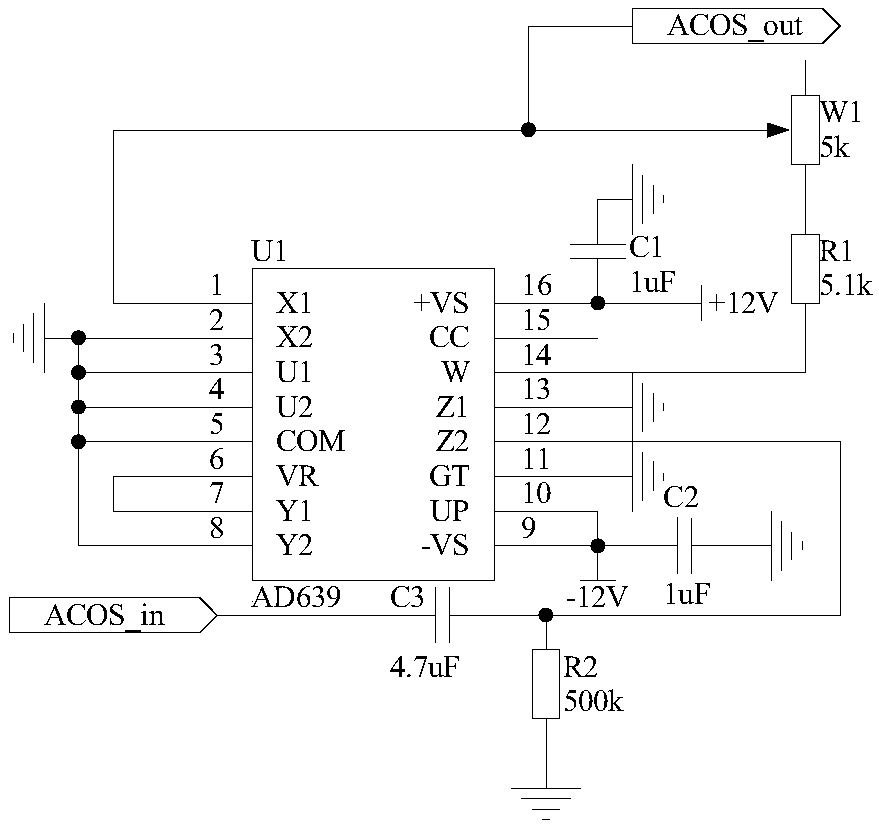

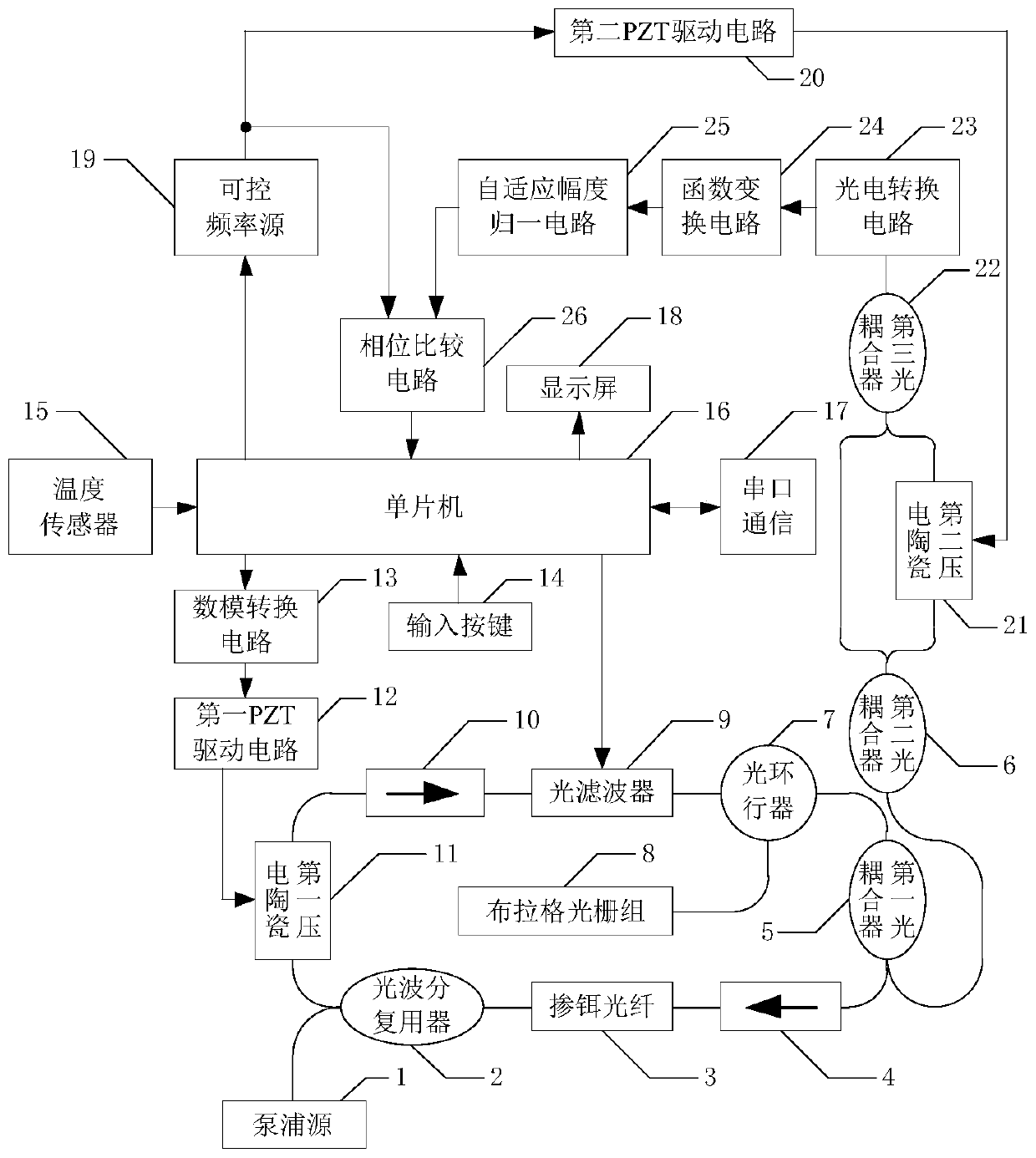

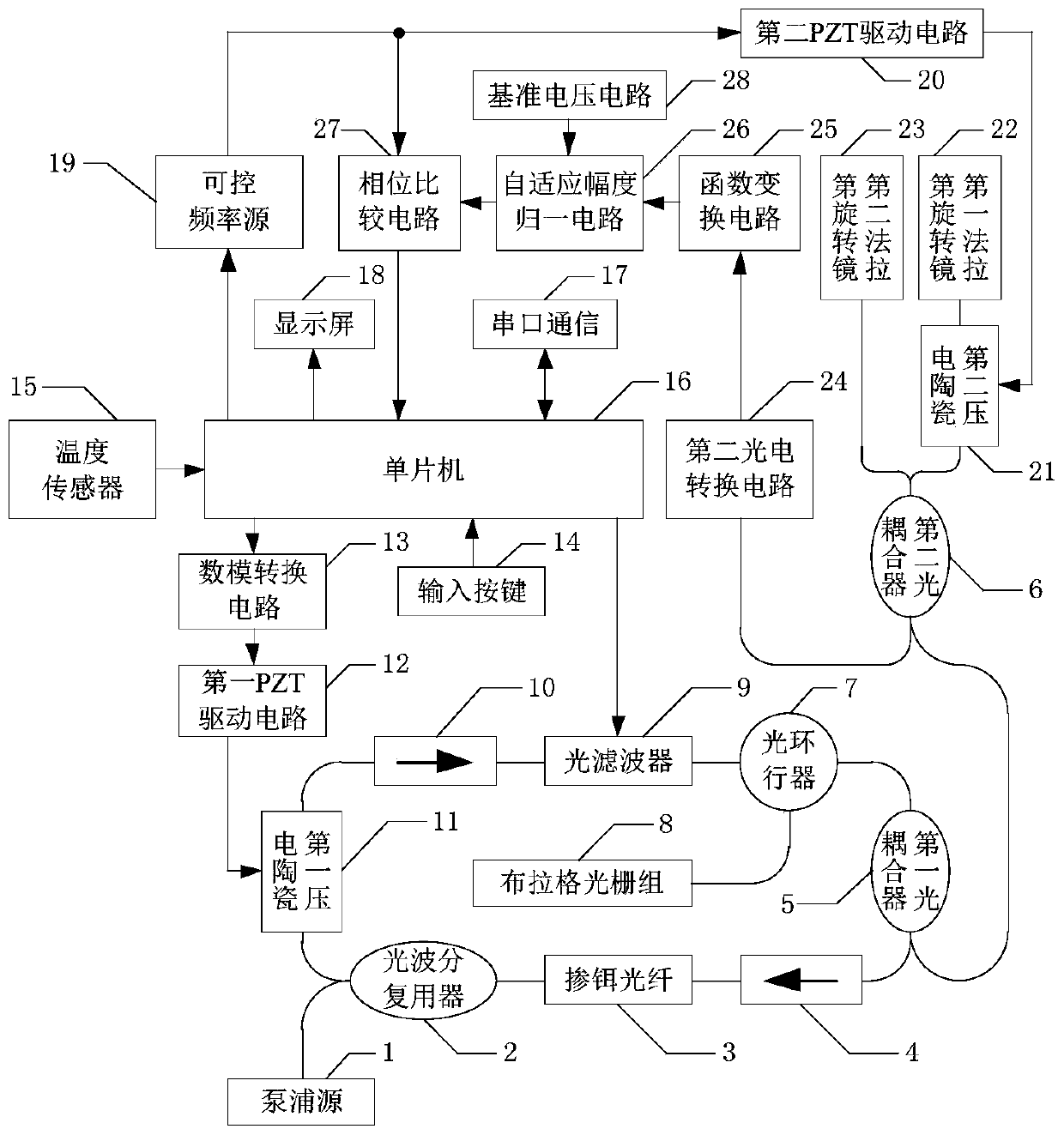

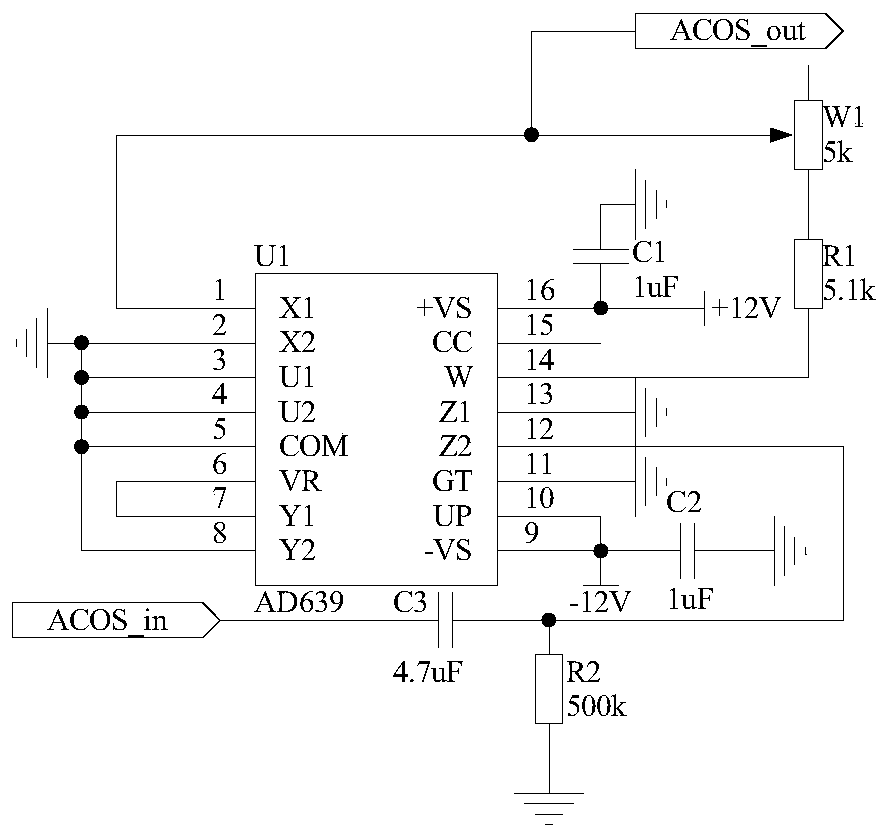

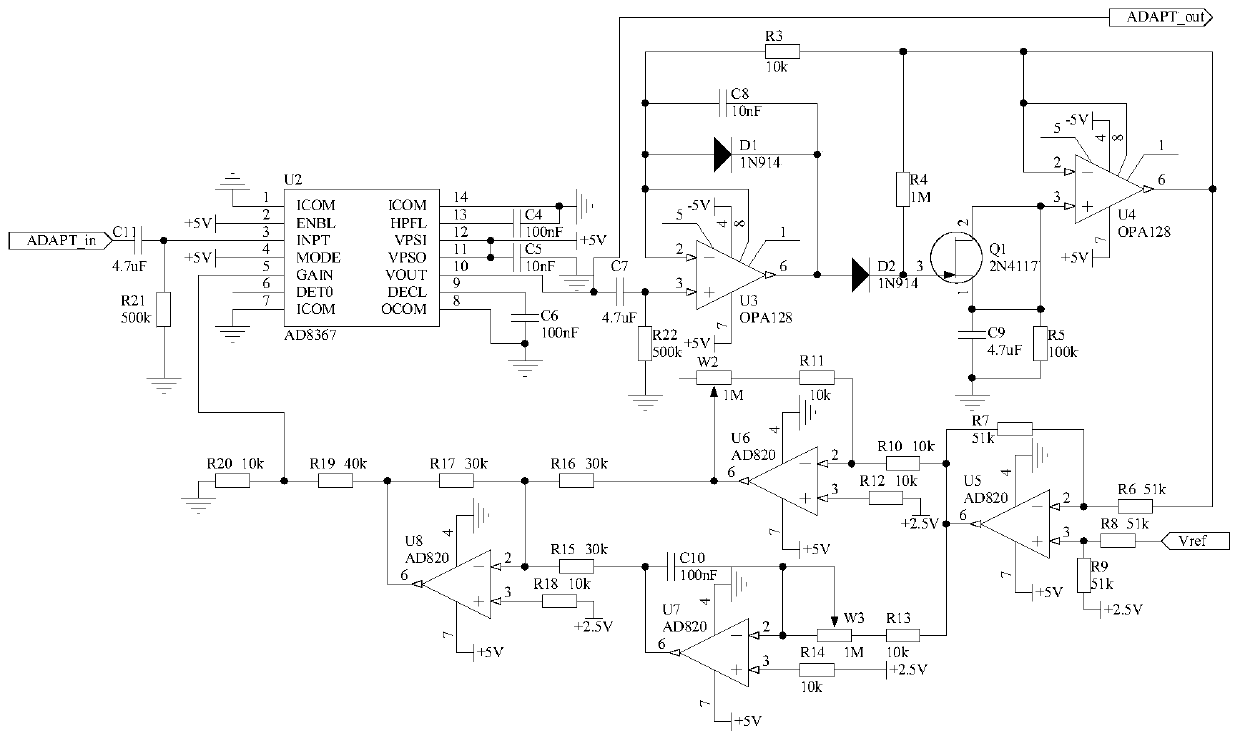

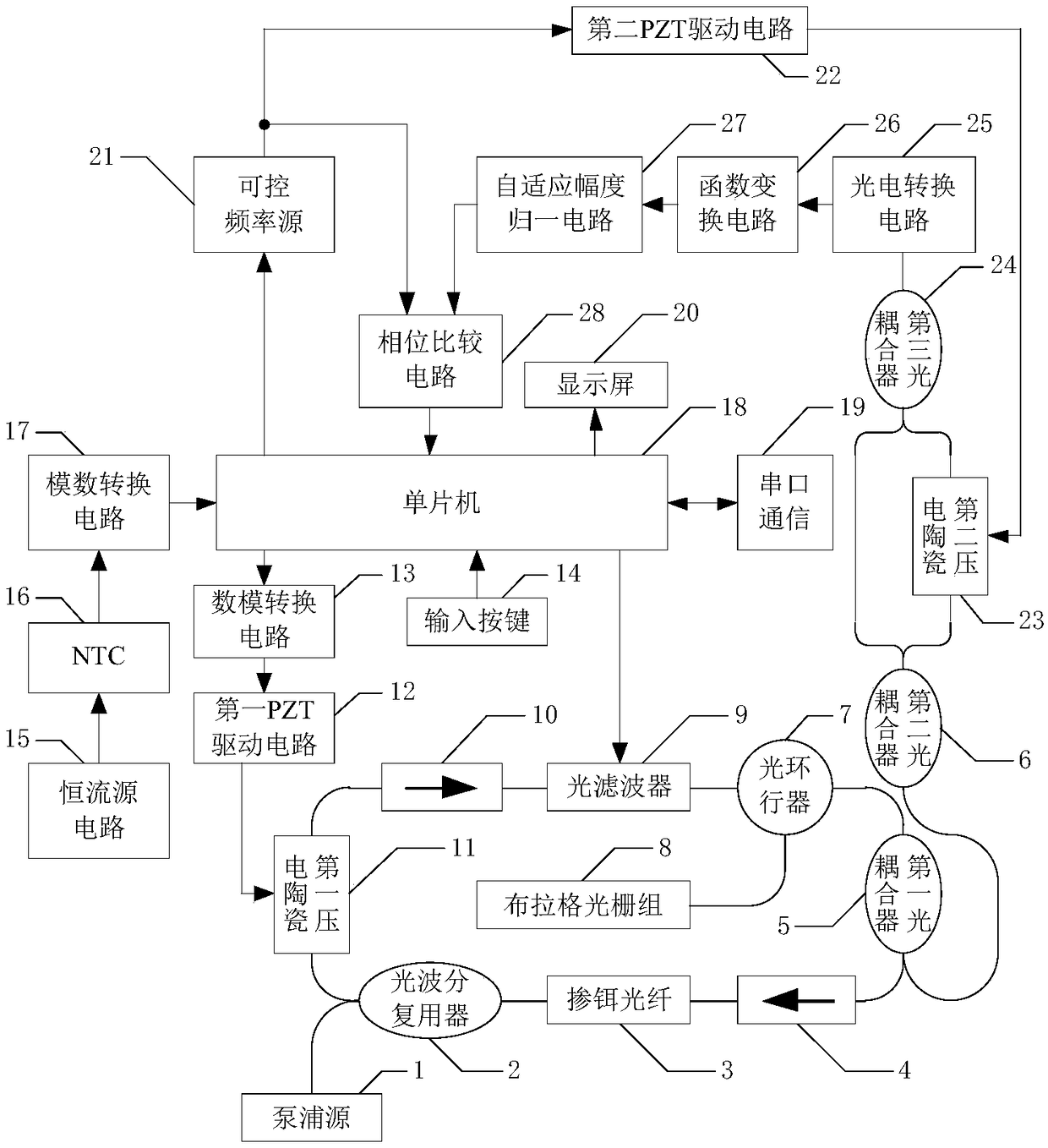

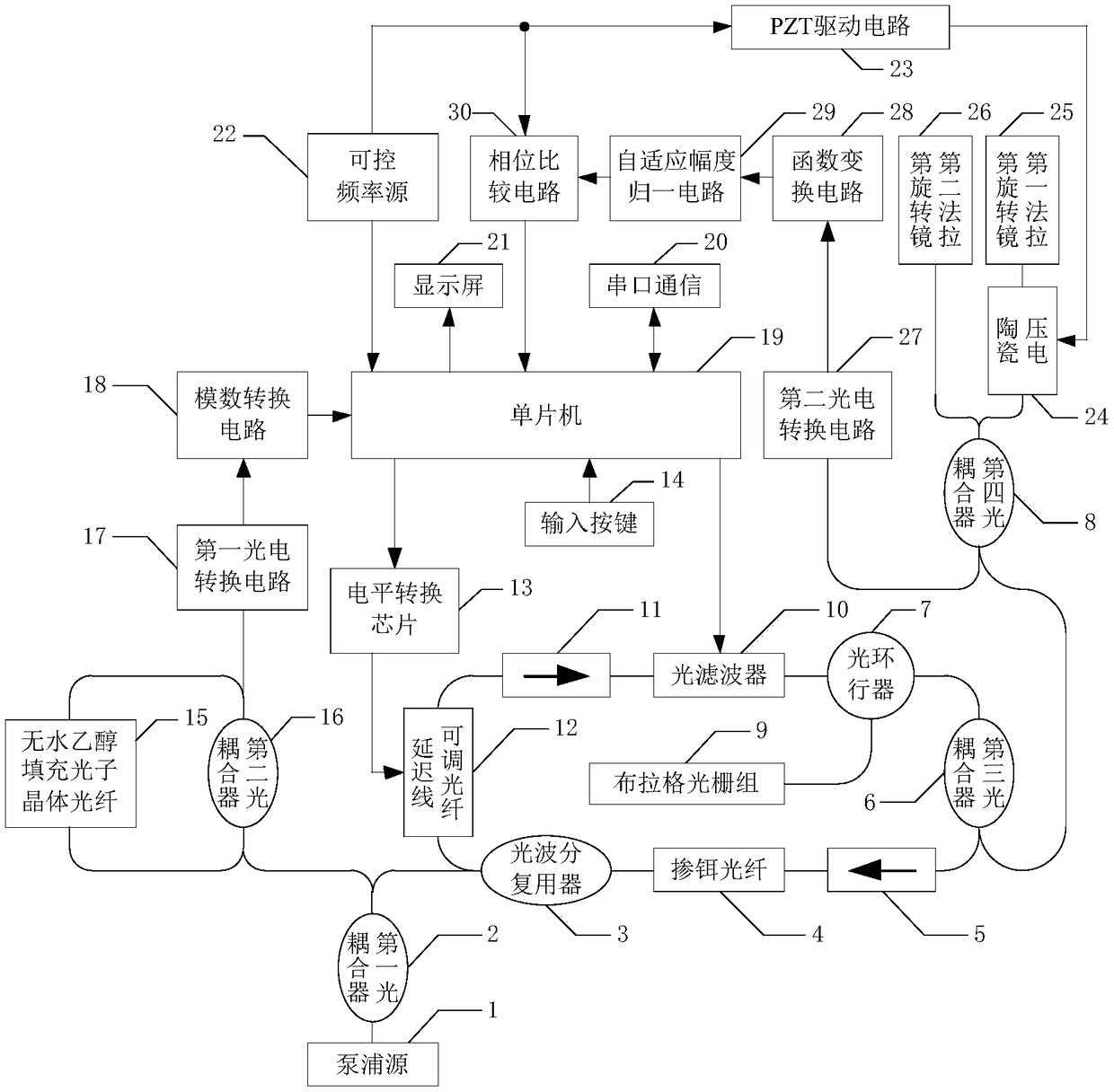

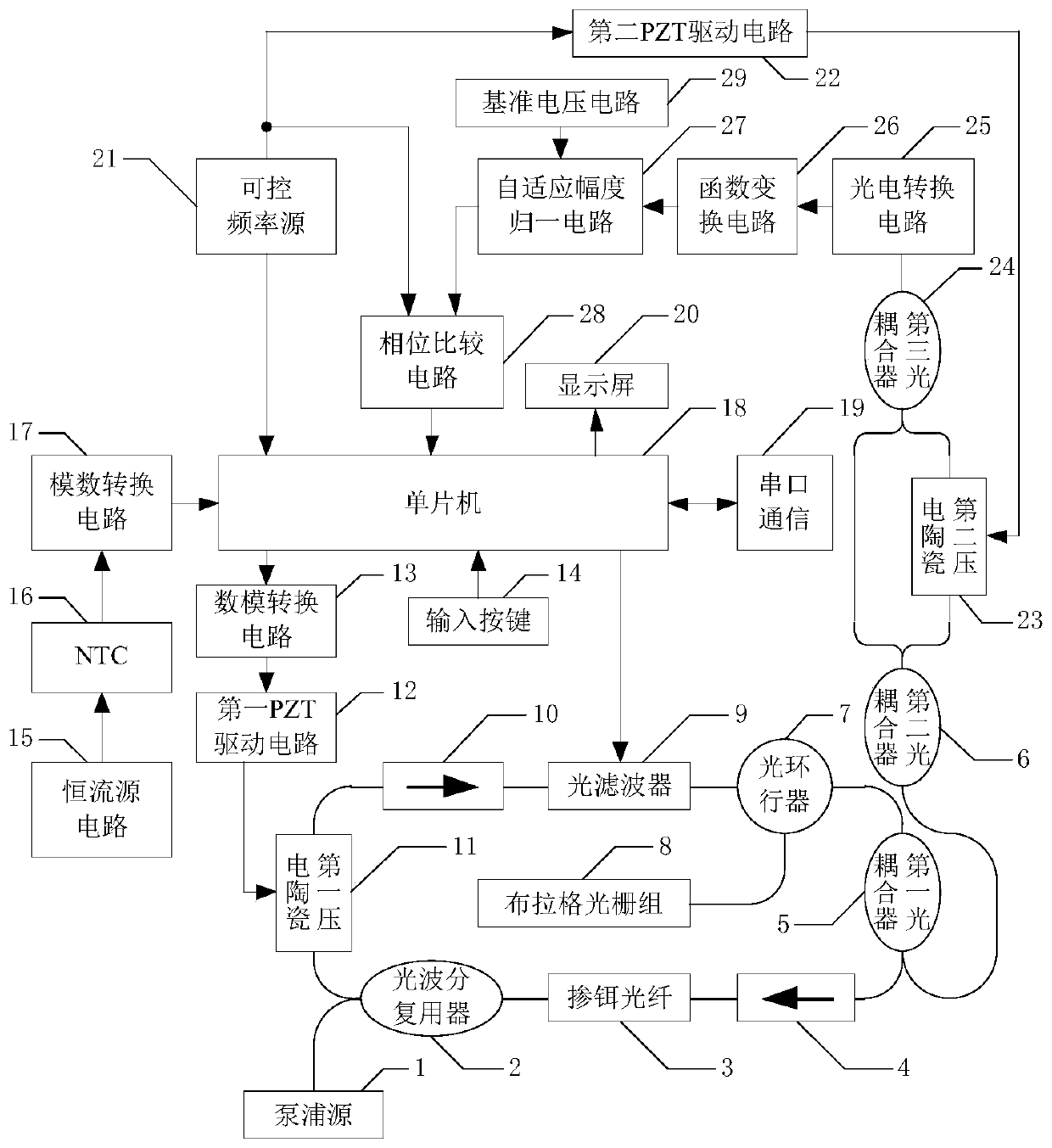

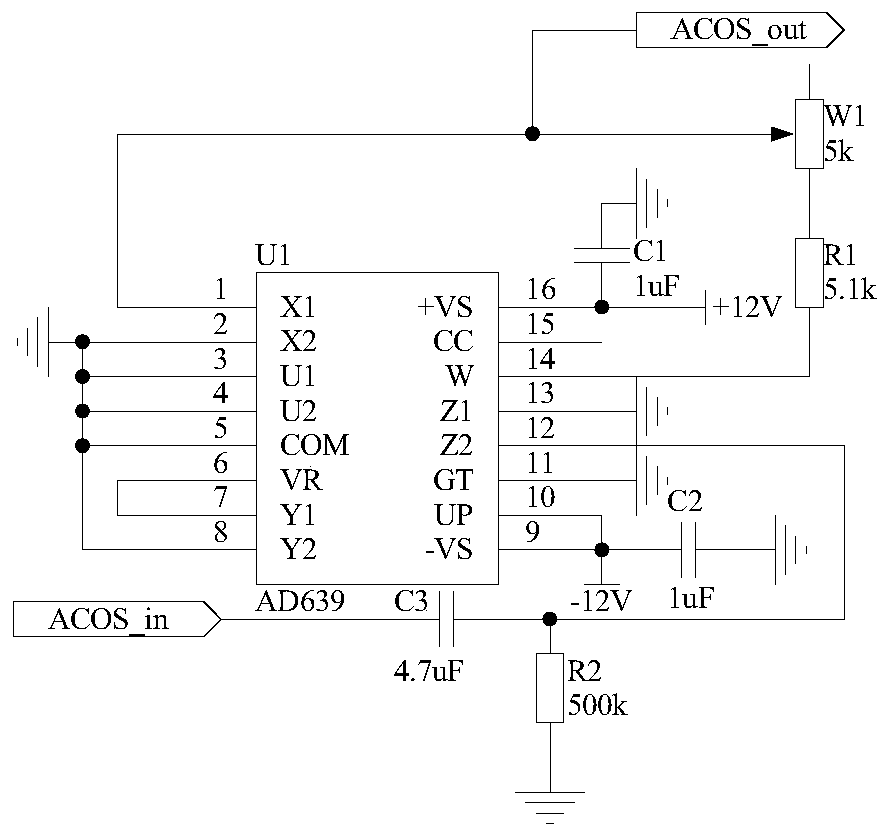

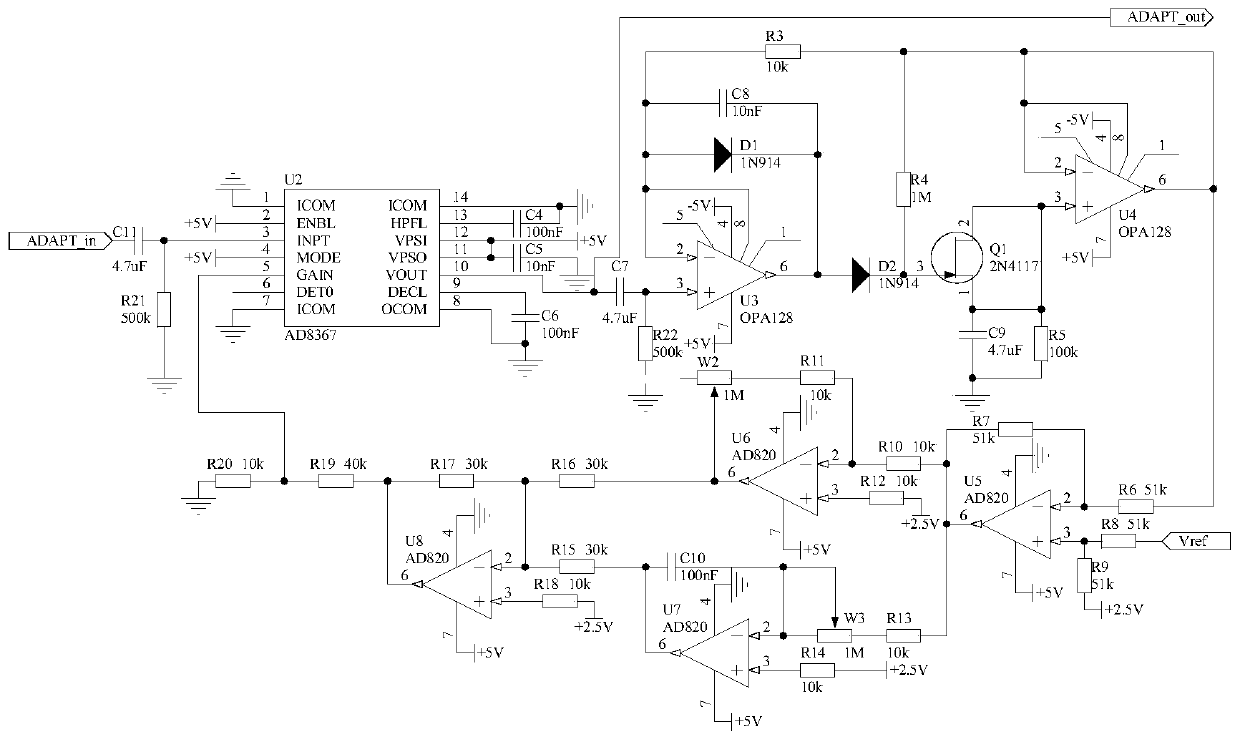

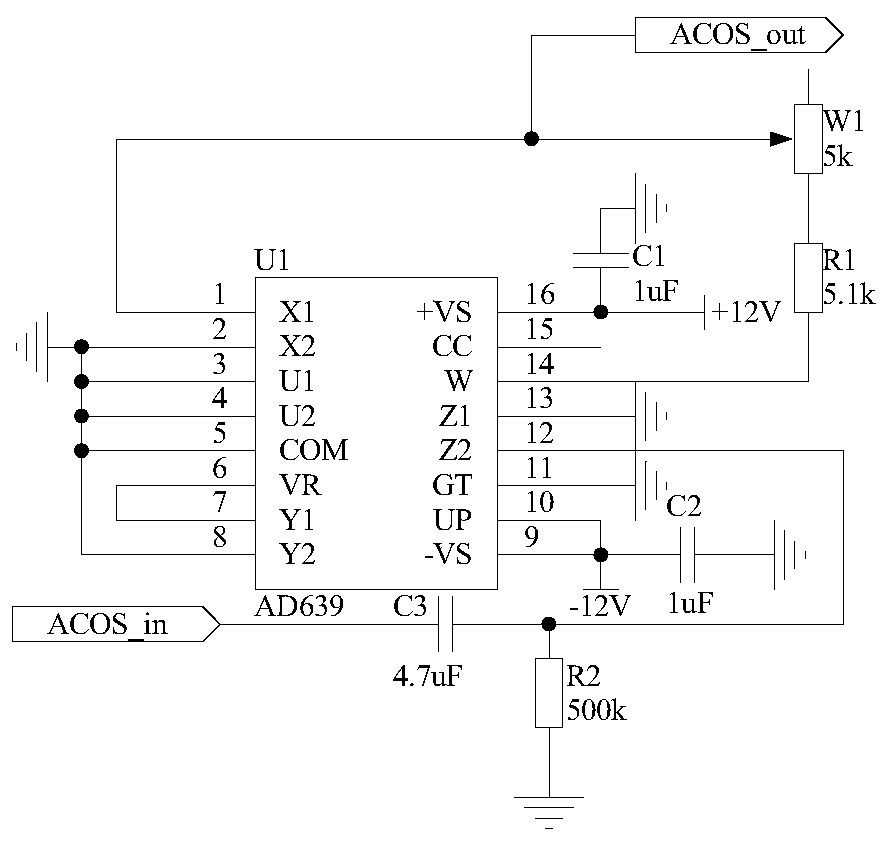

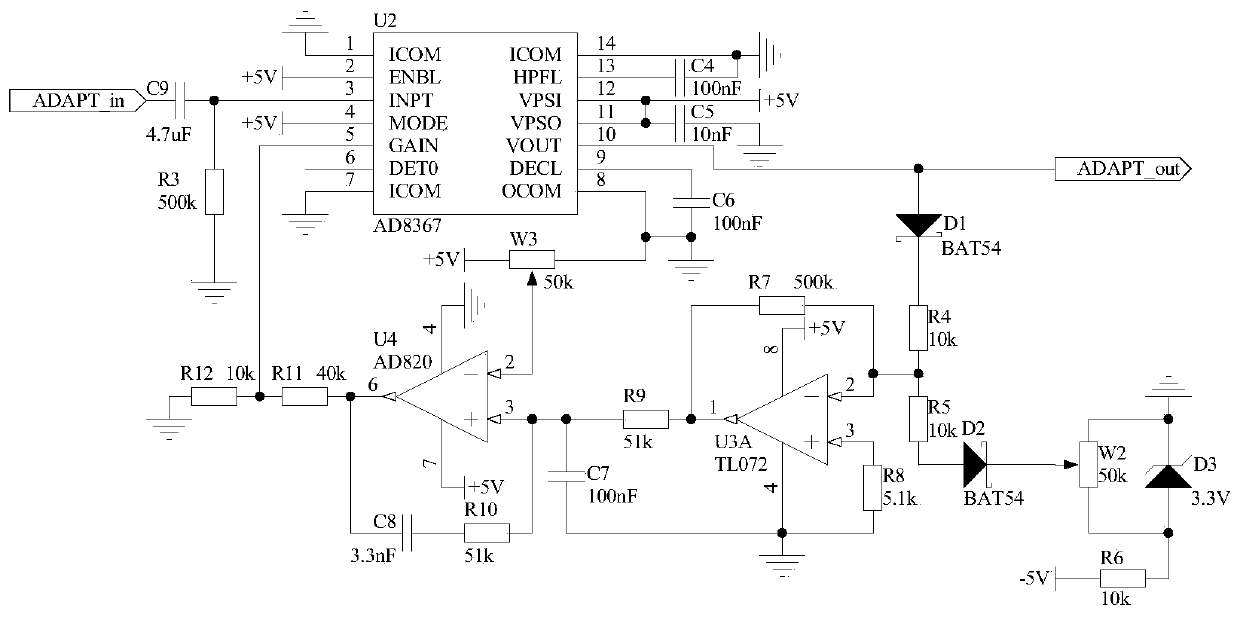

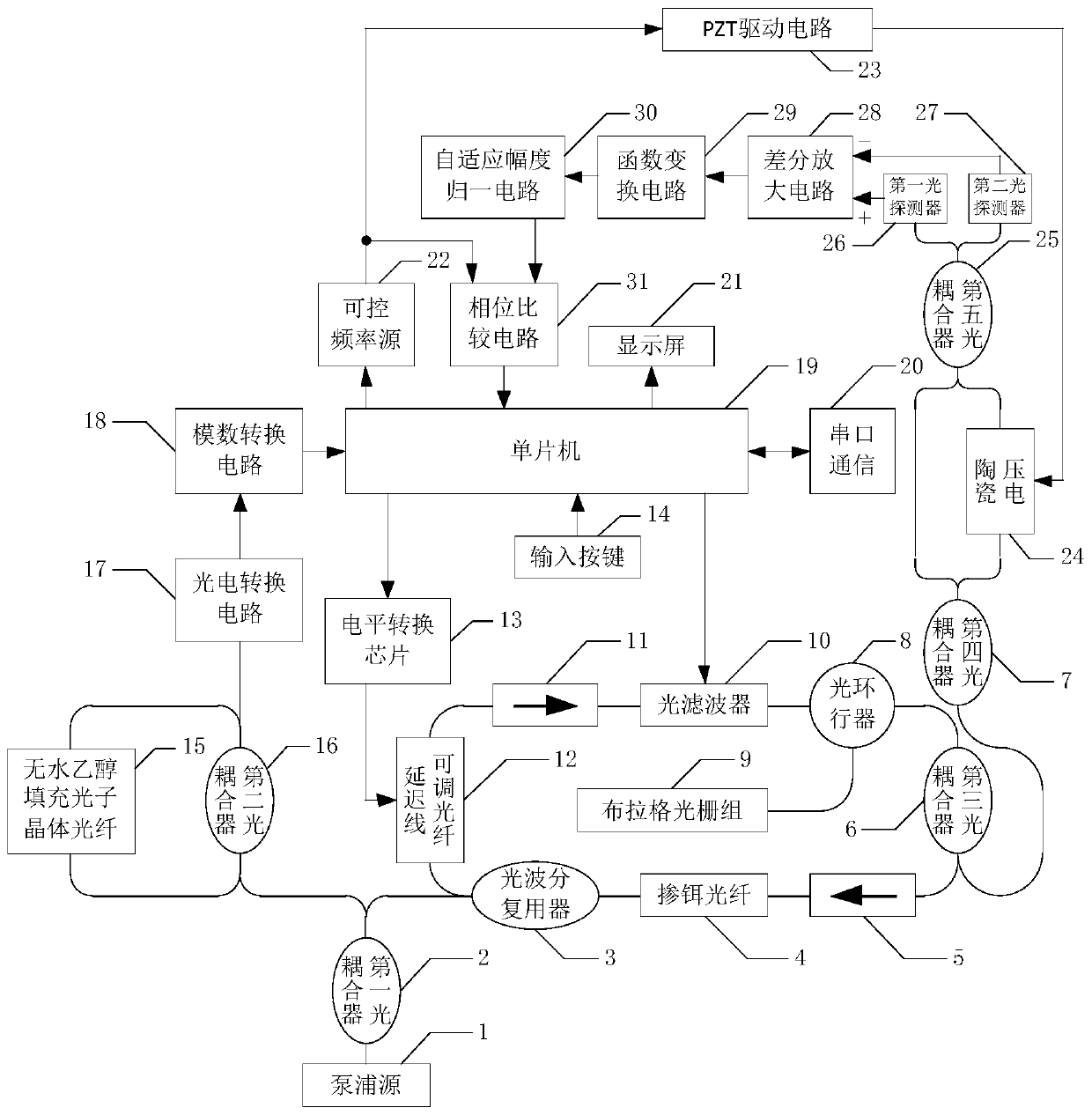

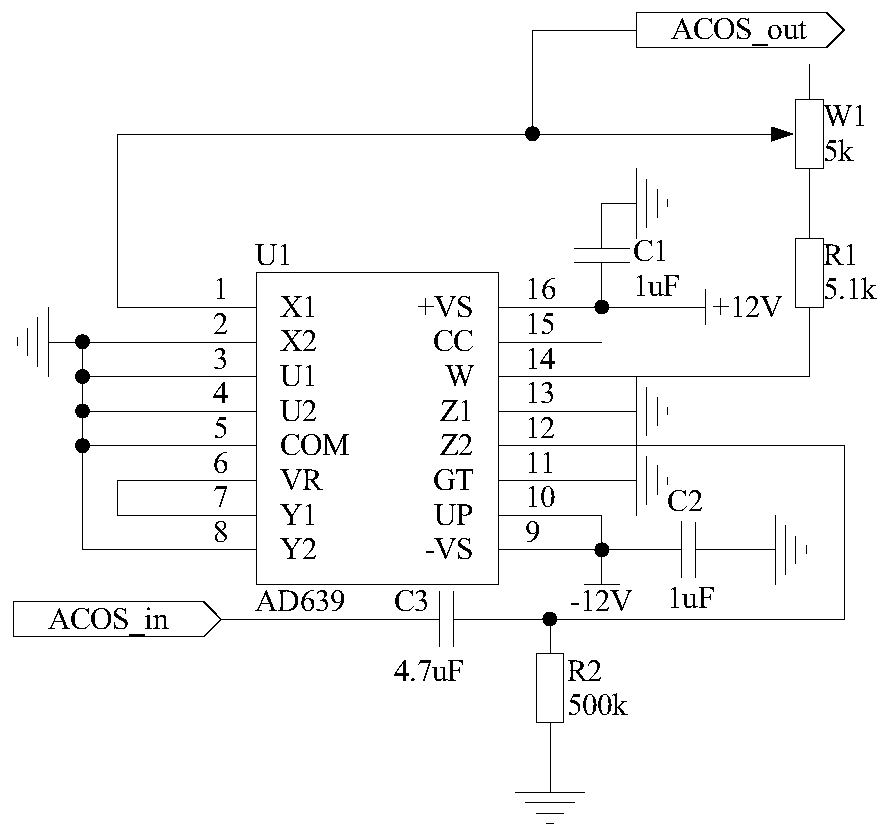

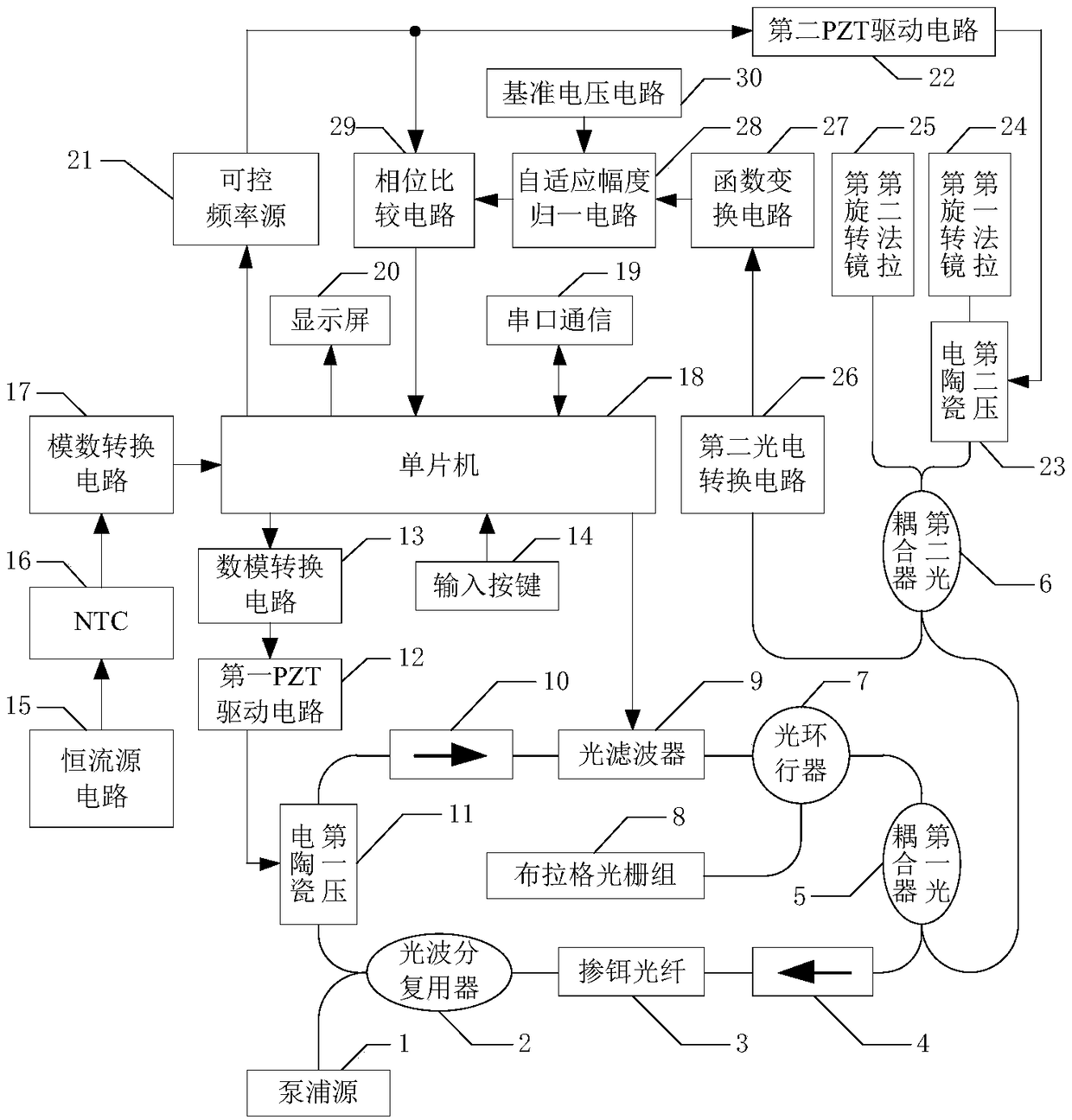

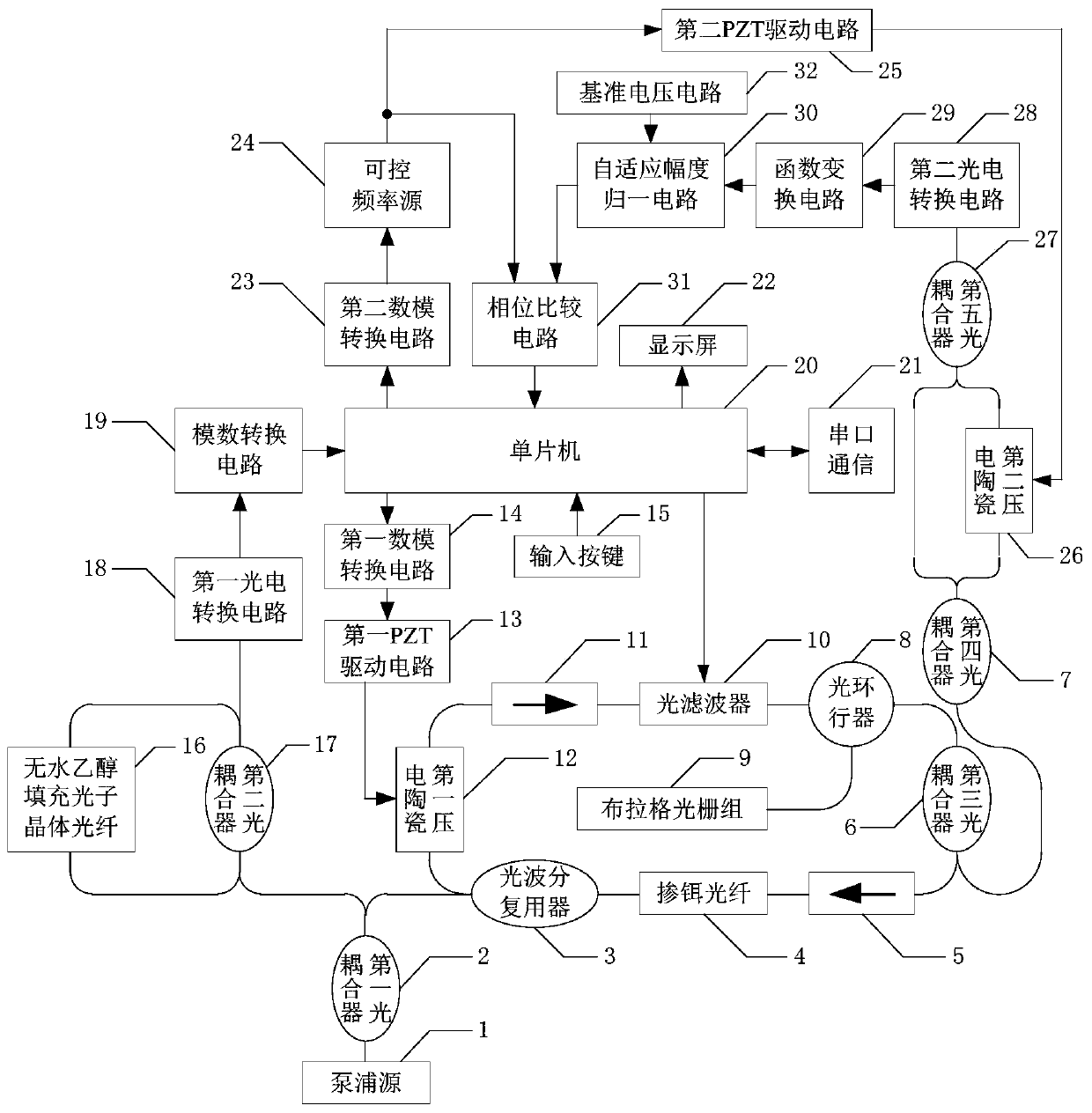

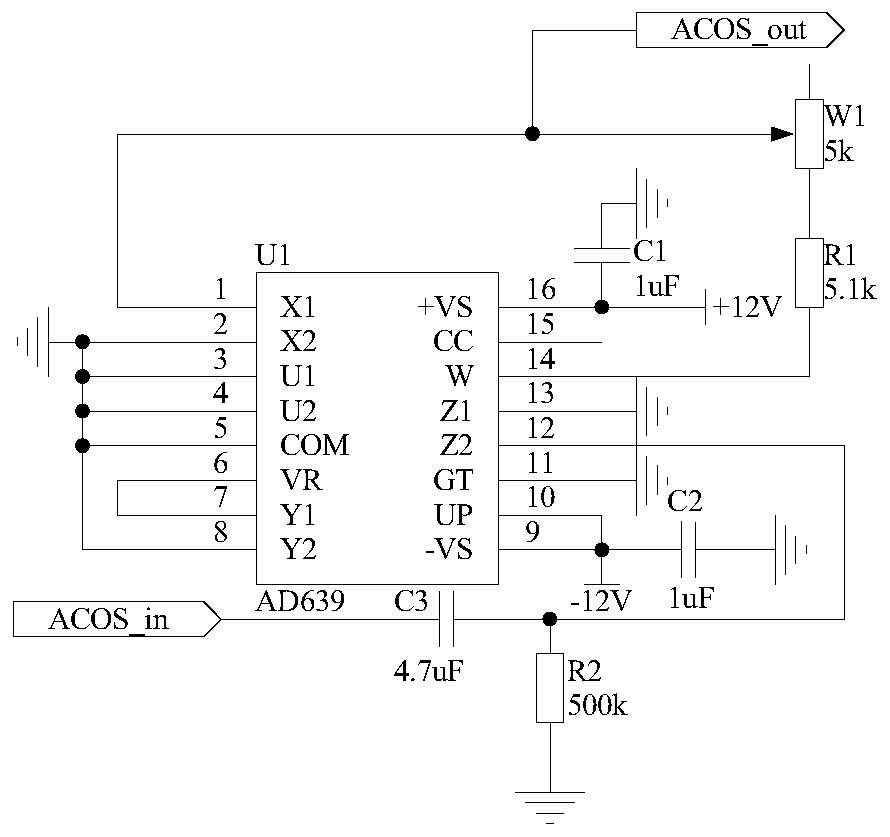

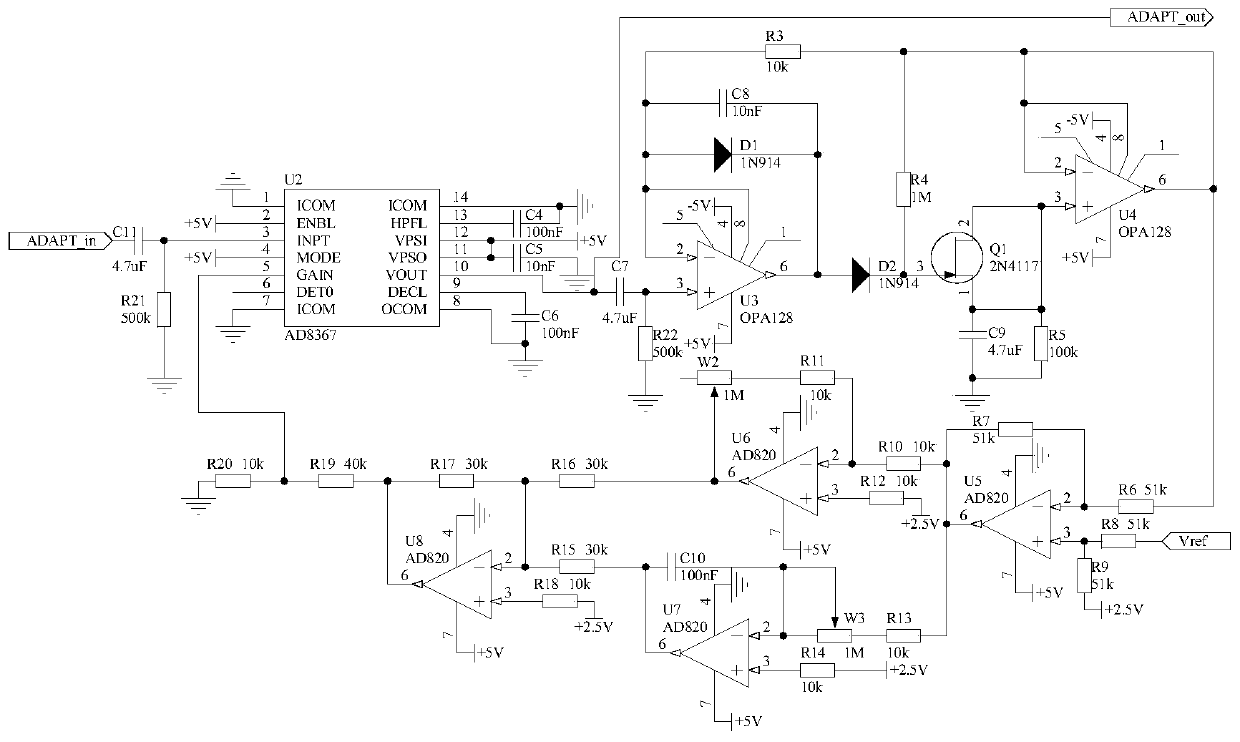

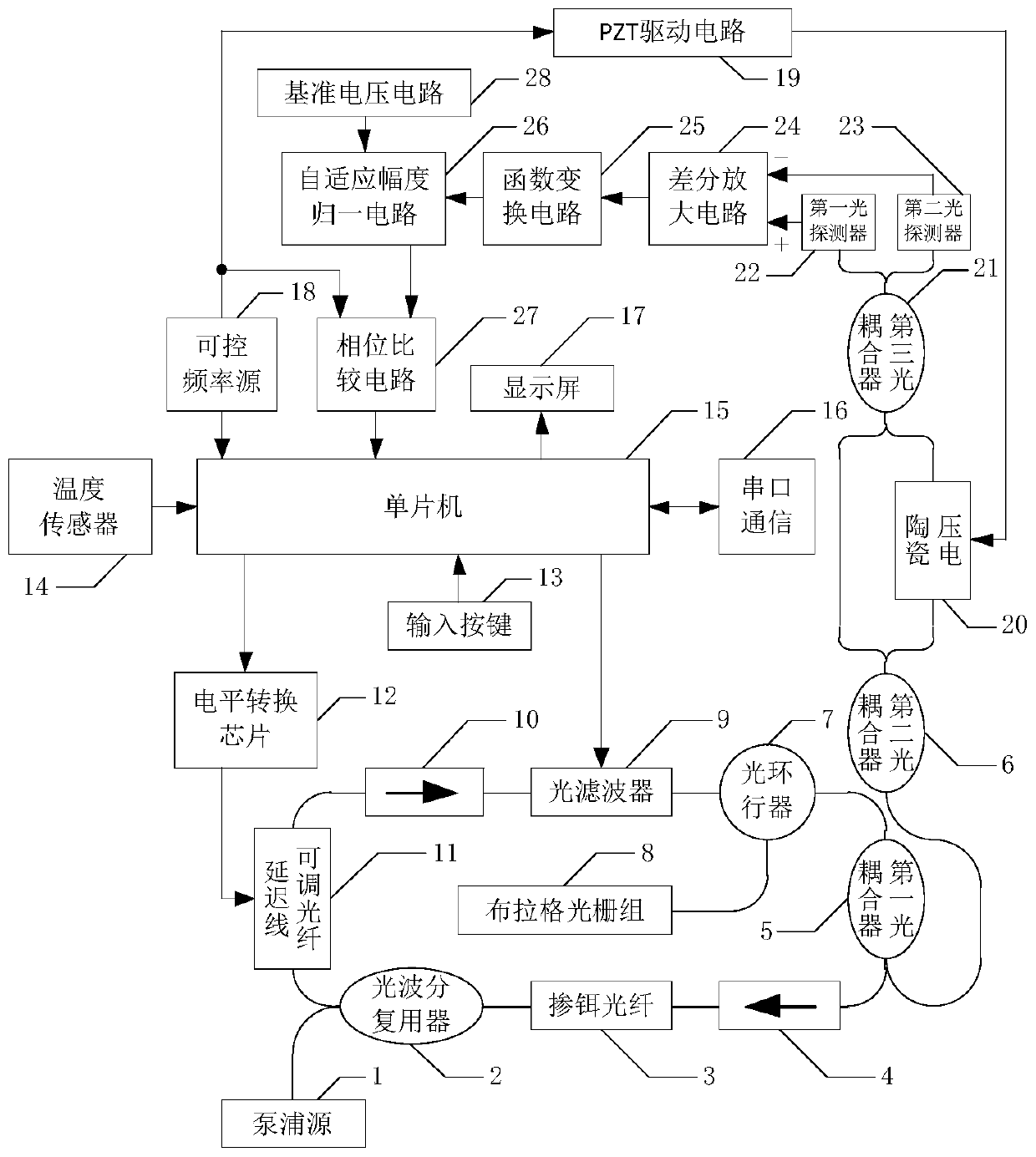

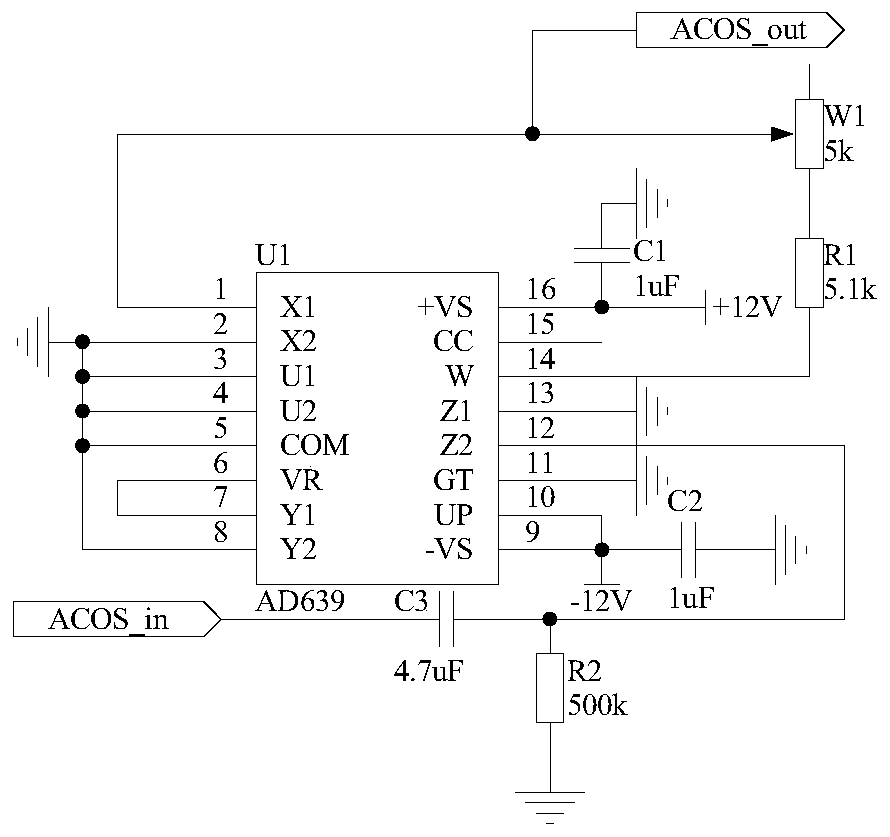

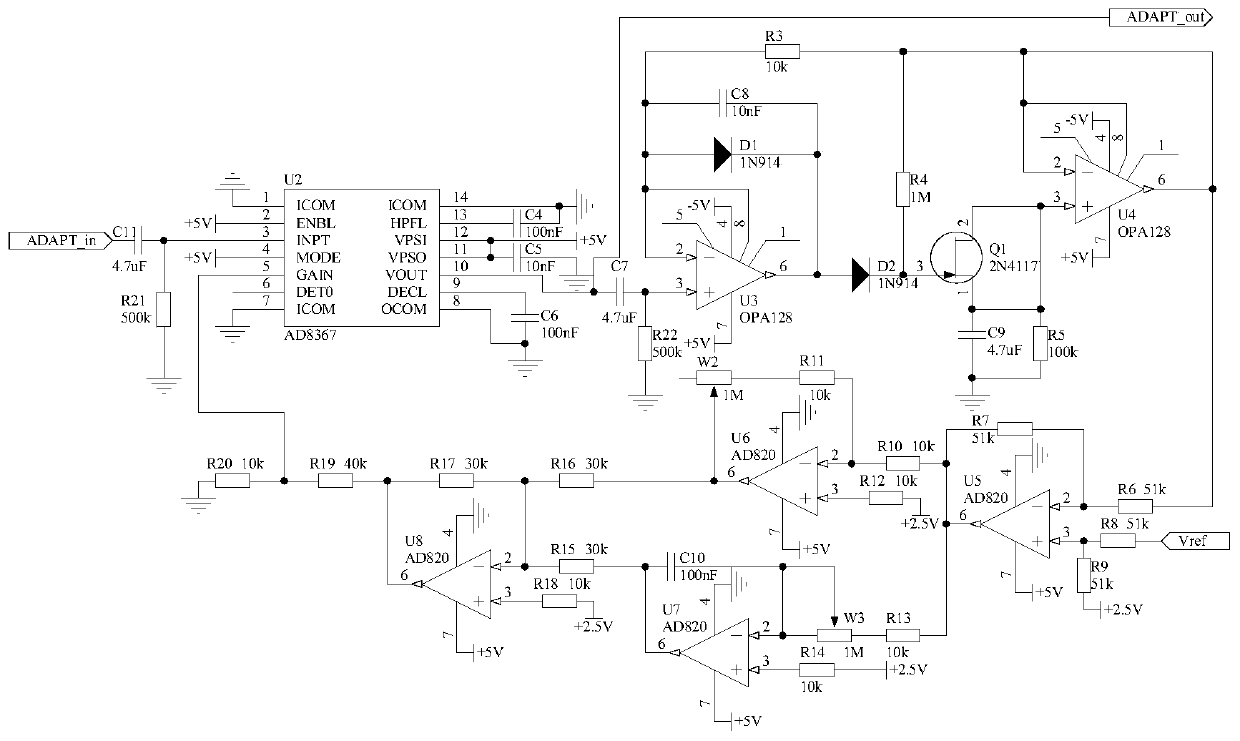

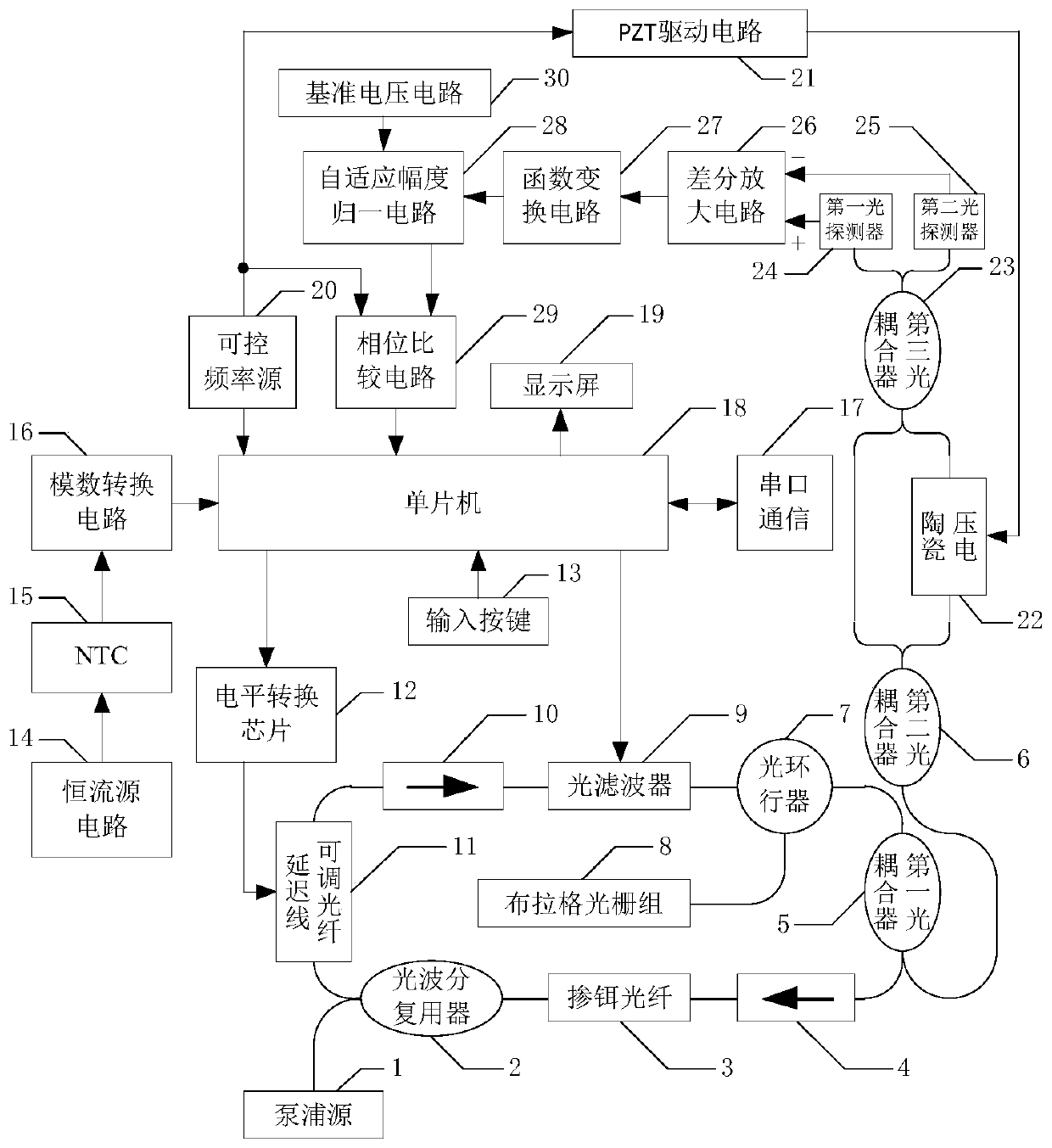

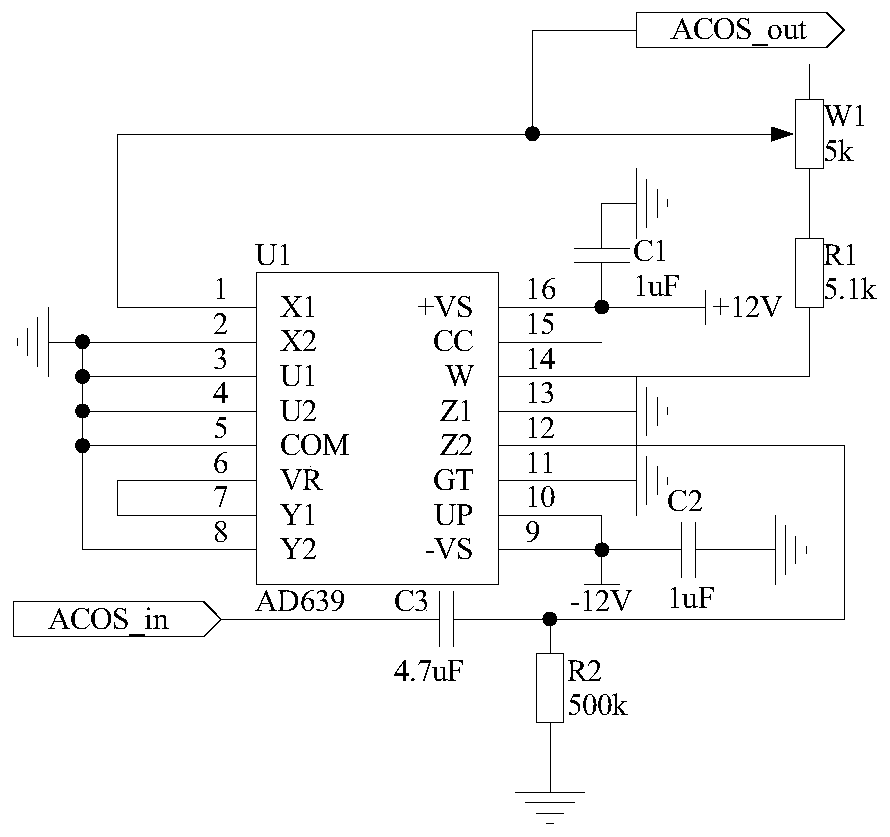

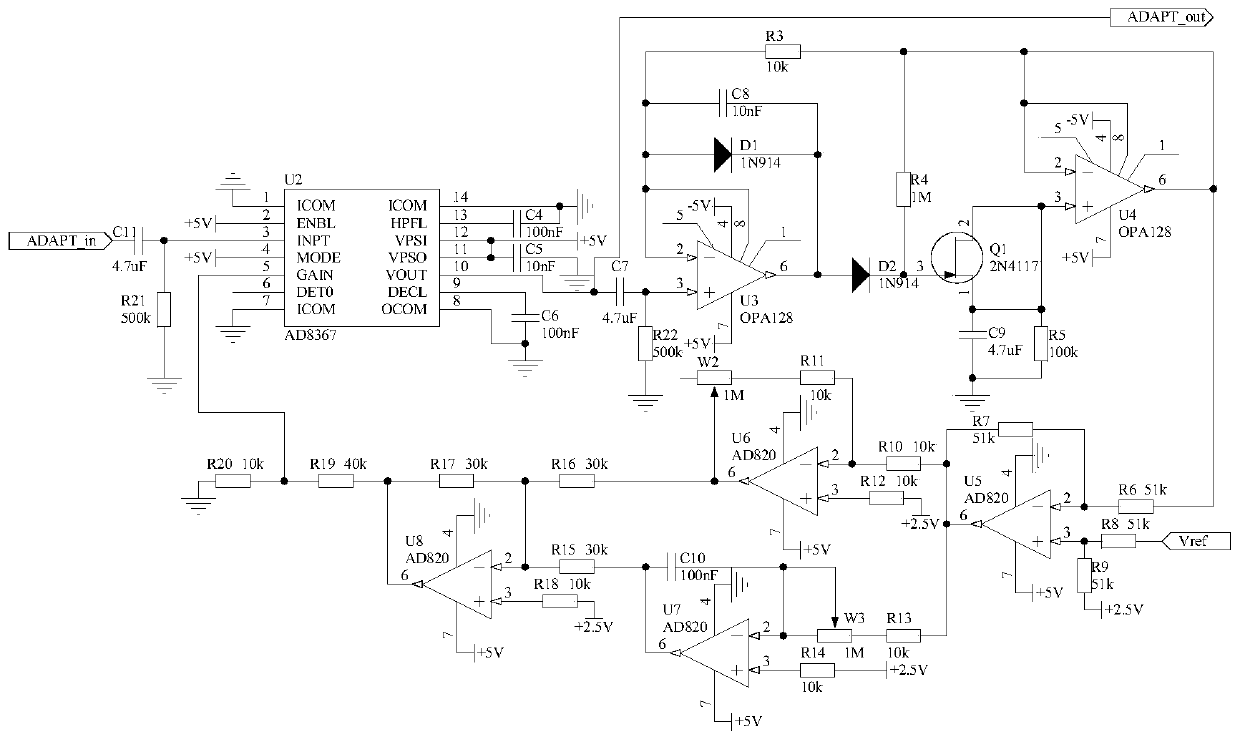

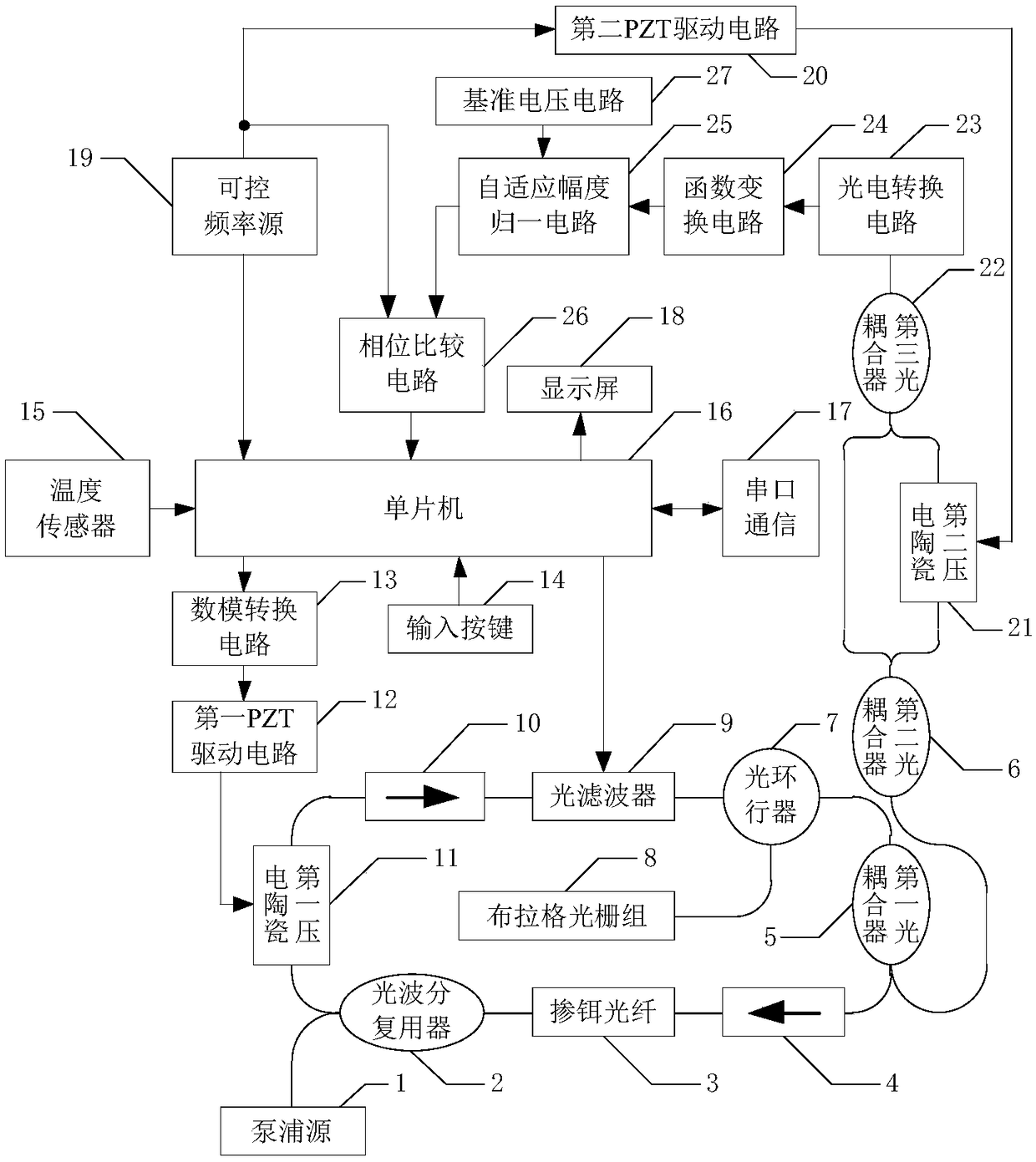

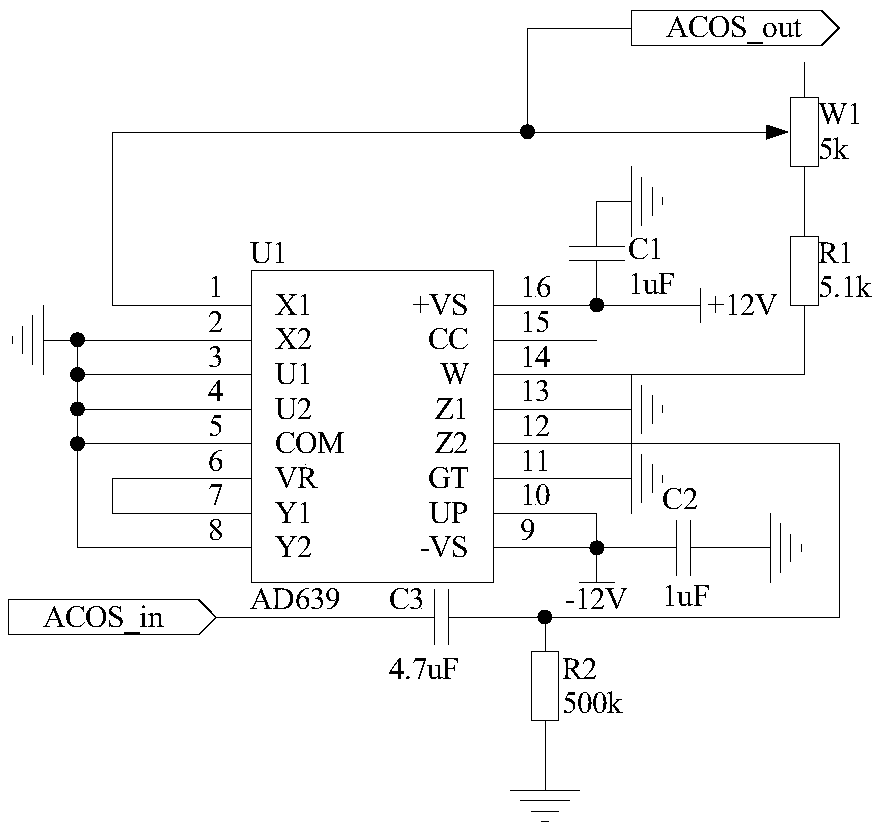

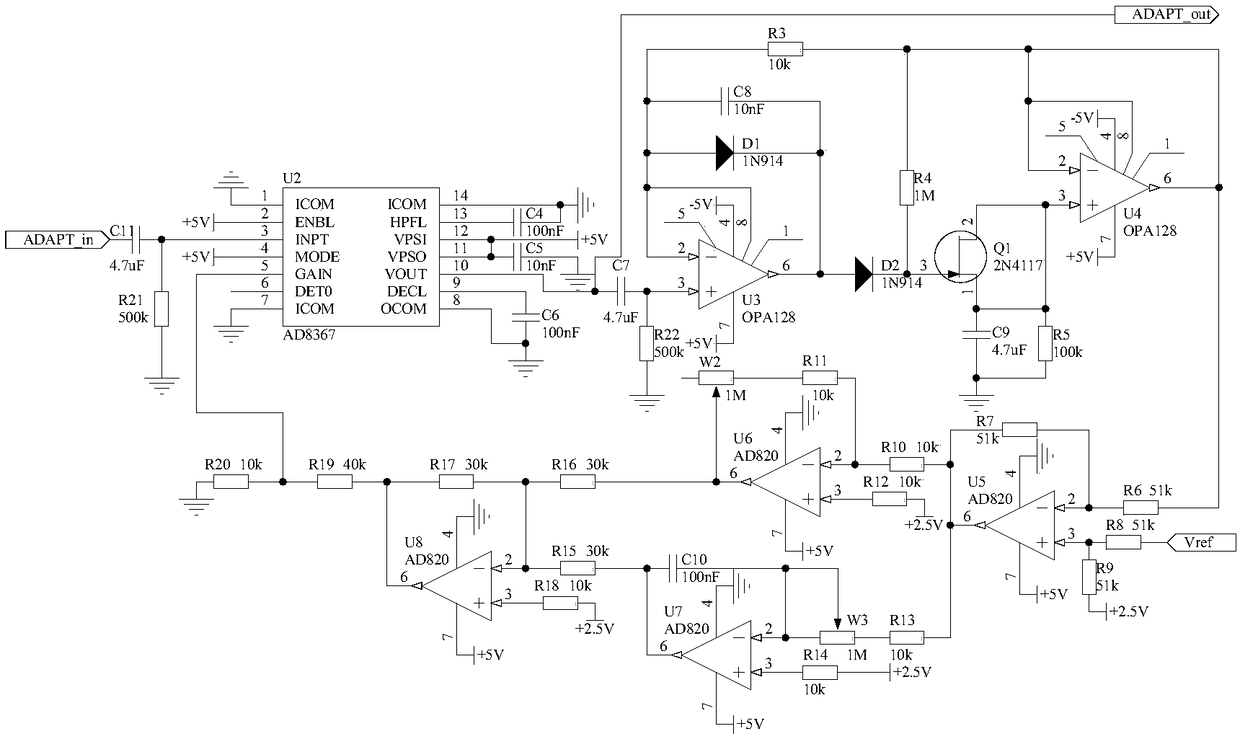

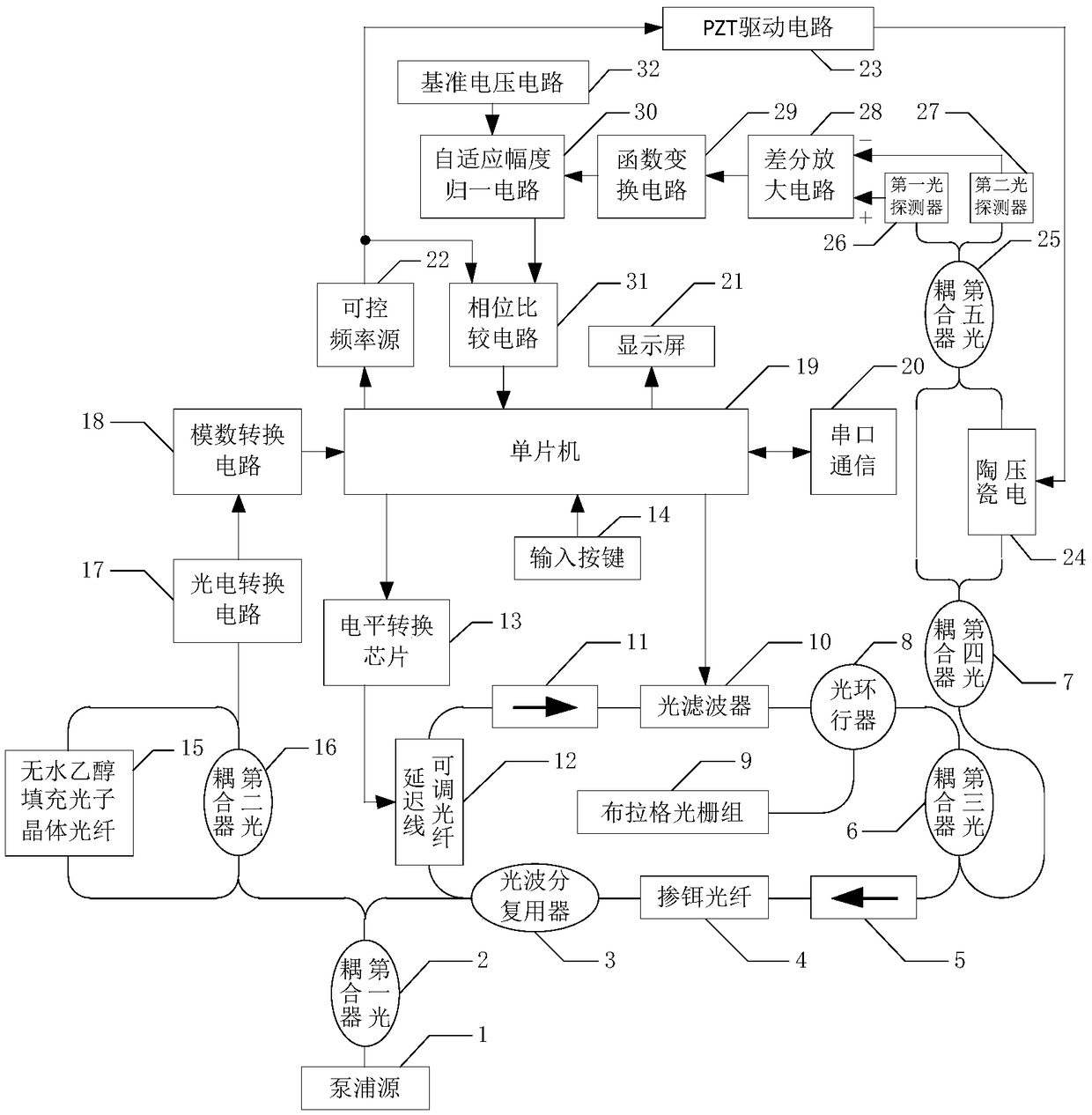

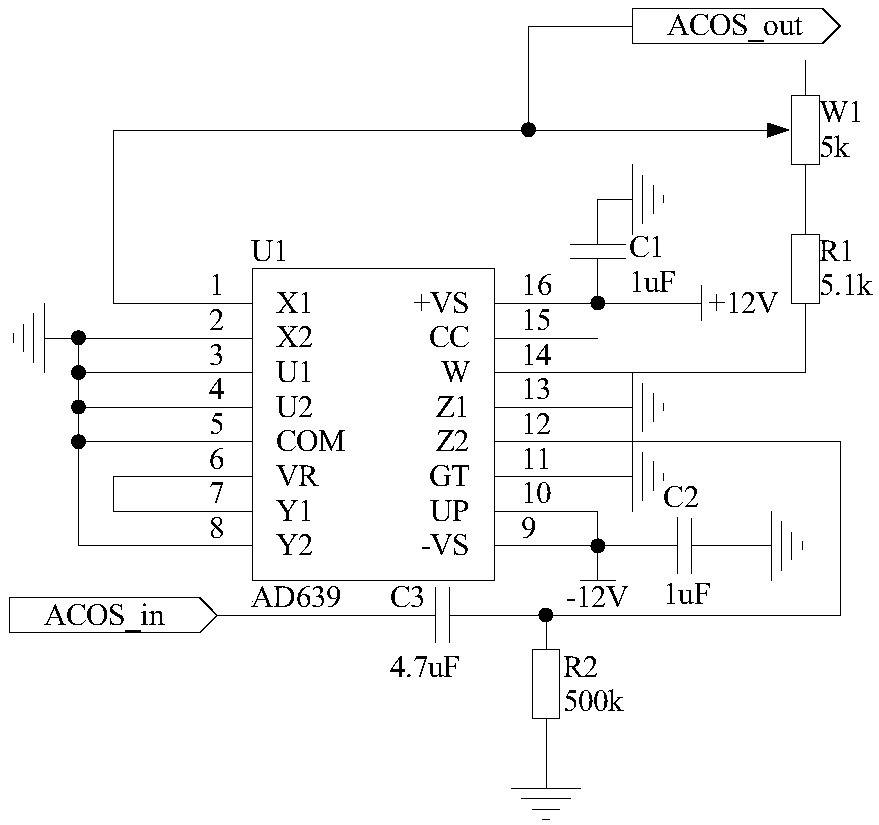

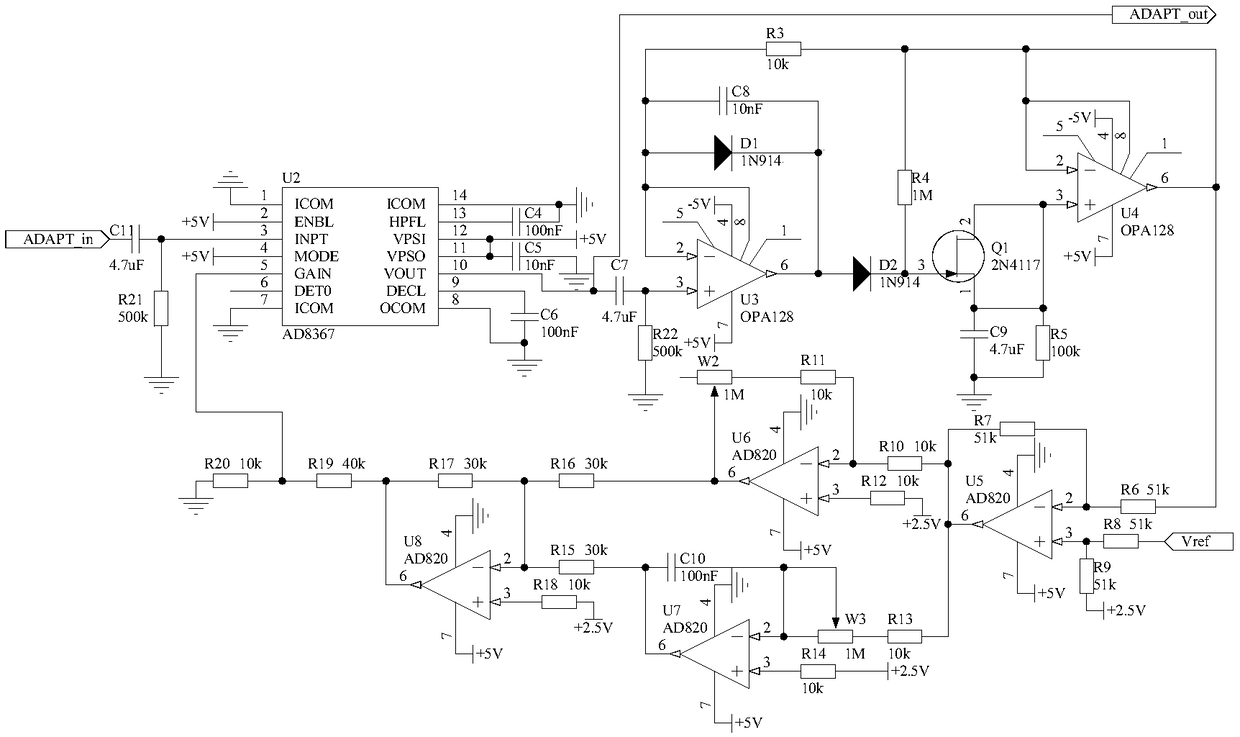

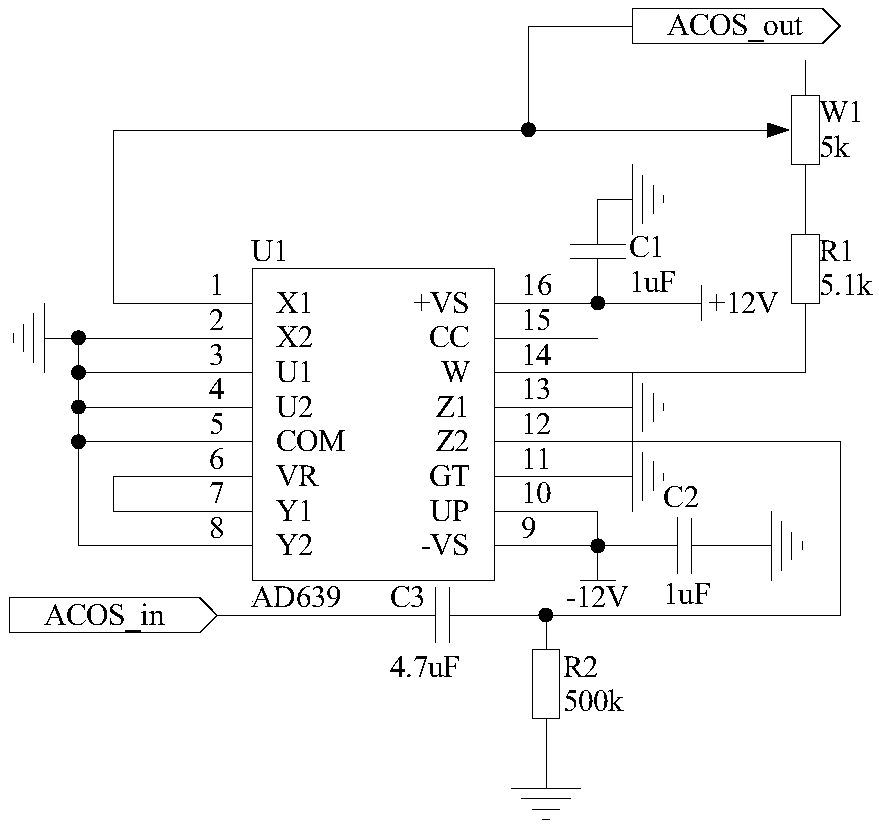

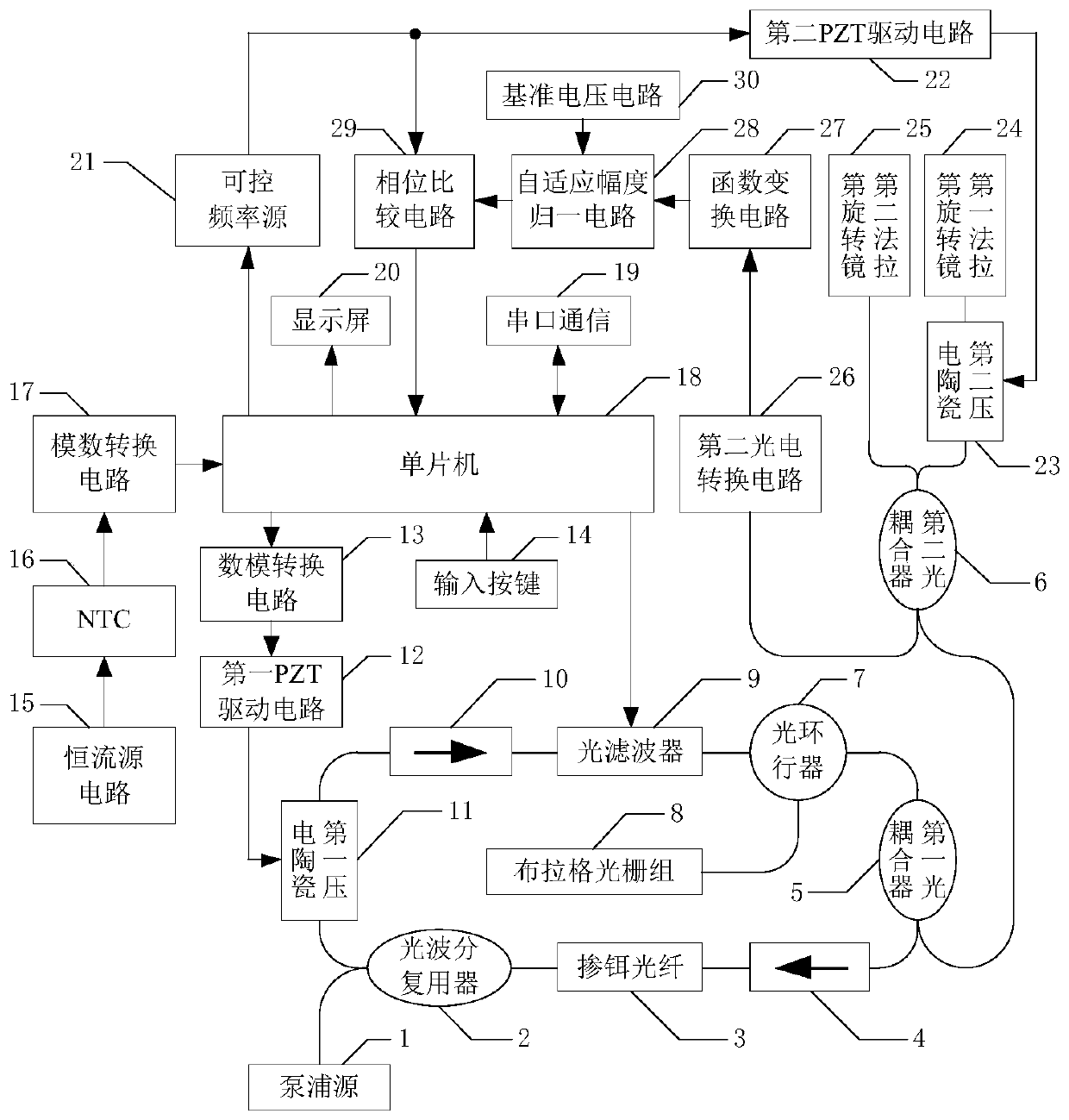

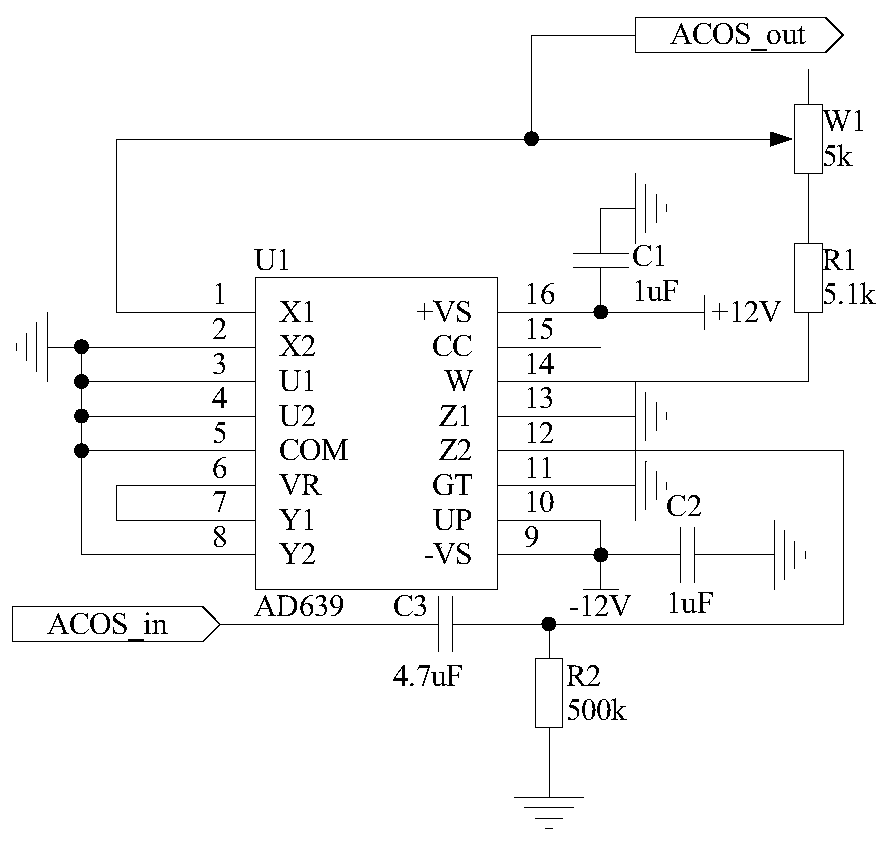

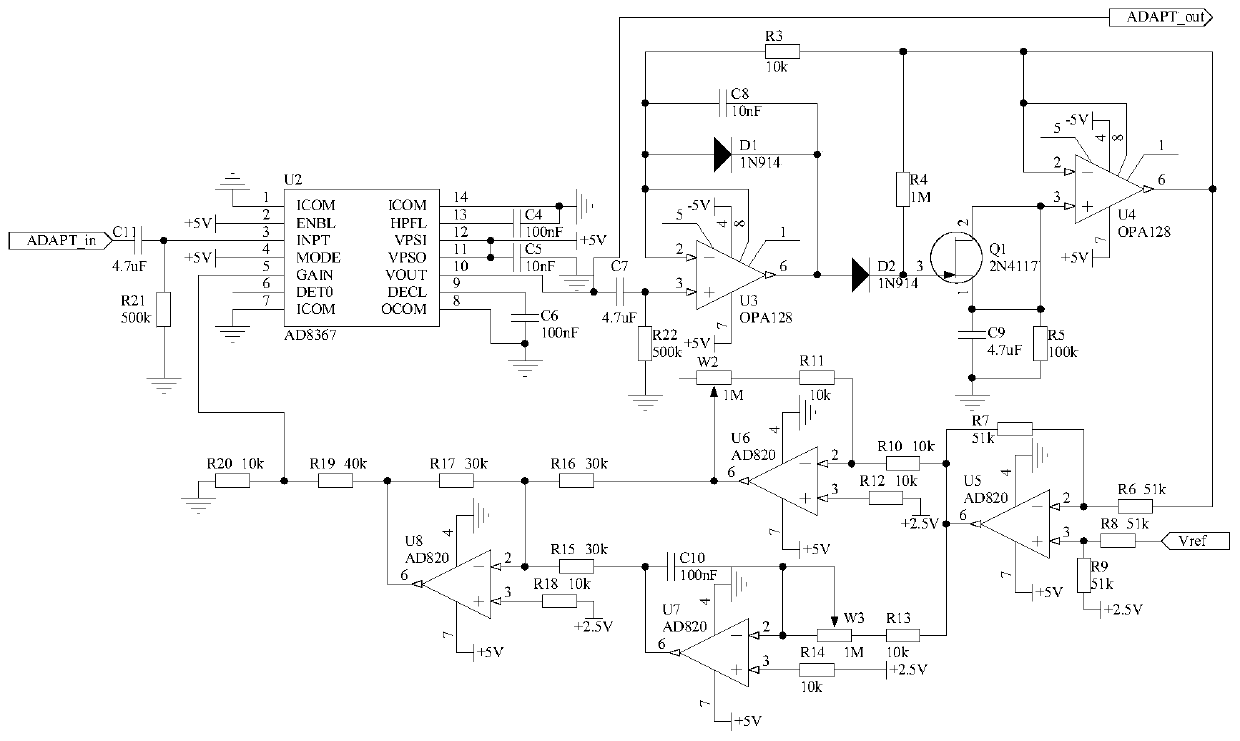

Fiber sensing system based on fiber laser

InactiveCN109141674AWork reliablyNo high frequency interferenceThermometers using physical/chemical changesActive medium shape and constructionMultiplexerVIT signals

The invention discloses a fiber sensing system based on a fiber laser, and belongs to the technical field of fiber sensors. The main structure of the system comprises a pump source (1), an optical multiplexer (2), and an Er-doped optical fiber (3). According to the invention, a sine signal is taken as a modulation signal, and no high-frequency interference can be generated, so the system is more reliable in working, is high in sensing precision, and is wide in application range.

Owner:JILIN UNIV

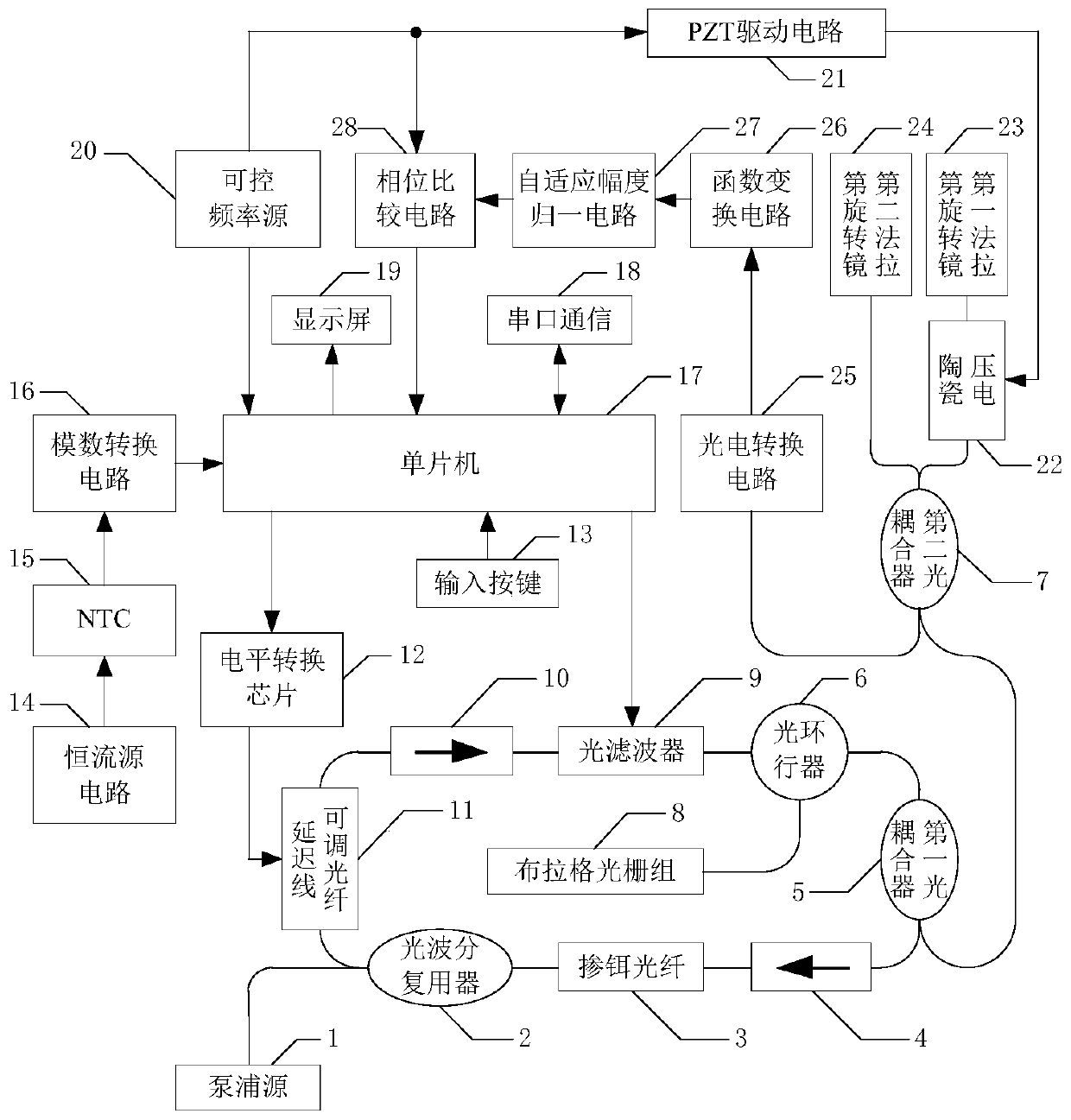

Micro-stress sensor for bridge monitoring

InactiveCN108955970AWork reliablyNo high frequency interferenceForce measurement by measuring optical property variationMultiplexerErbium doping

The invention provides a micro-stress sensor for bridge monitoring, and belongs to the technical field of optical fiber sensors. The sensor is mainly provided with a pumping source (1), an optical wavelength division multiplexer (2), and an erbium-doped optical fiber (3). The sine signal is used as a modulation signal, high-frequency interference cannot be generated, and the sensor has the advantages of being more reliable in work, and high in sensing precision.

Owner:JILIN UNIV

A PLL Applicable to Grid Voltage Unbalance and Distortion State

ActiveCN105743109BGuaranteed Steady State PerformanceFast dynamic responseVoltage-current phase anglePolyphase network asymmetry elimination/reductionCompensation effectEngineering

The invention discloses a phase-locked loop applicable to power grid voltage unbalance and distortion states, and belongs to the related technical fields of power grid voltage phase signal detection and power grid load harmonic current extraction. The phase-locked loop provided by the invention aims to solve the problem as follows: the conventional synchronous rotating reference frame based three-phase digital phase-locked loop cannot accurately detect the phase value of the three-phase voltage fundamental wave positive-sequence component under power grid voltage unbalance and distortion states; consequently, the precision of a related harmonic current extraction algorithm is lowered, and the compensation effect of a harmonic compensation apparatus is weakened. The phase-locked loop provided by the invention improves the conventional three-phase digital phase-locked loop, and a repetition controller is introduced; the repetition controller is connected with a proportional integral controller in parallel to form a new controller, so that the excellent steady-state performance of the repetition controller is combined with the excellent dynamic performance of the proportional integral controller; and therefore, the phase-locked loop has the advantages of high dynamic response, high detection precision and the like. The phase-locked loop is mainly applied to voltage phase detection under power grid voltage unbalance and distortion states.

Owner:DALIAN UNIV OF TECH

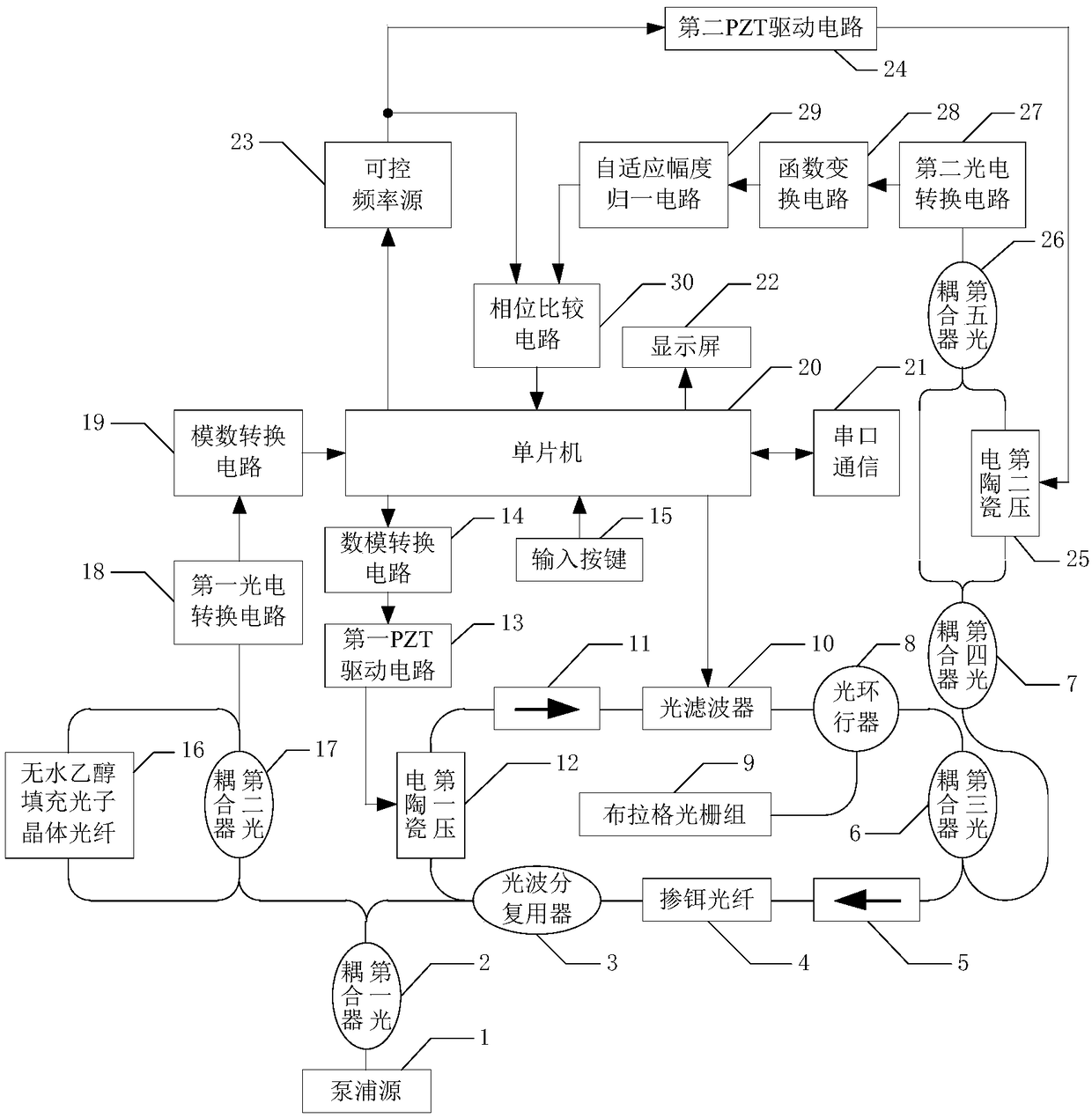

High-precision stress sensor based on Bragg fiber grating

InactiveCN109186824AWork reliablyNo high frequency interferenceForce measurement by measuring optical property variationGratingMultiplexer

A high-precision stress sensor based on Bragg fiber grating provided by the invention belongs to the technical field of optical fiber sensors. The sensor comprises the main structures of a pump source(1), a first photocoupler (2), an optical wavelength division multiplexer (3), and the like. The high-precision stress sensor provided by the invention uses a sinusoidal signal as the modulation signal without generating high-frequency interference, and has the characteristics such as more reliable work, high sensing precision and wide application range.

Owner:JILIN UNIV

A Fiber Optic Sensor Based on Michelson Interference

InactiveCN109029518BWork reliablyNo high frequency interferenceConverting sensor output opticallyMultiplexerEngineering

Owner:JILIN UNIV

High-precision temperature sensor

InactiveCN109029772AWork reliablyNo high frequency interferenceThermometers using physical/chemical changesMultiplexerOptical wavelength

The invention relates to a high-precision temperature sensor and belongs to the technical field of optical fiber sensors. The high-precision temperature sensor mainly comprises a pumping source (1), an optical wavelength division multiplexer (2), an Er-doped fiber (3) and the like. The high-precision temperature sensor provided by the invention uses a sinusoidal signal as a modulating signal, cannot produce high-frequency interference and has the characteristics of more reliable work, high sensing precision and wide application range.

Owner:JILIN UNIV

Micro stress sensor based on phase comparison

InactiveCN109238533AWork reliablyNo high frequency interferenceForce measurement by measuring optical property variationPhysicsFiber optic sensor

The invention provides a micro stress sensor based on phase comparison, and belongs to the technical field of optical fiber sensors. The main structure of the micro stress sensor comprises a pumping source (1), an optical wavelength division multiplexer (2), an erbium doped optical fiber (3), and the like. The micro stress sensor provided by the invention uses a sinusoidal signal as a modulation signal, thereby generating no high frequency interference, and having the characteristics of more reliable work, high sensing precision, wide application range, etc.

Owner:JILIN UNIV

A High Precision Stress Sensing System Based on Michelson Interference Structure

InactiveCN108827505BWork reliablyNo high frequency interferenceForce measurement by measuring optical property variationMultiplexerEngineering

The invention discloses a high-precision stress sensing system based on Michelson interference structure and belongs to the technical field of optical fiber sensors. The main structure of the high-precision stress sensing system comprises a pumping source (1), an optical wavelength division multiplexer (3), an erbium-doped optical fiber (3) and the like. The high-precision stress sensing system uses a sinusoidal signal as a modulation signal, does not generate high-frequency interference, and is reliable in operation, high in sensing precision and wide in application range.

Owner:JILIN UNIV

A Temperature Sensing System for Mine Safety Monitoring

InactiveCN109029773BWork reliablyNo high frequency interferenceThermometers using physical/chemical changesMultiplexerOptical coupler

Owner:JILIN UNIV

A High Precision Temperature Sensor

InactiveCN109029772BWork reliablyNo high frequency interferenceThermometers using physical/chemical changesMultiplexerMaterials science

A high-precision temperature sensor of the invention belongs to the technical field of optical fiber sensors. Its main structures include a pump source (1), an optical wavelength division multiplexer (2), an erbium-doped optical fiber (3) and the like. The invention uses a sinusoidal signal as a modulation signal, does not generate high-frequency interference, and has the characteristics of more reliable operation, high sensing precision, wide application range and the like.

Owner:JILIN UNIV

Phase detection and starting circuit used in multiphase clock generating circuit of high-speed serial interface

InactiveCN103001628BNovel ideaPhase detection error is smallPulse automatic controlPhase detectorFlip-flop

A phase detection and starting circuit used in a multiphase clock generating circuit of a high-speed serial interface comprises a phase detector and a starting circuit, wherein the phase detector is provided with three input ends and two output ends, the starting circuit is connected with the input end of the phase detector, and the starting circuit comprises an AND gate, a first D trigger, a second D trigger, a third D trigger, a first CML2CMOS circuit, a second CML2CMOS circuit, a third CML2CMOS circuit, a first buffer, a second buffer and a third buffer. The circuit controls initial states of clock signals entering the phase detector when the multiphase clock generating circuit starts working, so that the wrong locking and the harmonic locking of the multiphase clock generating circuit can be effectively prevented, the phase detector adopts the current mode logic technology, the working efficiency is high, and the incoming mismatching jittering is low.

Owner:SHENZHEN GRADUATE SCHOOL TSINGHUA UNIV

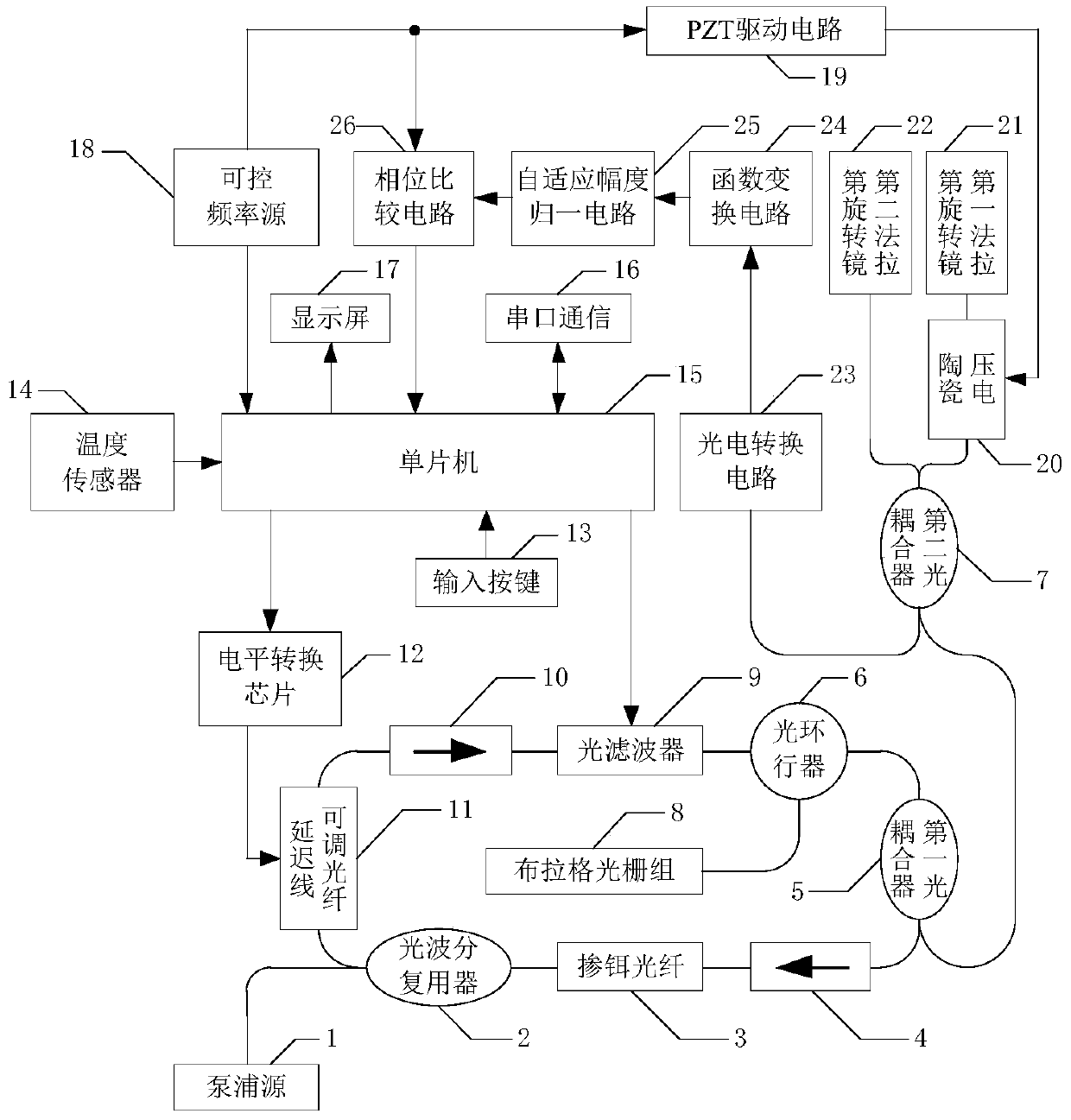

A Temperature Detection System Based on Michelson Interference Structure

InactiveCN109029775BWork reliablyNo high frequency interferenceThermometers using physical/chemical changesMultiplexerEngineering

A temperature detection system based on a Michelson interference structure of the invention belongs to the technical field of optical fiber sensors. Its main structure includes a pumping source (1), a first optical coupler (2), an optical wavelength division multiplexer (3) and the like. The invention uses a sinusoidal signal as a modulation signal, does not generate high-frequency interference, and has the characteristics of more reliable operation, high sensing precision, wide application range and the like.

Owner:JILIN UNIV

Fiber sensor based on Michelson interference

InactiveCN109029518AWork reliablyNo high frequency interferenceConverting sensor output opticallyMultiplexerMichelson interferometer

The invention discloses a fiber sensor based on Michelson interference and belongs to the technical field of the fiber sensor. A main structure of the fiber sensor comprises a pump source (1), a firstoptical coupler (2), an optical wavelength division multiplexer (3) and the like. According to the fiber sensor, a sinusoidal signal is taken as a modulation signal and high frequency interference isnot generated. The fiber sensor is characterized by relatively reliable working, high sensing precision and wide application range.

Owner:JILIN UNIV

A high-precision micro-stress sensor

InactiveCN109100063BWork reliablyNo high frequency interferenceForce measurement by measuring optical property variationMultiplexerErbium doping

The invention discloses a highly precise micro-stress sensor, and belongs to the technical field of optical fiber sensors. The main structure of the micro-stress sensor comprises a pump source (1), anoptical wavelength division multiplexer (2), an erbium doped fiber (3), and the like. According to the highly precise micro-stress sensor a sinusoidal signal is used as a modulation signal, high-frequency interference is not generated, and the micro-stress sensor has the characteristics of being more reliable in operation, high in sensing precision, wide in application range, and the like.

Owner:JILIN UNIV

A micro stress sensor based on phase comparison

InactiveCN109238533BWork reliablyNo high frequency interferenceForce measurement by measuring optical property variationMultiplexerErbium doping

The invention provides a micro stress sensor based on phase comparison, and belongs to the technical field of optical fiber sensors. The main structure of the micro stress sensor comprises a pumping source (1), an optical wavelength division multiplexer (2), an erbium doped optical fiber (3), and the like. The micro stress sensor provided by the invention uses a sinusoidal signal as a modulation signal, thereby generating no high frequency interference, and having the characteristics of more reliable work, high sensing precision, wide application range, etc.

Owner:JILIN UNIV

Temperature sensor based on Mach-Zehnder interference structure

InactiveCN109029776AWork reliablyNo high frequency interferenceThermometers using physical/chemical changesMultiplexerFiber optic sensor

The invention discloses a temperature sensor based on a Mach-Zehnder interference structure, and belongs to the technical field of optical fiber sensors. The main structure of the temperature sensor comprises a pumping source (1), an optical wavelength division multiplexer (2), an Er-doped optical fiber. By use of the temperature sensor, a sinusoidal signal is taken as a modulation signal, no high-frequency interference is generated, and the temperature sensor has the characteristics of being reliable in working, high in sensing accuracy, wide in application range and the like.

Owner:JILIN UNIV

Temperature detection system based on Michelson interference structure

InactiveCN109029775AWork reliablyPhase detection error is smallThermometers using physical/chemical changesOptical couplerPhysics

The invention relates to a temperature detection system based on a Michelson interference structure and belongs to the technical field of optical fiber sensors. The temperature detection system mainlycomprises a pumping source (1), a first optical coupler (2), an optical wavelength division multiplexer (3) and the like. The temperature detection system provided by the invention uses a sinusoidalsignal as a modulating signal, can not produce high-frequency interference and has the characteristics of more reliable work, high sensing precision and wide application range.

Owner:JILIN UNIV

A multipurpose fiber optic sensor

Owner:JILIN UNIV

A Fiber Optic Sensor Based on Sine Wave Modulation

InactiveCN109084817BWork reliablyNo high frequency interferenceConverting sensor output opticallyMultiplexerErbium doping

The invention discloses an optical fiber sensor based on sine wave modulation, and belongs to the technical field of optical fiber sensors. The main structure is a pump source (1), an optical wavelength division multiplexer (3), an erbium doped fiber (3) and the like. According to the optical fiber sensor based on sine wave modulation, a sinusoidal signal is used as a modulation signal, high-frequency interference is not generated, and the invention has the characteristics of being more reliable in operation, high in sensing precision, wide in application range and the like.

Owner:JILIN UNIV

A High-Precision Stress Sensor Based on Fiber Bragg Grating

InactiveCN109186824BWork reliablyNo high frequency interferenceForce measurement by measuring optical property variationGratingMultiplexer

A high-precision stress sensor based on Bragg fiber grating provided by the invention belongs to the technical field of optical fiber sensors. The sensor comprises the main structures of a pump source(1), a first photocoupler (2), an optical wavelength division multiplexer (3), and the like. The high-precision stress sensor provided by the invention uses a sinusoidal signal as the modulation signal without generating high-frequency interference, and has the characteristics such as more reliable work, high sensing precision and wide application range.

Owner:JILIN UNIV

Multipoint temperature sensing system composed of fiber Bragg grating

InactiveCN109029774AWork reliablyNo high frequency interferenceThermometers using physical/chemical changesGratingFiber Bragg grating

The invention discloses a multipoint temperature sensing system composed of a fiber Bragg grating and belongs to the technical field of a fiber sensor. A main structure of the multipoint temperature sensing system comprises a pump source (1), an optical wavelength division multiplexer (2), an erbium-doped fiber (3) and the like. According to the multipoint temperature sensing system, a sinusoidalsignal is taken as a modulation signal and high frequency interference is not generated. The multipoint temperature sensing system is characterized by relatively reliable working, high sensing precision and wide application range.

Owner:JILIN UNIV

A Stress Sensor Based on Mach-Zehnder Interference Structure

InactiveCN109029806BWork reliablyNo high frequency interferenceForce measurement by measuring optical property variationMultiplexerOptical coupler

The invention discloses a stress sensor based on a Mach-Zehnder interference structure, and belongs to the technical field of optical fiber sensors. The main structure of the stress sensor comprises apumping source (1), a first optical coupler (2), an optical wavelength division multiplexer (3) and the like. By use of the stress sensor, a sinusoidal signal is taken as a modulation signal, no high-frequency interference is generated, and the stress sensor has the characteristics of being reliable in working, high in sensing accuracy, wide in application range and the like.

Owner:JILIN UNIV

A fiber optic sensing system based on fiber laser

InactiveCN109141674BWork reliablyNo high frequency interferenceThermometers using physical/chemical changesActive medium shape and constructionMultiplexerErbium lasers

The invention relates to an optical fiber sensing system based on an optical fiber laser and belongs to the technical field of optical fiber sensors. Its main structures include a pump source (1), an optical wavelength division multiplexer (2), an erbium-doped optical fiber (3) and the like. The invention uses a sinusoidal signal as a modulation signal, does not generate high-frequency interference, and has the characteristics of more reliable operation, high sensing precision, wide application range and the like.

Owner:JILIN UNIV

A micro-stress sensor for bridge monitoring

InactiveCN108955970BWork reliablyNo high frequency interferenceForce measurement by measuring optical property variationMultiplexerMaterials science

The invention provides a micro-stress sensor for bridge monitoring, and belongs to the technical field of optical fiber sensors. The sensor is mainly provided with a pumping source (1), an optical wavelength division multiplexer (2), and an erbium-doped optical fiber (3). The sine signal is used as a modulation signal, high-frequency interference cannot be generated, and the sensor has the advantages of being more reliable in work, and high in sensing precision.

Owner:JILIN UNIV

Temperature detection device used in severe environment

InactiveCN109029771AWork reliablyNo high frequency interferenceThermometers using physical/chemical changesMultiplexerFiber optic sensor

The invention relates to a temperature detection device used in a severe environment and belongs to the technical field of optical fiber sensors. The temperature detection device mainly comprises a pumping source (1), an optical wavelength division multiplexer (2), an Er-doped fiber (3) and the like. The temperature detection device provided by the invention uses a sinusoidal signal as a modulating signal, can not produce high-frequency interference and has the characteristics of more reliable work and high sensing precision.

Owner:JILIN UNIV

Temperature sensing system used for mine safety monitoring

InactiveCN109029773AWork reliablyNo high frequency interferenceThermometers using physical/chemical changesMultiplexerEngineering

The invention relates to a temperature sensing system used for mine safety monitoring and belongs to the technical field of optical fiber sensors. The temperature sensing system mainly comprises a pumping source (1), a first optical coupler (2), an optical wavelength division multiplexer (3) and the like. The temperature sensing system provided by the invention uses a sinusoidal signal as a modulating signal, can not produce high-frequency interference and has the characteristics of more reliable work and high sensing precision.

Owner:JILIN UNIV

High-precision optical fiber sensor based on Mach-Zehnder interference structure

InactiveCN109029517AWork reliablyNo high frequency interferenceConverting sensor output opticallyMultiplexerOptical coupler

The invention relates to a high-precision optical fiber sensor based on a Mach-Zehnder interference structure and belongs to the technical field of optical fiber sensors. The high-precision optical fiber sensor mainly comprises a pumping source (1), a first optical coupler (2), an optical wavelength division multiplexer (3) and the like. The high-precision optical fiber sensor provided by the invention uses a sinusoidal signal as a modulating signal, can not produce high-frequency interference and has the characteristics of more reliable work, high sensing precision and wide application range.

Owner:JILIN UNIV