Method for manufacturing grid structure of semiconductor device

A technology of gate structure and manufacturing method, which is applied in the field of gate structure manufacturing of complementary metal oxide semiconductor devices, and can solve problems such as depression of active region and LDD region, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The invention discloses a method for manufacturing a gate structure of a semiconductor device. It has high precision for etching gate oxide layer of 65nm and below. The method can be used to manufacture a semiconductor device with an extremely thin gate oxide layer of an ultra-large-scale integrated circuit (ULSI).

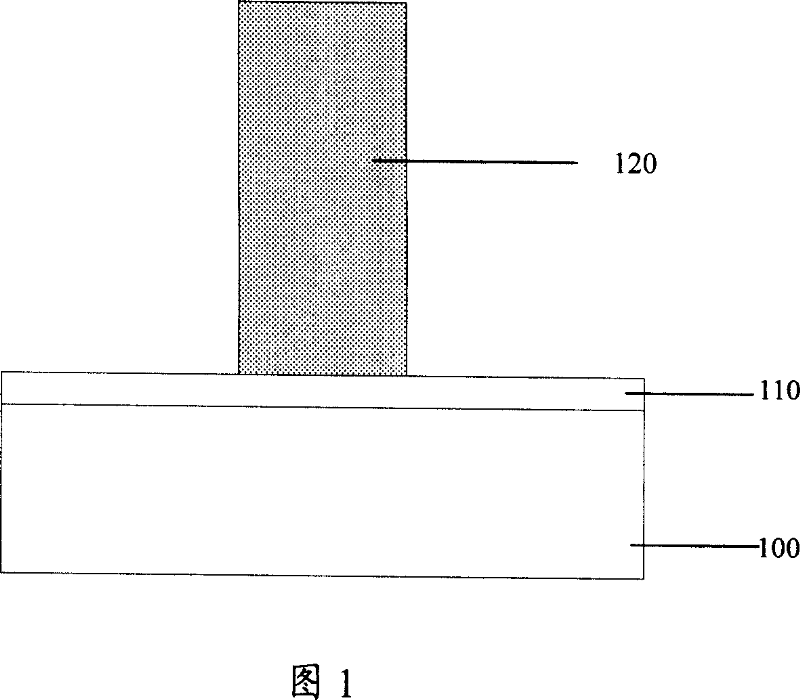

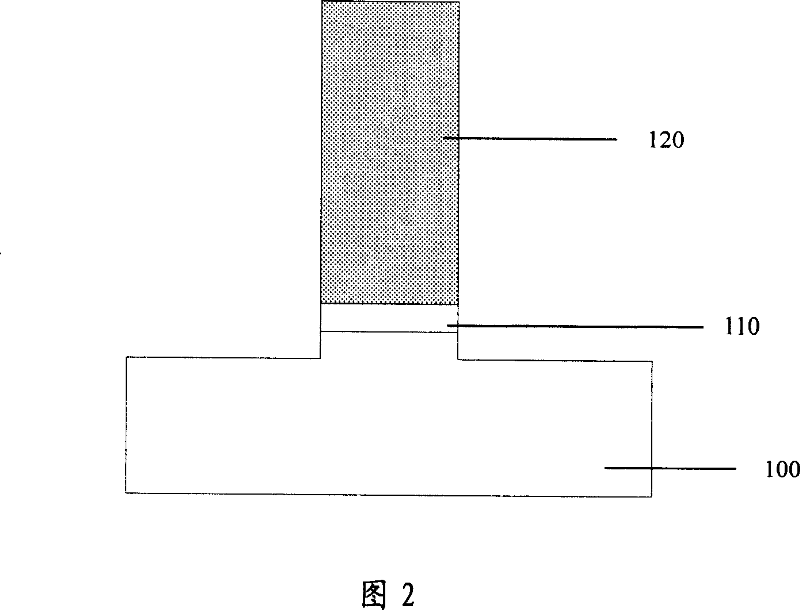

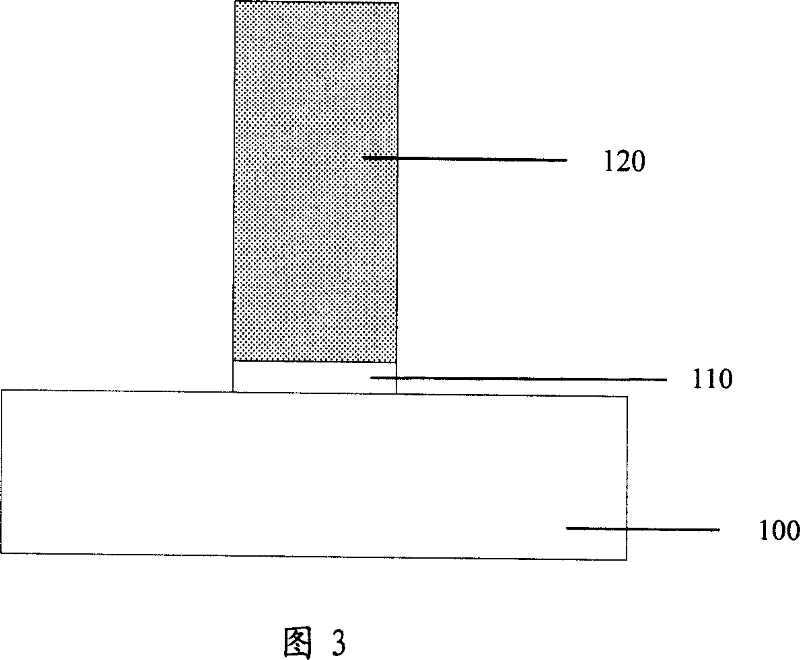

[0025] The present invention also includes a manufacturing method of a field effect transistor, such as a complementary metal oxide semiconductor (CMOS) field effect transistor, which includes a metal gate electrode and an ultra-thin gate dielectric layer (such as 10-20 Ȧ). FIG. 1 is a schematic diagram of a gate structure of a semiconductor device. As shown in FIG. 1 , a gate oxide layer 110 and a gate electrode layer 120 are formed on a substrate 100 . The process flow includes the process done on the thin film layer during the gate fabrication process. The photolithography process and its sub-processes (such as exposure, glue coating, substrate cleani...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More