Flip-attached and underfilled stacked semiconductor devices

A semiconductor and substrate technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of chip passivation layer cracks, solder joint delamination, crack propagation circuit structure, etc., to achieve The effect of reducing thermomechanical stress, increasing throughput, and simplifying process flow

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

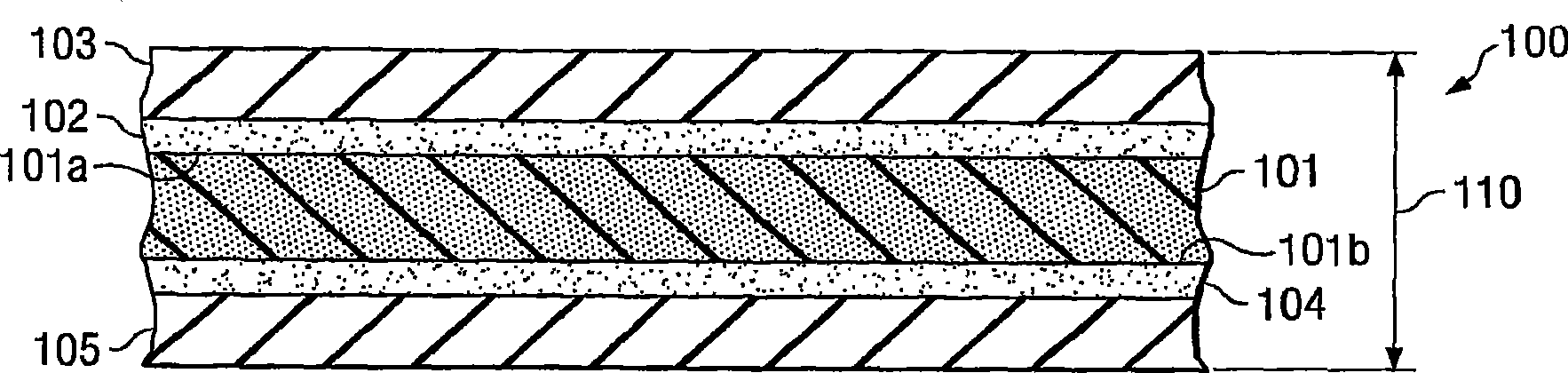

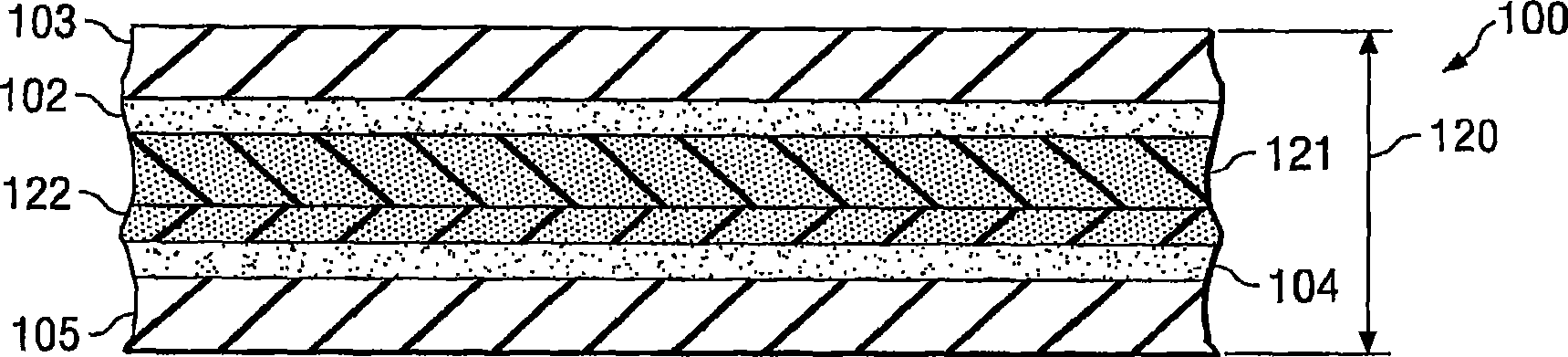

[0023] exist Figure 1A One embodiment of the present invention is depicted in a schematic cross-section of a strip (generally indicated as 100 ), which is used as a carrier and especially in a semiconductor device assembly. The strip 100 consists of a base plate 101 of polymeric material, preferably thermoplastic, having a thickness ranging from about 25 to 450 μm; for some devices said thickness can reach about 800 μm. Preferred thermoplastic chassis materials include: long chain polyimide plus acrylic or silicone, long chain polyethylene plus acrylic, and long chain polypropylene plus acrylic. Preferably, the backplane material is chosen such that it softens and enters a low viscosity or liquid phase in the same temperature range required to reflow components embedded in tape (see below). For example, this temperature range includes the melting temperature of the solder selected for assembling the device. A technical advantage is that, when the base plate is chosen from th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com