Method for preparing high-dielectric-coefficient grid medium membrane hafnium silicon oxygen nitrogen

A high dielectric constant, hafnium silicon oxygen nitrogen technology, which is applied in the manufacture of circuits, electrical components, semiconductor/solid state devices, etc., can solve the problems of increased power consumption and increased leakage of gate dielectrics, and achieves low leakage current and good interface. , the effect of low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

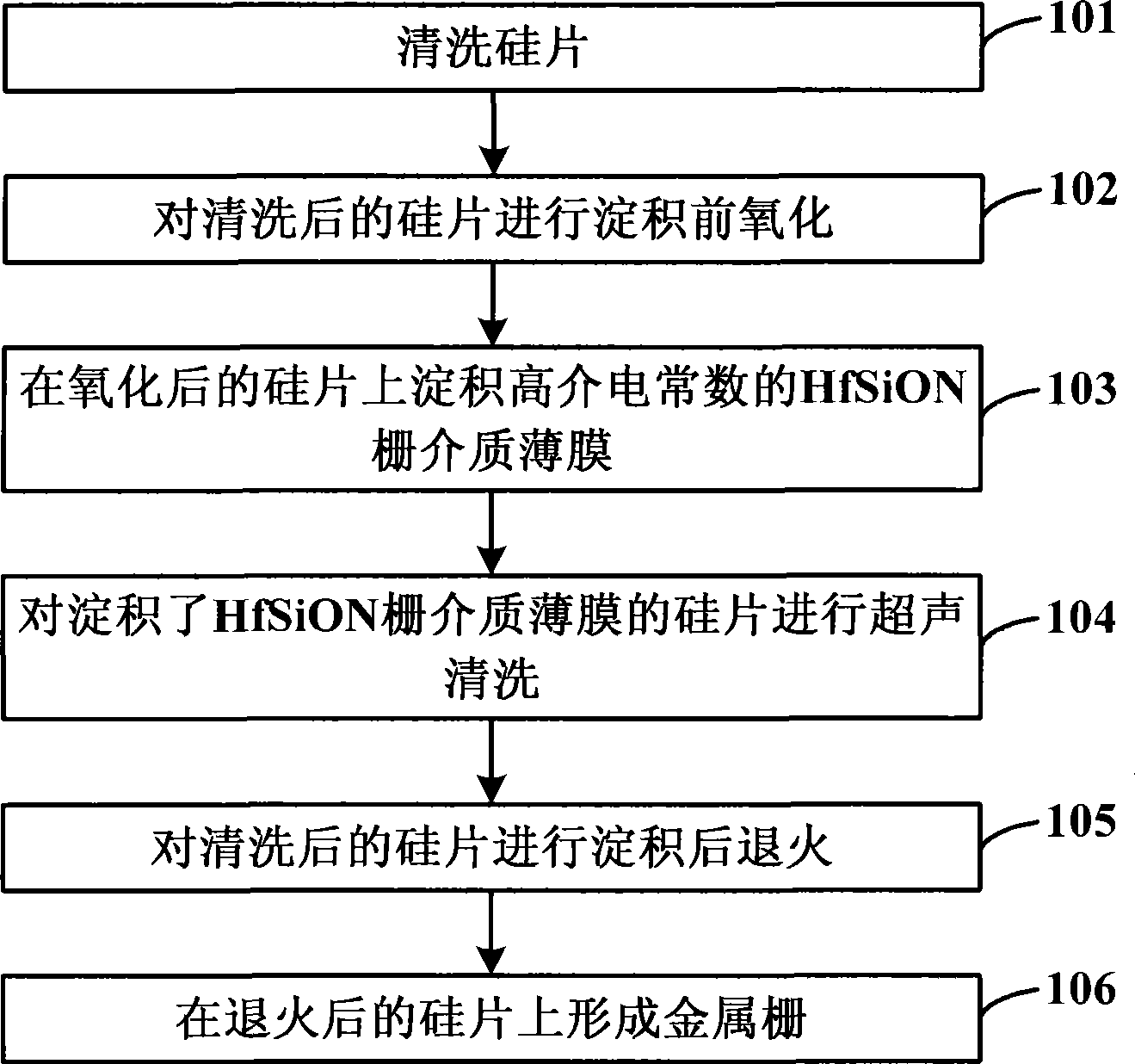

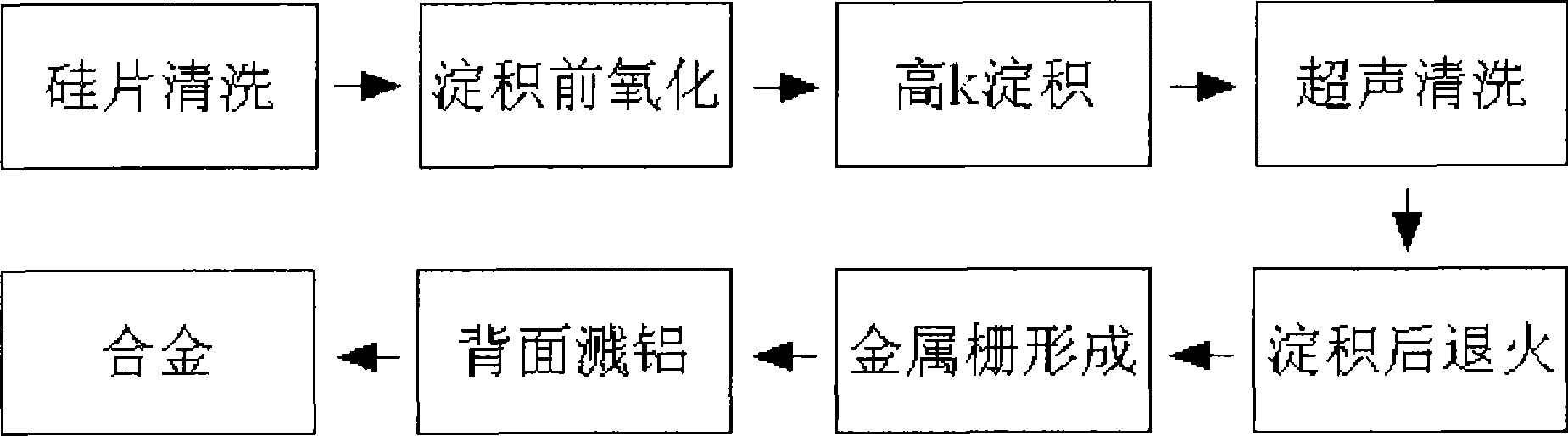

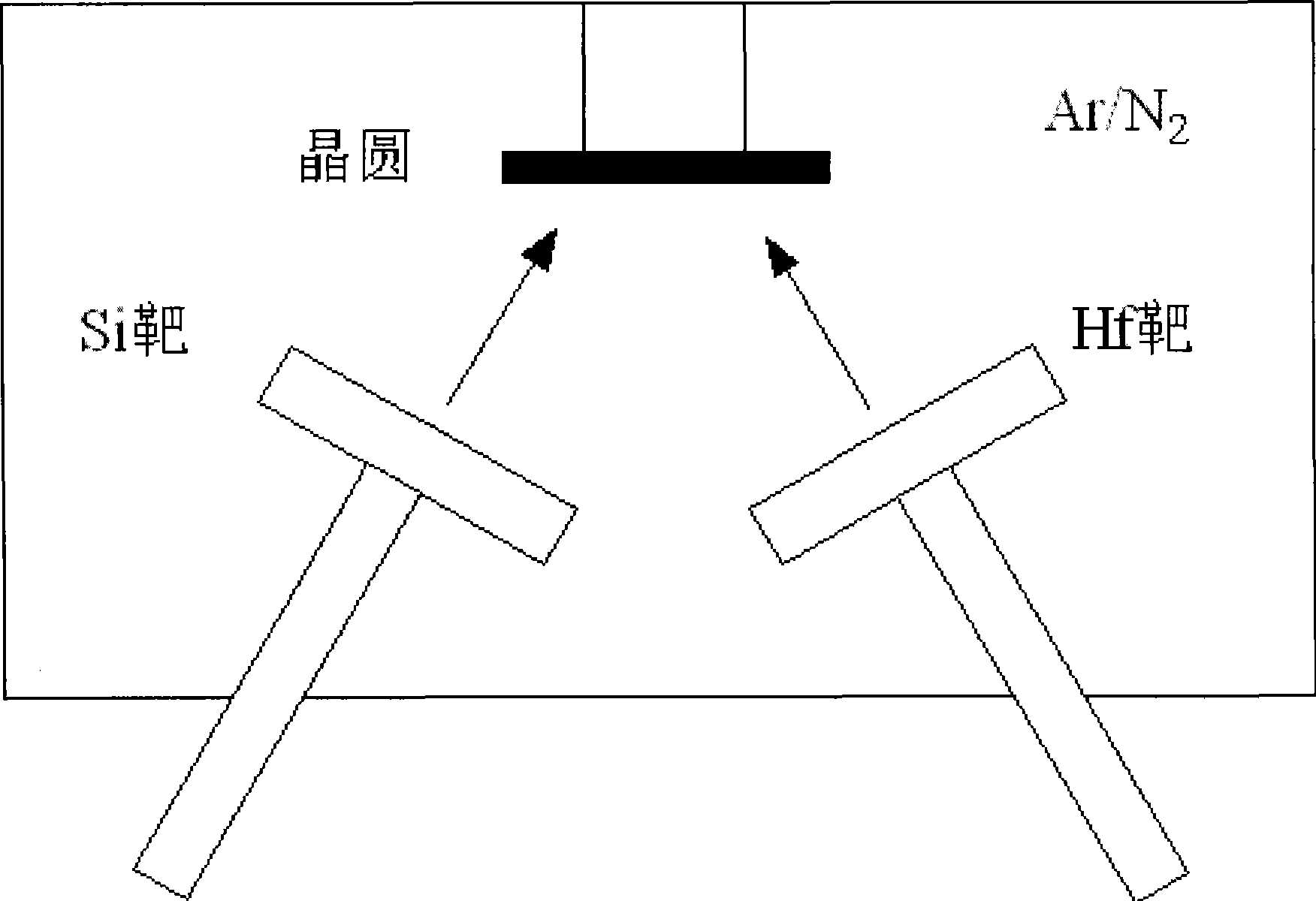

[0037] The present invention adopts the magnetron sputtering process to prepare hafnium silicon oxygen nitrogen (HfSiON) high dielectric constant gate dielectric film. Alcohol / water solution soaked at room temperature, rinsed with deionized water, put into the furnace immediately after drying, grew the interface layer by rapid thermal annealing, and used magnetron sputtering technology to alternately sputter hafnium ( Hf) target and silicon (Si) target are deposited to form HfSiON high dielectric constant gate dielectric film. After deposition, rapid thermal annealing is performed to complete the HfSiON high dielectric constant gate dielectric film, and then metal gate electrodes are formed for electrical measurement.

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More