Production method for through wafer interconnection construction

An interconnection structure and through-silicon via technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as increased cost, long working hours, and excess, to alleviate thermal mismatch, reduce parasitic capacitance, reduce Effects of thermomechanical stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

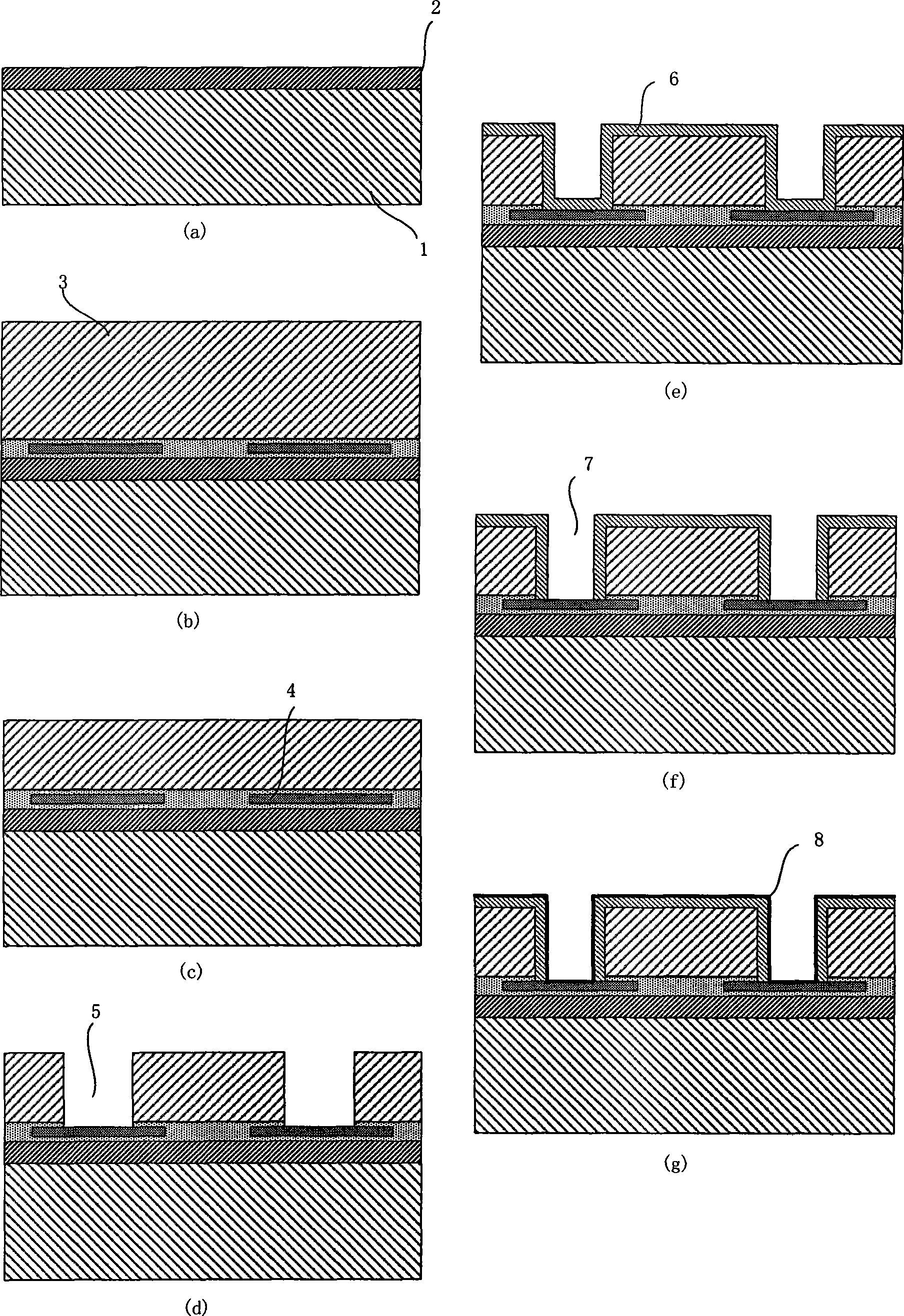

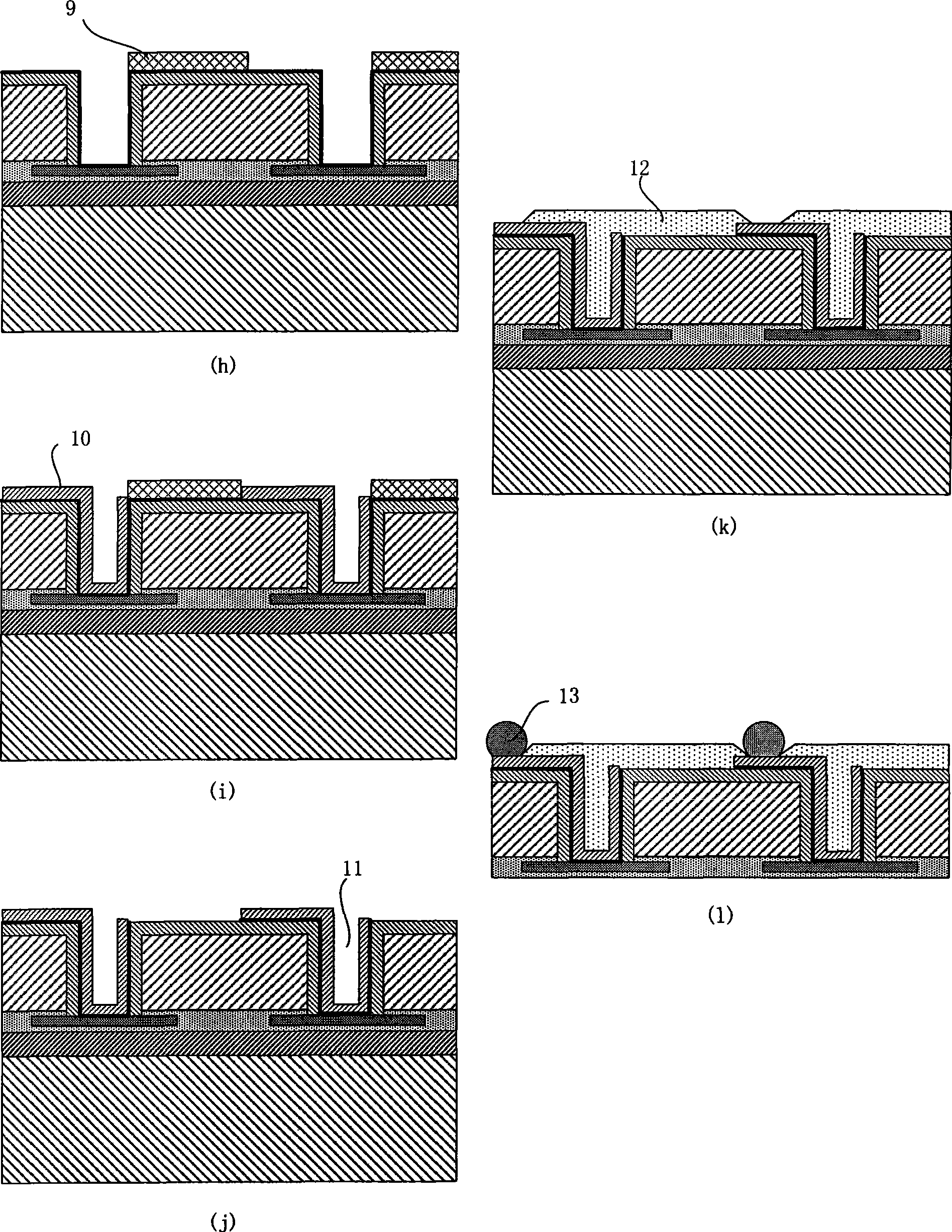

[0019] The specific embodiments of the process method provided by the present invention will be described in further detail below with reference to the accompanying drawings and examples. The method of the present invention includes:

[0020] (a) Provide a substrate 1 , such as a silicon wafer coated with an oxide layer 2 . The thickness of the substrate is 10-500 microns. see figure 1 (a).

[0021] (b) Bonding a silicon device wafer or chip 3 having at least one internal contact 4 on the silicon wafer. For example, aluminum pads and passivation layers can be fabricated on the front side of the device wafer or chip by flip-chip method to form internal contact points 4 . see figure 1 (b).

[0022] (c) Thinning silicon device wafers or chips by mechanical grinding. The grinding thickness is 25-100 microns. see figure 1 (c).

[0023] (d) dry etching the silicon device wafer or chip to form blind vias 5, the blind vias 5 having an aspect ratio of 5:1-20:1. These blind h...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More