Method for preparing metal-oxide-semiconductor field effect transistors (MOSFETs) with extremely short-gate length bulk-silicon surrounding gates

A technology of gate length and surrounding gate, which is applied in the field of microelectronic nanoscale complementary metal oxide semiconductor devices and extremely large-scale integration, can solve the problems of size reduction, large parasitic capacitance resistance, substrate pollution, etc., and achieve shortened gate length, Reduce parasitic capacitance and enhance shortening effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0075] 1) Double well process and advancement: N + The well is implanted into the Si substrate (104) using P 31+ , the energy is 110-150KeV, the dose is (1-2)e13, P + The well injected Si substrate (104) adopts B 11+ , the energy is 110-150KeV, the dose is (1-2)e13; and advance, the well depth is 1-2 microns;

[0076] 2) Isoplanar local oxidation (LOCOS) isolation, long field oxygen: 1000°C, 3000-5000 or Shallow Trench Isolation (STI);

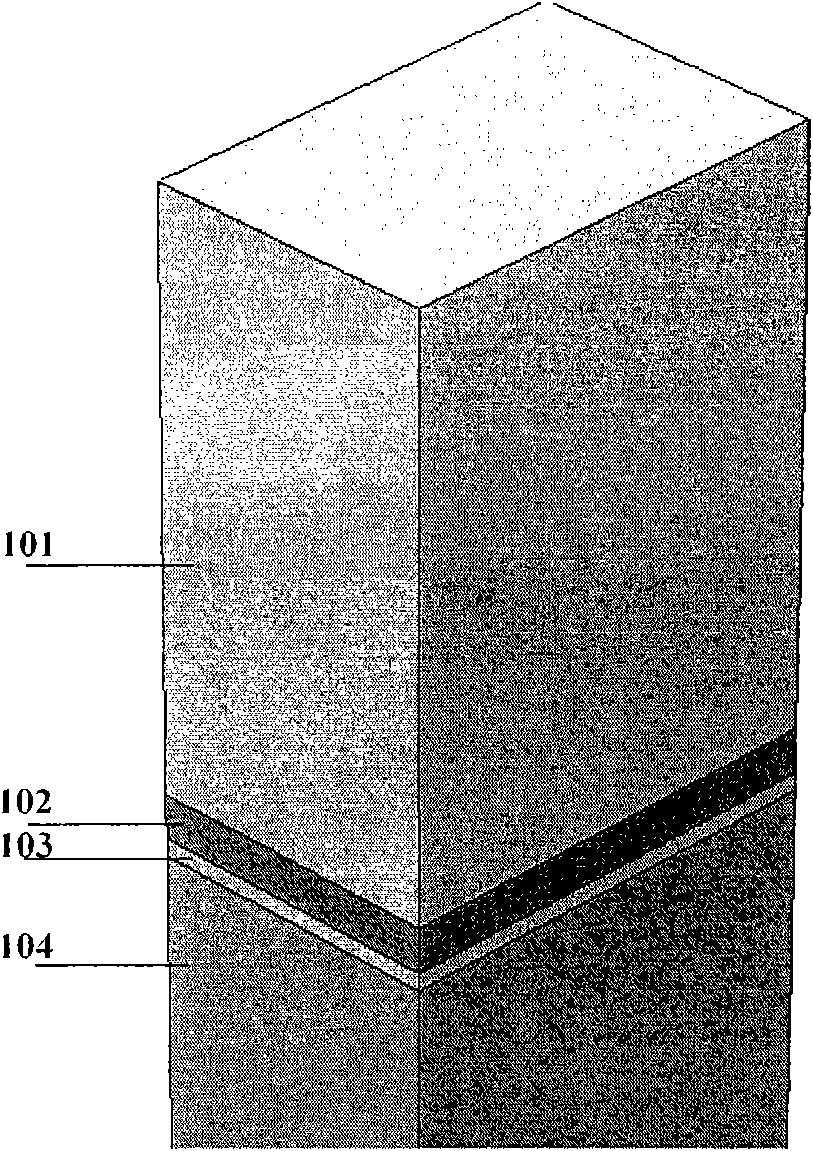

[0077] 3) As shown in Figure 1(a), CVD pads buffer SiO 2 Oxide layer (103) 15nm / SiN(102) 50nm / TEOS(101) 300nm three dielectric layers;

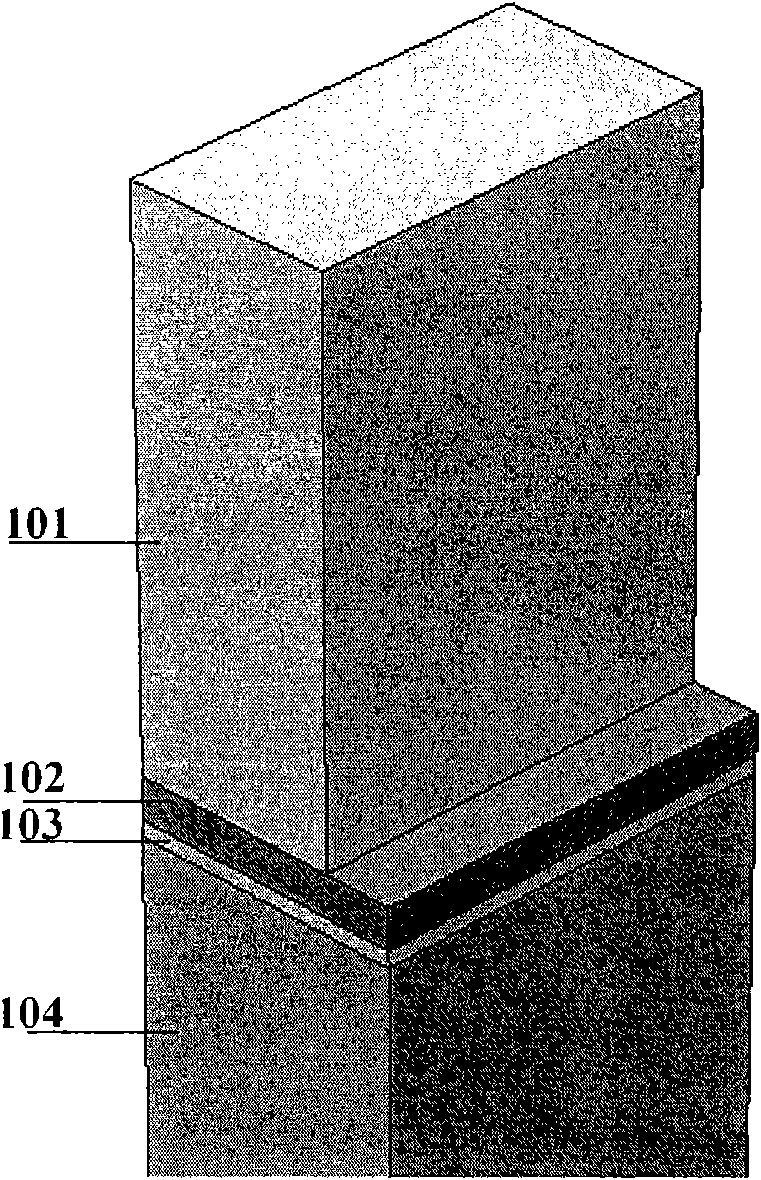

[0078] 4) As shown in Figure 1(b), a TEOS groove with a width of 120nm is etched with a positive electron beam exposure;

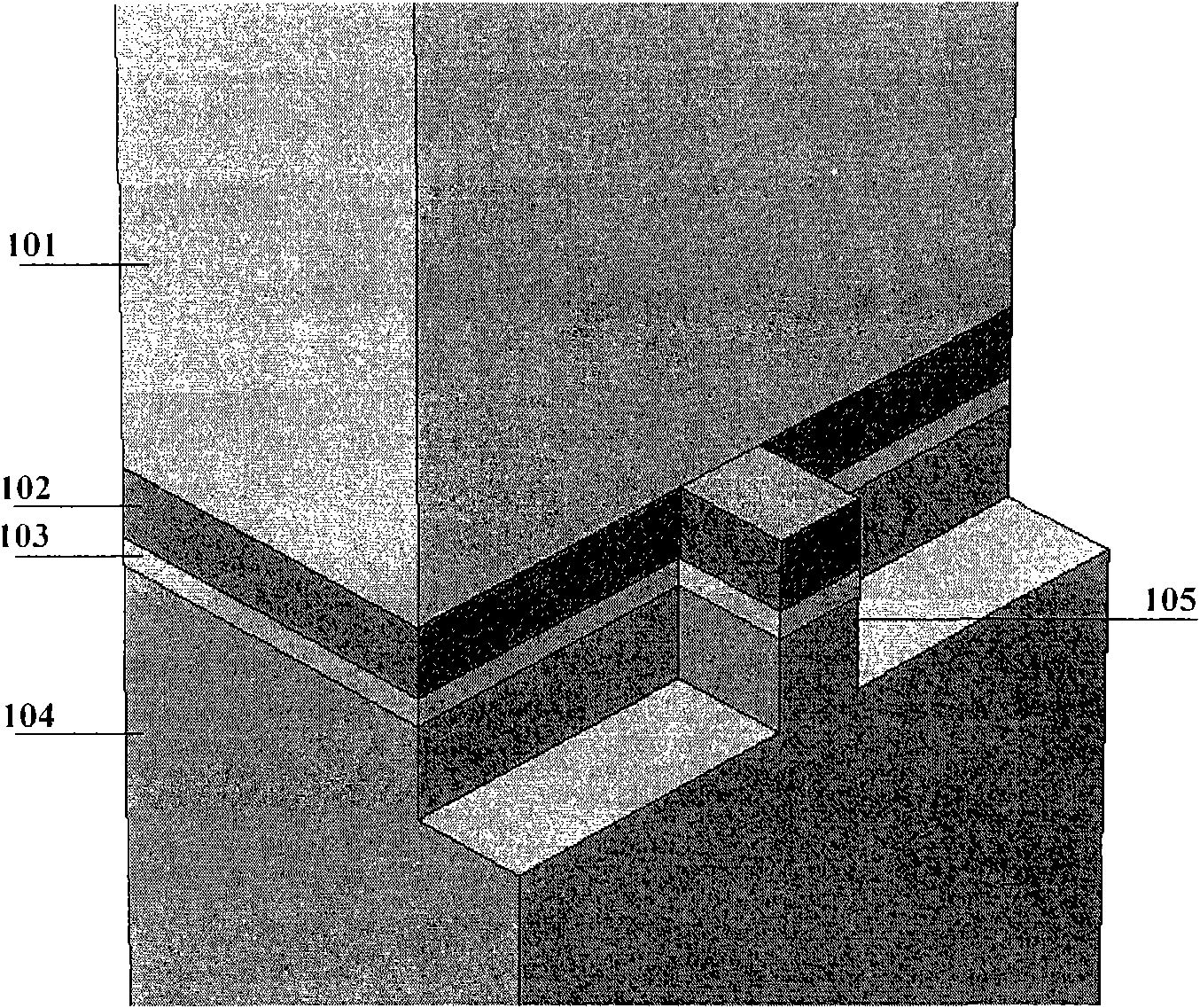

[0079] 5) As shown in Figure 1(c), use SAL601 negative electron beam exposure to etch SiN / buffered SiO in two steps in the TEOS groove 2 Oxide layer and steep fin islands (105) with a height of 100nm;

[0080] 6) As shown in Figure 1(d), build up an isotropic buffer oxide layer o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More