N-channel accumulative SiC IEMOSFET (Implantation and Epitaxial Metal-Oxide-Semiconductor Field Effect Transistor) device and manufacturing method thereof

An accumulation type and channel technology, applied in the field of microelectronics, can solve the problems of reduced electron mobility in the inversion layer, increased device on-resistance, and affecting device performance, achieving increased mobility, reduced on-resistance, The effect of simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

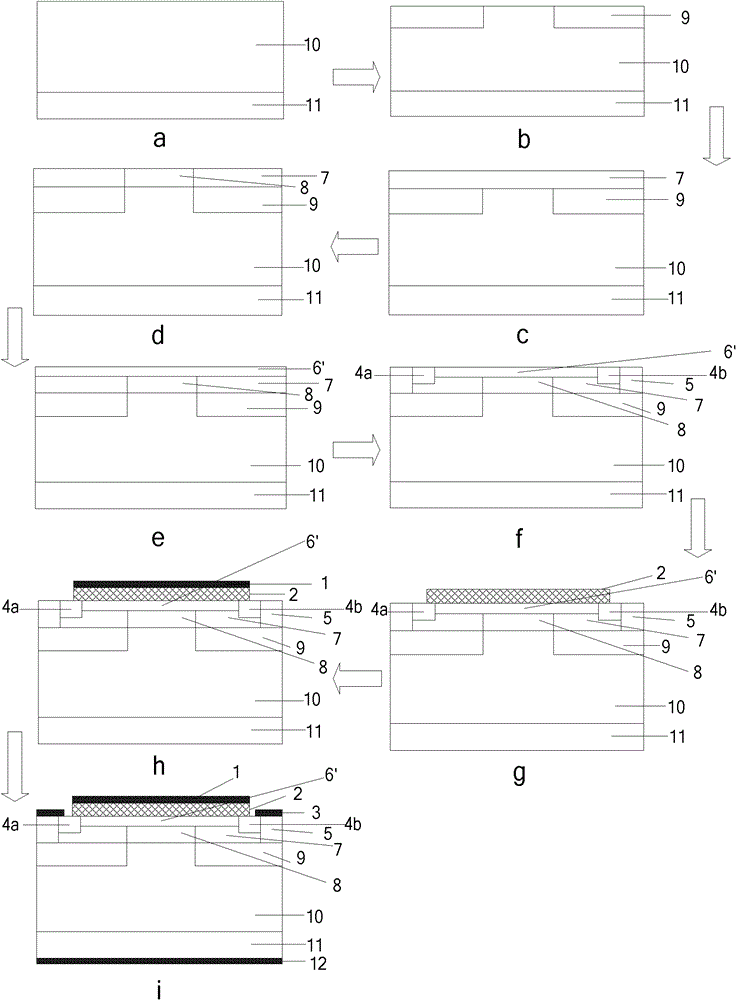

[0038] Step 1. In N + Epitaxial growth of N on SiC substrate - Drift layer.

[0039] to N + The silicon carbide substrate 11 was cleaned by RCA cleaning standard, and then epitaxially grown on the surface of the substrate with a thickness of 8 μm and a nitrogen ion doping concentration of 1×10 15 cm -3 N - Drift layer 10, such as image 3 a. The process conditions are as follows: the epitaxy temperature is 1570°C, the pressure is 100mbar, the reaction gas is silane and propane, the carrier gas is pure hydrogen, and the impurity source is liquid nitrogen.

[0040] Step 2. Multiple times of selective implantation of aluminum ions to form a P well.

[0041] (2.1) Deposit a layer of SiO with a thickness of 0.2 μm on the front side of the silicon carbide wafer by low-pressure hot-wall chemical vapor deposition 2 layer, and then deposit Al with a thickness of 1 μm as a barrier layer for the ion implantation of the P well 9, and form the P well implantation region by photolith...

Embodiment 2

[0068] Step 1. In N + Epitaxial growth of N on SiC substrate - Drift layer.

[0069] to N + The silicon carbide substrate 11 was cleaned by RCA cleaning standard, and then epitaxially grown on the surface of the substrate with a thickness of 8.5 μm and a nitrogen ion doping concentration of 1.5×10 15 cm -3 N - Drift layer 10, such as image 3 a. The process conditions are as follows: the epitaxy temperature is 1570°C, the pressure is 100mbar, the reaction gas is silane and propane, the carrier gas is pure hydrogen, and the impurity source is liquid nitrogen.

[0070] Step 2. Multiple times of selective implantation of aluminum ions to form a P well.

[0071] (2.1) Deposit a layer of SiO with a thickness of 0.2 μm on the front side of the silicon carbide wafer by low-pressure hot-wall chemical vapor deposition 2 layer, and then deposit Al with a thickness of 1 μm as a barrier layer for the ion implantation of the P well 9, and form the P well implantation region by photo...

Embodiment 3

[0098] Step A. In N + Epitaxial growth of N on SiC substrate - Drift layer.

[0099] to N + The silicon carbide substrate 11 is cleaned by RCA cleaning standard, and then epitaxially grown on the surface of the substrate with a thickness of 9 μm and a nitrogen ion doping concentration of 2×10 15 cm -3 N - Drift layer 10, such as image 3 a. The process conditions are as follows: the epitaxy temperature is 1570°C, the pressure is 100mbar, the reaction gas is silane and propane, the carrier gas is pure hydrogen, and the impurity source is liquid nitrogen.

[0100] Step B. multiple times of selective implantation of aluminum ions to form a P well.

[0101] (B1) Deposit a layer of SiO with a thickness of 0.2 μm on the front side of the silicon carbide wafer by low-pressure hot-wall chemical vapor deposition 2 layer, and then deposit Al with a thickness of 1 μm as a barrier layer for the ion implantation of the P well 9, and form the P well implantation region by photolithog...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More