Capacitance-free dynamic random access memory structure and preparation method thereof

A dynamic random, non-capacitive technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as reducing the probability of impact ionization, disturbance of gate dielectric data, and reduction of channel threshold voltage near the drain region. Achieve the effects of high-density three-dimensional process integration, suppression of gate dielectric degradation, and suppression of short channel effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

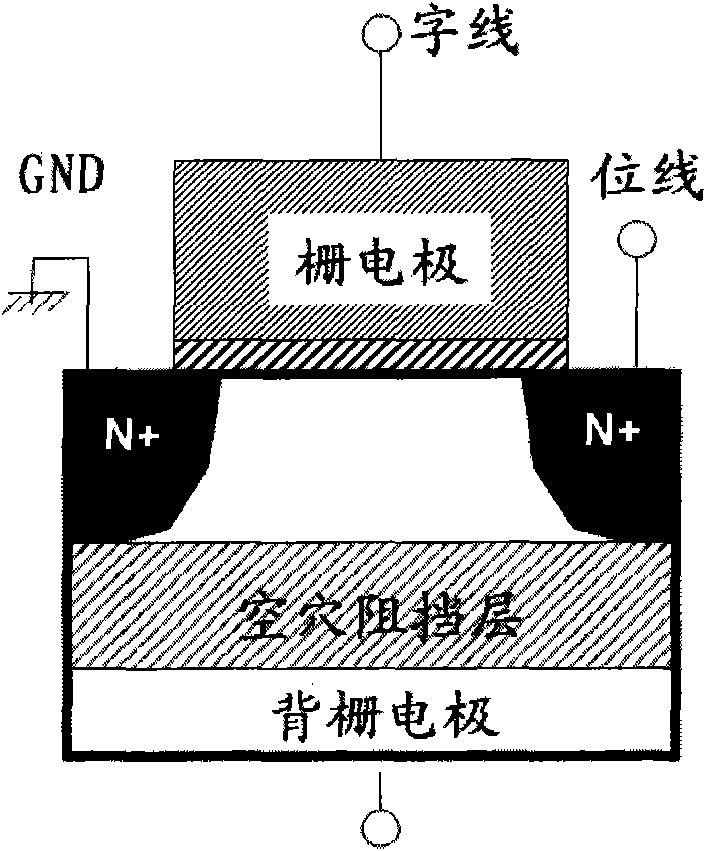

[0040] figure 1 is a schematic diagram of a conventional non-capacitance floating body memory cell structure, holes will be stored in the area close to the hole blocking layer. Here the hole blocking layer can be made of SiO 2 It can also be realized by using n-doped Si, or even by using SiGe, SiC, etc. At the same time, the substrate or the back gate can be grounded, and negative voltage bias can also be realized.

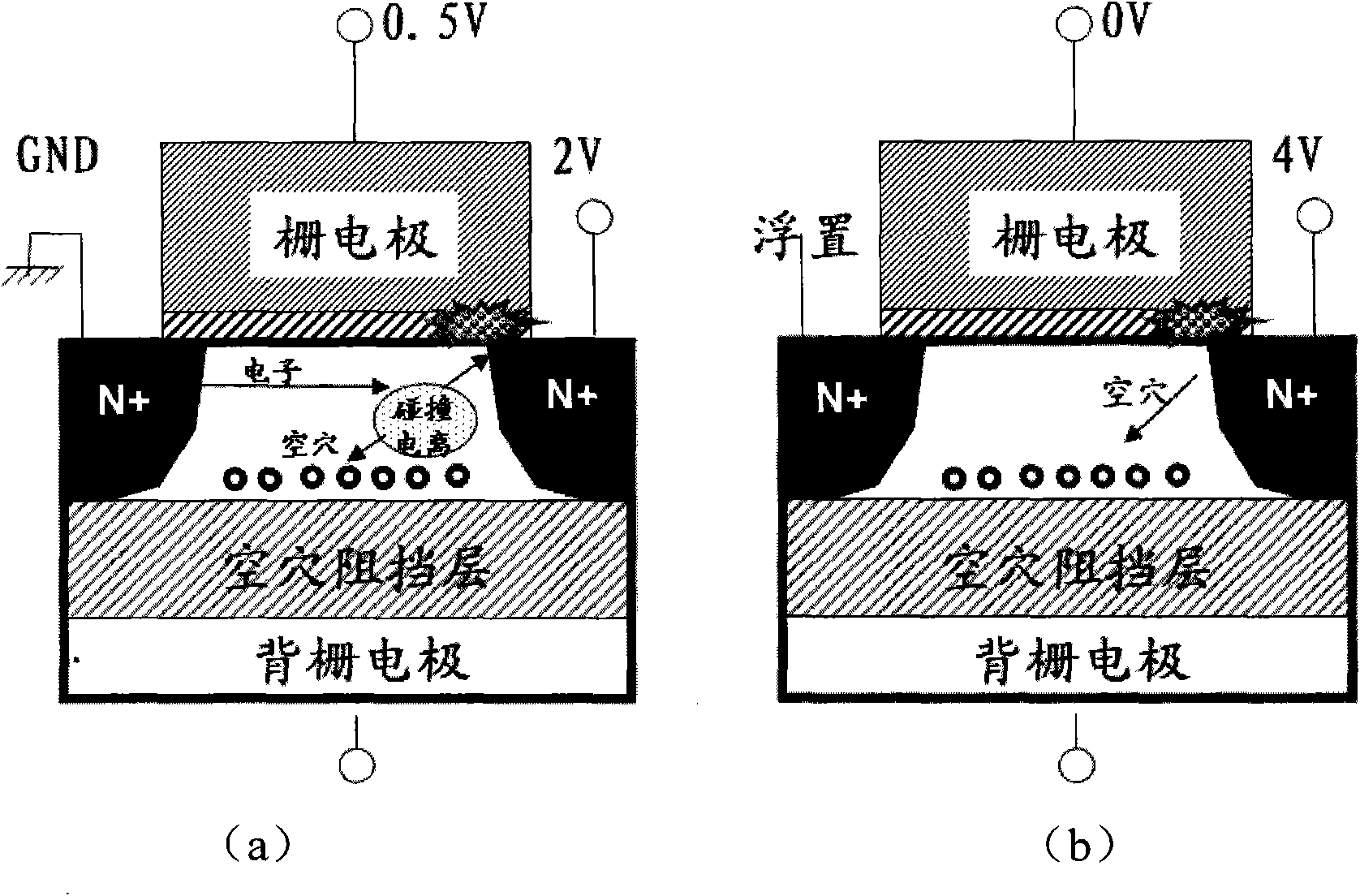

[0041] figure 2 It is a schematic diagram of two programming modes of a conventional floating body memory unit. In channel hot electron programming mode ( figure 2 a) Apply a large positive voltage such as 2V to the drain, and apply a transistor turn-on voltage such as 0.5V to the gate. The source vol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More