DMOS device and manufacturing method thereof

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as peeling of covering layers, old packaging equipment, and metal defects, so as to improve accuracy, ILD layer and metal The effect of tight interface

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

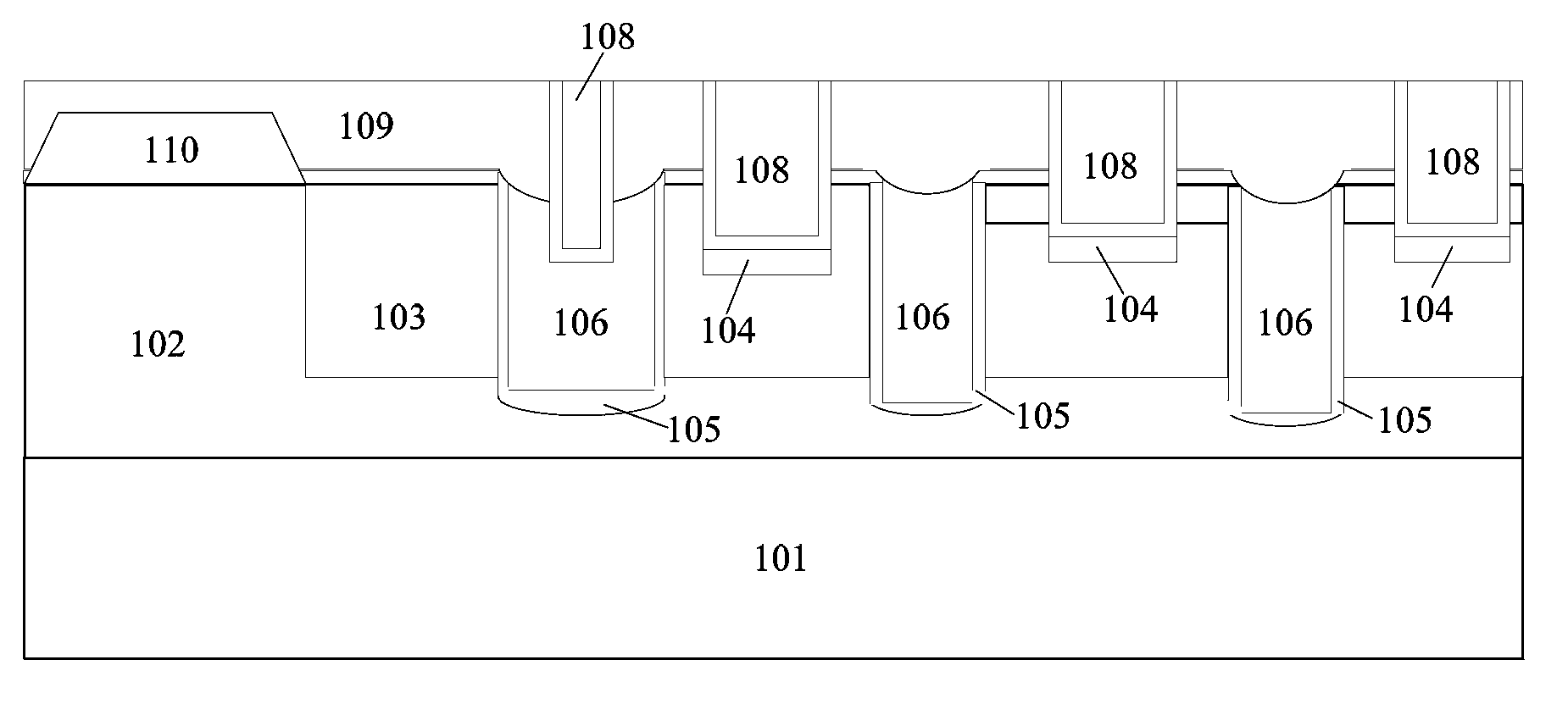

[0044] The cross-sectional view of each step of the DMOS device manufacturing method disclosed in the embodiment of the present invention is as follows image 3 and Figure 4 shown, including the following steps:

[0045]Step 1: provide a substrate, the substrate includes an active region and an interlayer dielectric ILD layer 109 on the surface of the active region, wherein the ILD layer on the surface of the active region has a tungsten plug 108, the ILD The surface of the layer 109 is flush with the surface of the tungsten plug 108;

[0046] It should be noted that the substrate in this embodiment may include semiconductor elements, such as silicon or silicon germanium (SiGe) in single crystal, polycrystalline or amorphous structure, or mixed semiconductor structures, such as silicon carbide, indium antimonide , lead telluride, indium arsenide, indium phosphide, gallium arsenide or gallium antimonide, alloy semiconductors or combinations thereof; also silicon-on-insulator...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More