Method for manufacturing field cut-off type insulated gate bipolar transistor

A technology of bipolar transistors and insulated gates, applied in transistors, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of deep impurity advancement, difficulty in thinning thickness, and unsatisfactory concentration distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The specific implementation manners of the present invention will be described in detail below in conjunction with the accompanying drawings.

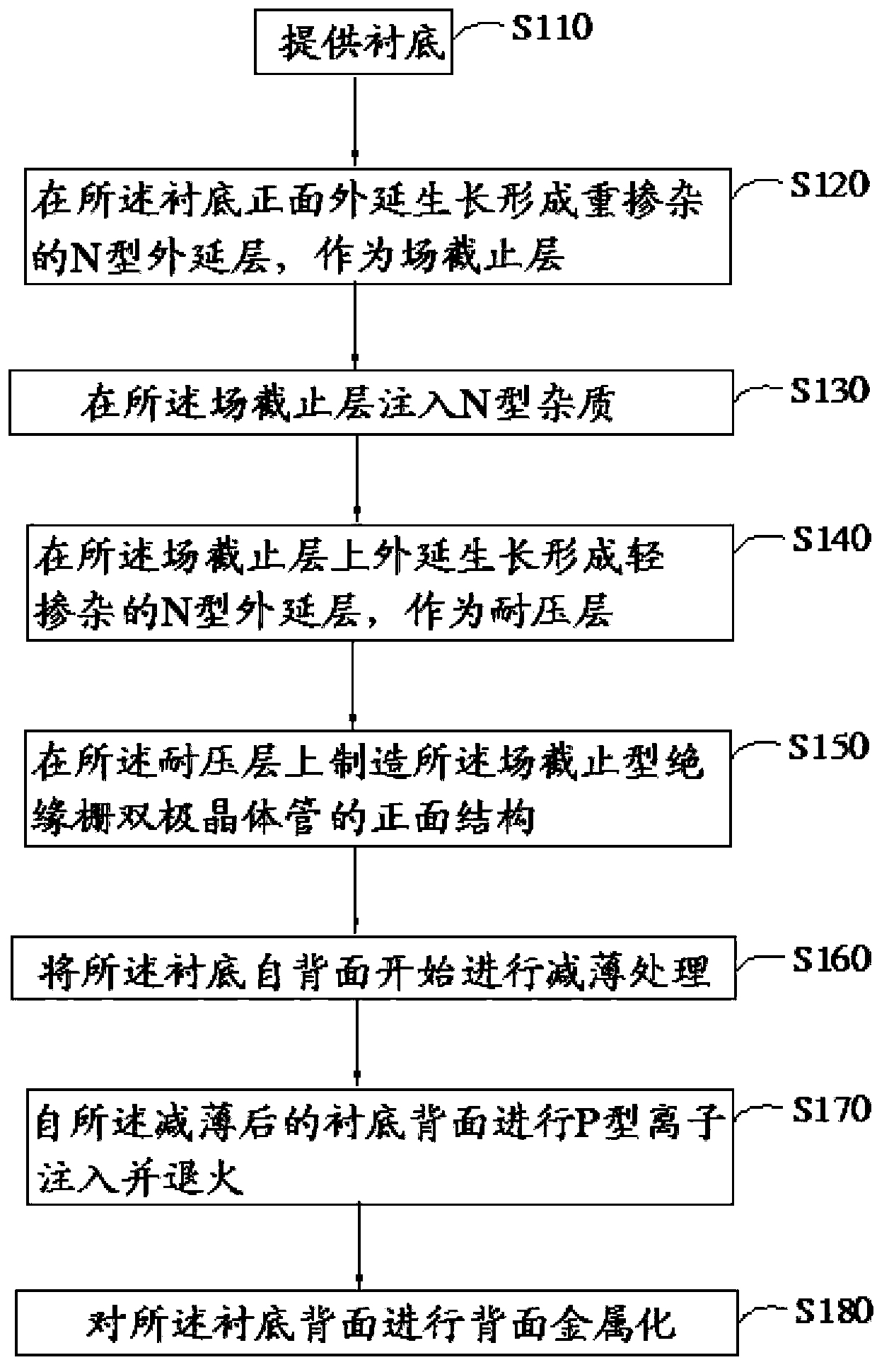

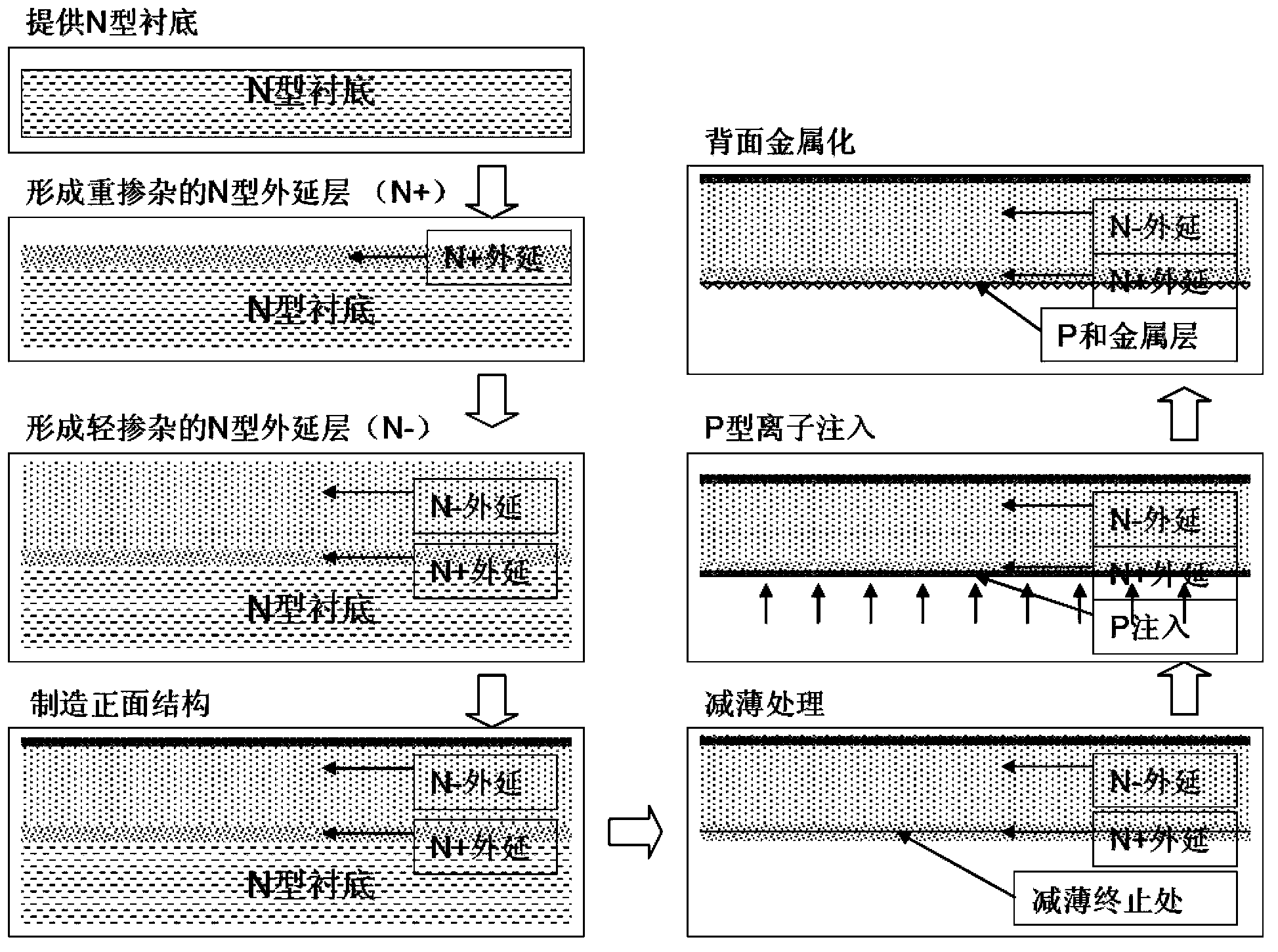

[0031] figure 1 It is a flowchart of an embodiment of the present invention, including:

[0032] Step S110: providing a substrate.

[0033] Choose a suitable type of substrate, either P-type or N-type. Because the substrate will eventually be thinned and eliminated, the selection is relatively free, and a lower-cost substrate can be selected. The substrate resistivity depends on the requirements of different IGBT products, the resistivity ranges from 0.001 to 200 ohm·m, and the substrate thickness ranges from 100 to 1000 microns.

[0034] Step S120: epitaxially growing a heavily doped N-type epitaxial layer (N+) on the front side of the substrate as a field stop layer.

[0035] Vapor phase epitaxy is used to epitaxially grow a heavily doped N-type epitaxial layer as a field stop layer. The thickness and resistivity of the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More