Low temperature polycrystalline silicon thin film, thin film transistor and respective manufacturing method and display device

A low-temperature polysilicon and thin film transistor technology, which is applied in transistors, semiconductor/solid-state device manufacturing, electric solid-state devices, etc. Effect of grain size improvement, grain boundary position improvement, and electrical properties improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

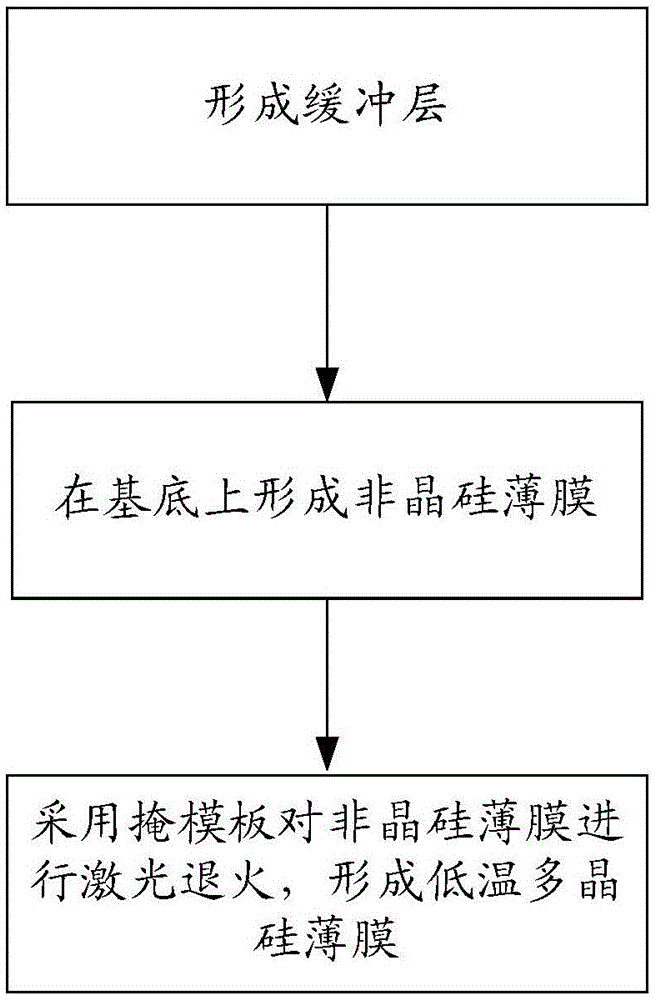

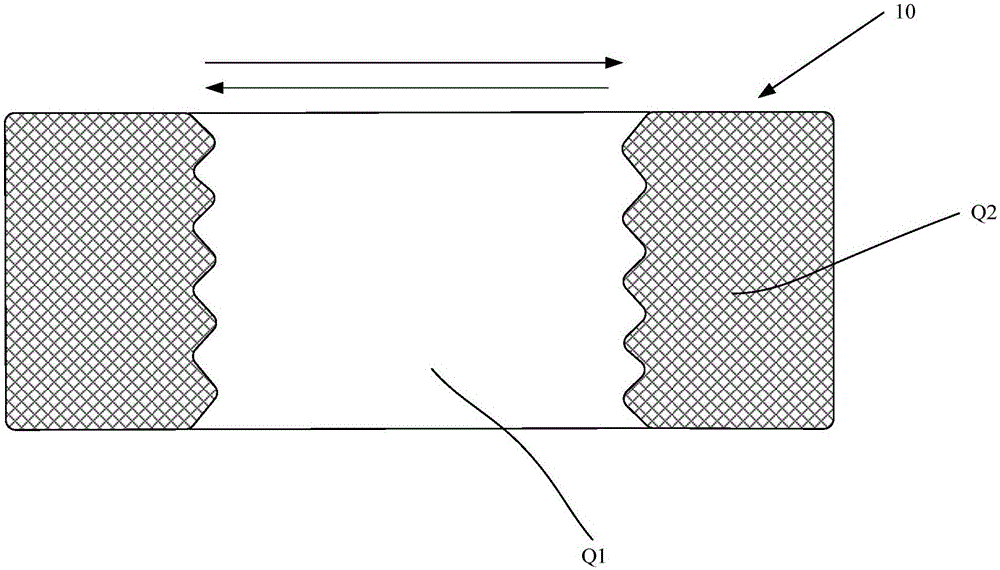

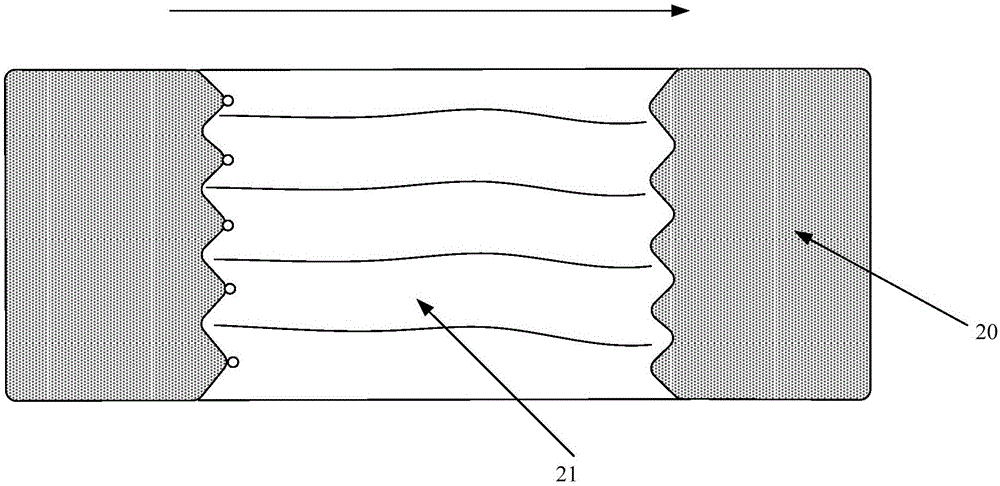

[0044] Such as Figure 1-3 As shown, this embodiment provides a method for preparing a low-temperature polysilicon thin film, comprising the following steps:

[0045] Step 1, forming a buffer layer on the substrate.

[0046] In this step, the substrate is made of a transparent material such as glass and is pre-cleaned. Specifically, sputtering, thermal evaporation, plasma enhanced chemical vapor deposition (PlasmaEnhancedChemicalVaporDeposition: PECVD for short), low pressure chemical vapor deposition (LowPressureChemicalVaporDeposition: LPCVD for short), atmospheric pressure chemical vapor deposition (AtmosphericPressureChemicalVaporDeposition: APCVD) or electron cyclotron resonance chemical vapor deposition (Electron Cyclotron Resonance Chemical Vapor Deposition: ECR-CVD for short) to form the buffer layer.

[0047] Wherein, the buffer layer includes at least one layer of silicon oxide and silicon nitride. In addition, the thickness of the buffer layer may be 150nm to 300...

Embodiment 2

[0060] Such as Figure 4 , 5 As shown, this embodiment provides a method for preparing a low-temperature polysilicon thin film transistor, which includes the steps of preparing a low-temperature polysilicon thin film described in Embodiment 1. Specifically, the preparation of a top-gate transistor is taken as an example for illustration.

[0061] Step 1, forming a buffer layer on the substrate.

[0062] In this step, the substrate is made of a transparent material such as glass and is pre-cleaned. Specifically, a buffer layer is formed on the substrate 1 by sputtering, thermal evaporation, plasma enhanced chemical vapor deposition, low pressure chemical vapor deposition, atmospheric pressure chemical vapor deposition or electron cyclotron resonance chemical vapor deposition.

[0063] Wherein, the buffer layer includes at least one layer of silicon oxide and silicon nitride, with a thickness of 150nm to 300nm. The reason for preparing such a thick buffer layer is to form an...

Embodiment 3

[0085] This embodiment provides a display device, which includes the above-mentioned low-temperature polysilicon thin film transistor, so the display effect of the display device of this embodiment is better.

[0086] The display device can be any product or component with a display function such as a liquid crystal panel, an electronic paper, an OLED panel, a mobile phone, a tablet computer, a television, a monitor, a notebook computer, a digital photo frame, a navigator, and the like.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More