Formation method of semiconductor structure

A semiconductor and plasma technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of fin-type field effect transistors whose performance needs to be further improved and large leakage current.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

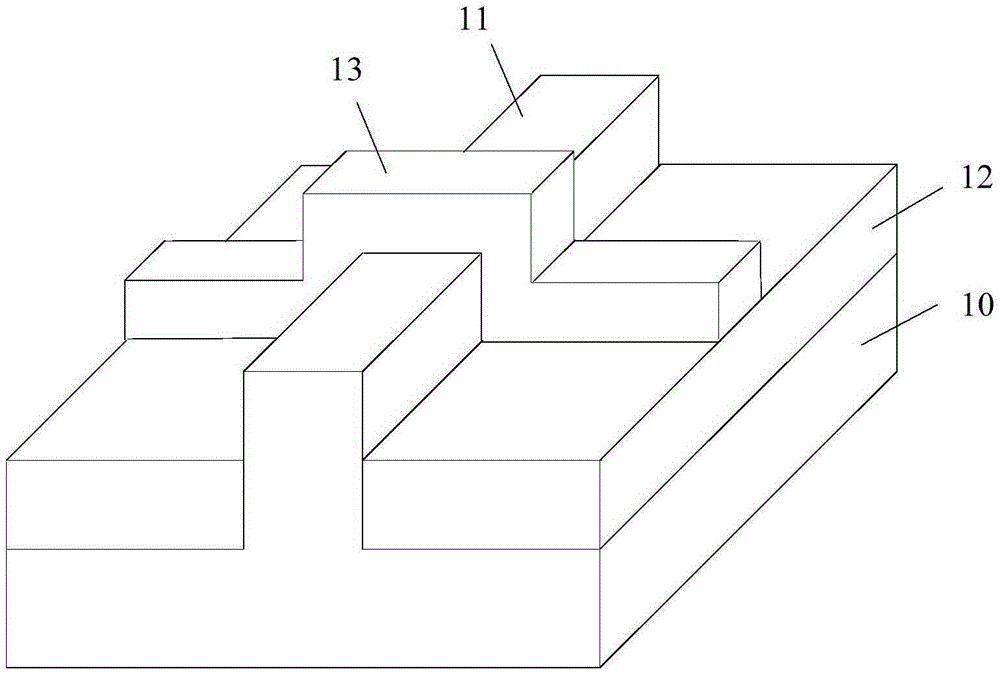

[0032] The structure of the silicon-on-insulator substrate includes: a bottom silicon layer, a buried oxide layer on the surface of the bottom silicon layer, and a top silicon layer on the surface of the buried oxide layer. Forming a semiconductor device on an insulating silicon substrate can effectively reduce the leakage current of the semiconductor device and improve the performance of the semiconductor device.

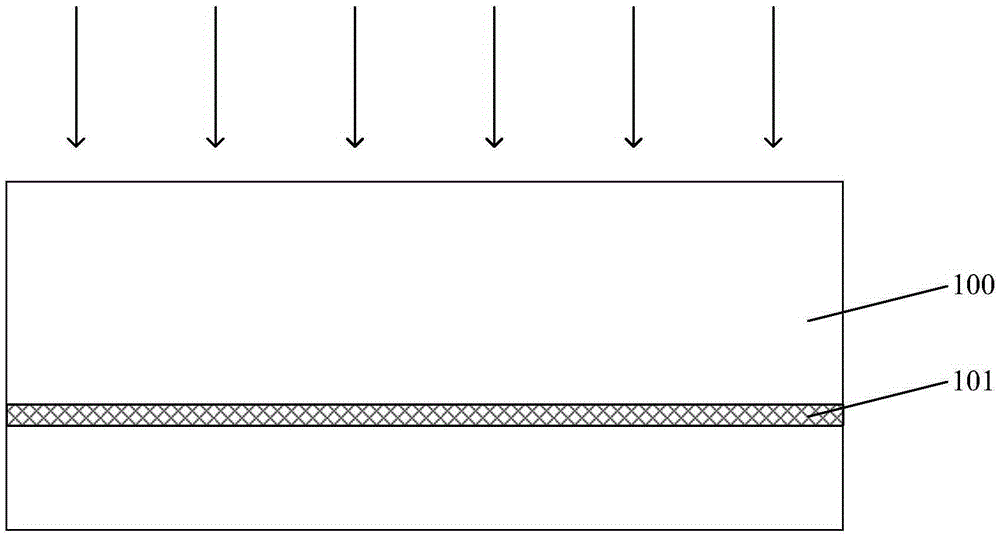

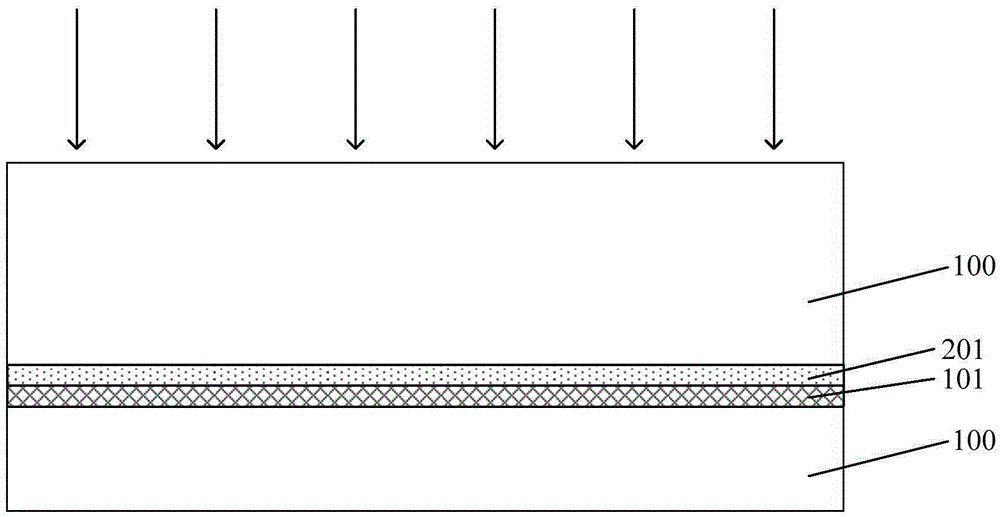

[0033] Oxygen ions can be implanted into bulk silicon by ion implantation to form a buried oxide layer in bulk silicon, thereby forming a silicon-on-insulator structure, but the ion implanter used for ion implantation usually takes a long time to reach the required level for forming the buried oxide layer. required implant dose, resulting in low efficiency and high cost for forming silicon-on-insulator substrates. In the plasma implantation process, the implantation dose is relatively large, and the implantation dose has nothing to do with the implantation time and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More