Preparation methods of SiC device gate dielectric layer and SiC device structure

A technology of gate dielectric layer and device structure, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of low critical breakdown strength, high thermal budget of gate dielectric layer, large leakage current, etc., to avoid C Cluster aggregation, high critical breakdown strength, and low leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

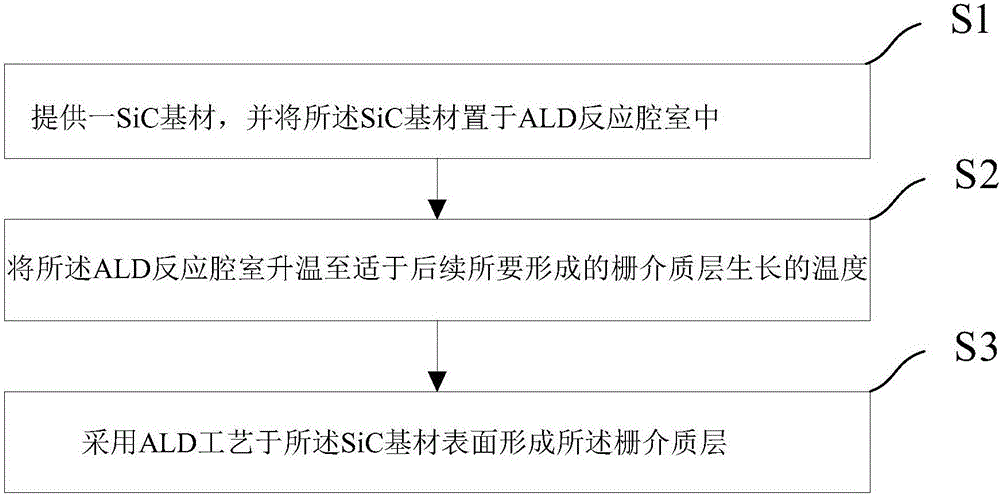

[0071] Such as figure 1 As shown, the present invention provides a method for preparing a gate dielectric layer of a SiC device, comprising the following steps:

[0072] 1) providing a SiC substrate, and placing the SiC substrate in an ALD reaction chamber;

[0073] 2) raising the temperature of the ALD reaction chamber to a temperature suitable for the subsequent growth of the gate dielectric layer to be formed;

[0074] 3) Forming the gate dielectric layer on the surface of the SiC substrate by using an ALD process.

[0075] The method for preparing the gate dielectric layer of the SiC device of the present invention will be described in detail below with reference to the accompanying drawings.

[0076] Such as figure 1 Shown in S1 in, carry out step 1), provide a SiC substrate, and described SiC substrate is placed in the ALD reaction chamber;

[0077] Specifically, the SiC base material includes but is not limited to SiC epitaxial wafers. In this embodiment, the SiC ba...

Embodiment 2

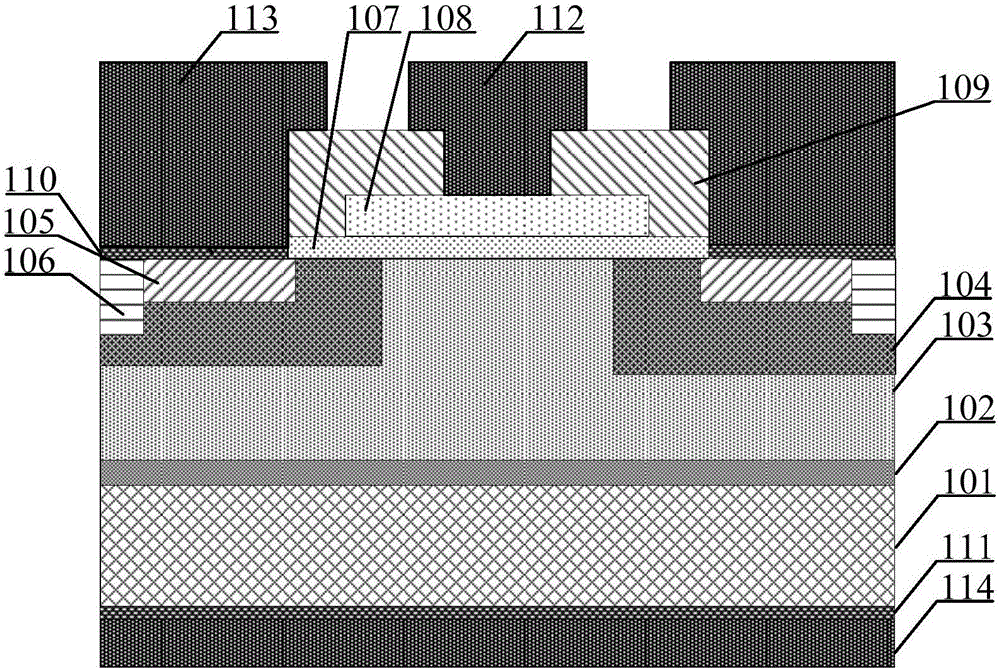

[0118] Such as figure 2 As shown, the present invention provides a method for preparing a SiC device structure, including the step of preparing a gate dielectric layer by using the method for preparing a gate dielectric layer of a SiC device as described in any one of Embodiment 1.

[0119] As an example, the method for preparing the SiC device structure includes the following steps:

[0120] 1) A heavily doped substrate of the first doping type is provided, such as a SiC substrate 101, and the substrate has a first surface and a second surface, and a lightly doped substrate of the first doping type is formed on the first surface. Doped SiC epitaxial layer 103;

[0121] 2) defining a gate structure region in the SiC epitaxial layer, and forming a second-type doped annular well region, such as a P-type well region 104, in the SiC epitaxial layer surrounding the gate structure region;

[0122] 3) Forming a heavily doped source region of the first doping type in the well regio...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More