High-performance normally-off GaN field effect transistor and preparation method thereof

A field-effect transistor, normally-off technology, applied in the field of semiconductor device preparation, can solve the problem of reducing the two-dimensional electron gas concentration of the conductive channel in the access area, deteriorating the quality of the secondary epitaxial heterogeneous structure, and detrimental to the conduction performance of the device, etc. problems, to achieve the effect of maintaining high quality, process repeatability and reliability, and improving conduction performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0033] Such as Figure 11 Shown is a schematic diagram of the device structure of this embodiment, and its structure includes a substrate 1, a stress buffer layer 2, and a GaN channel layer 3 from bottom to top. Sub-epitaxial layer 4, remove the gate mask to form a groove gate structure and deposit a layer of gate dielectric layer 5 on the surface, remove the gate dielectric layer at both ends of the device to form source 6 and drain 7, and gate dielectric in the groove gate region The layer is covered with a gate 8 .

[0034] The preparation method of the above-mentioned high-performance normally-off GaN field-effect transistor is as follows: Figure 1-Figure 10shown, including the following steps:

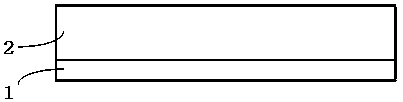

[0035] S1, utilize metal-organic chemical vapor deposition method to grow a layer of stress buffer layer 2 on Si substrate 1, such as figure 1 shown;

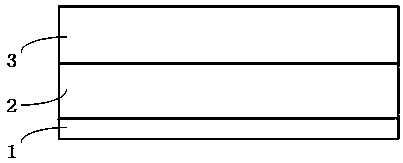

[0036] S2. Using a metal organic chemical vapor deposition method to grow a GaN channel layer 3 on the stress buffer layer ...

Embodiment 2

[0048] Figure 12-14 For the preparation of SiO on the gate region in Example 2 of the present invention 2 Schematic diagram of the process of the mask layer, which is similar to that of SiO on the gate region in Example 1 2 The only difference in the preparation method of the mask layer is that in Example 1, reactive coupled plasma etching is used to form the mask pattern on the gate region, while in Example 2, a lift-off method is used to form the mask pattern on the gate region. film graphics. The specific process includes the following steps:

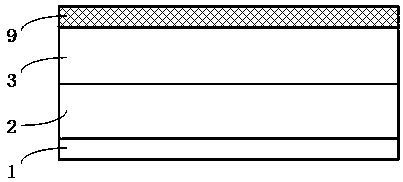

[0049] S1. A photoresist protection layer 10 with a patterned structure is partially formed on the secondary epitaxial layer 3, such as Figure 12 shown;

[0050] S2. Deposit a layer of SiO on the substrate with the photoresist protection layer 10 by plasma enhanced chemical vapor method 2 , as mask layer 9, such as Figure 13 shown;

[0051] S3, using photoresist stripping solution to remove photoresist protective layer 10, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More