AlGaN/GaN heterojunction HEMT device compatible with Si-CMOS technology and manufacturing method thereof

A heterojunction and process technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as lower product yield, epitaxial layer cracking, CMOS process line pollution, etc., to avoid pollution and improve device performance. performance, the effect of lowering the process temperature

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The specific implementation of the present invention will be further described below in conjunction with drawings and examples, but the implementation and protection of the present invention are not limited thereto. It can be realized with reference to the prior art.

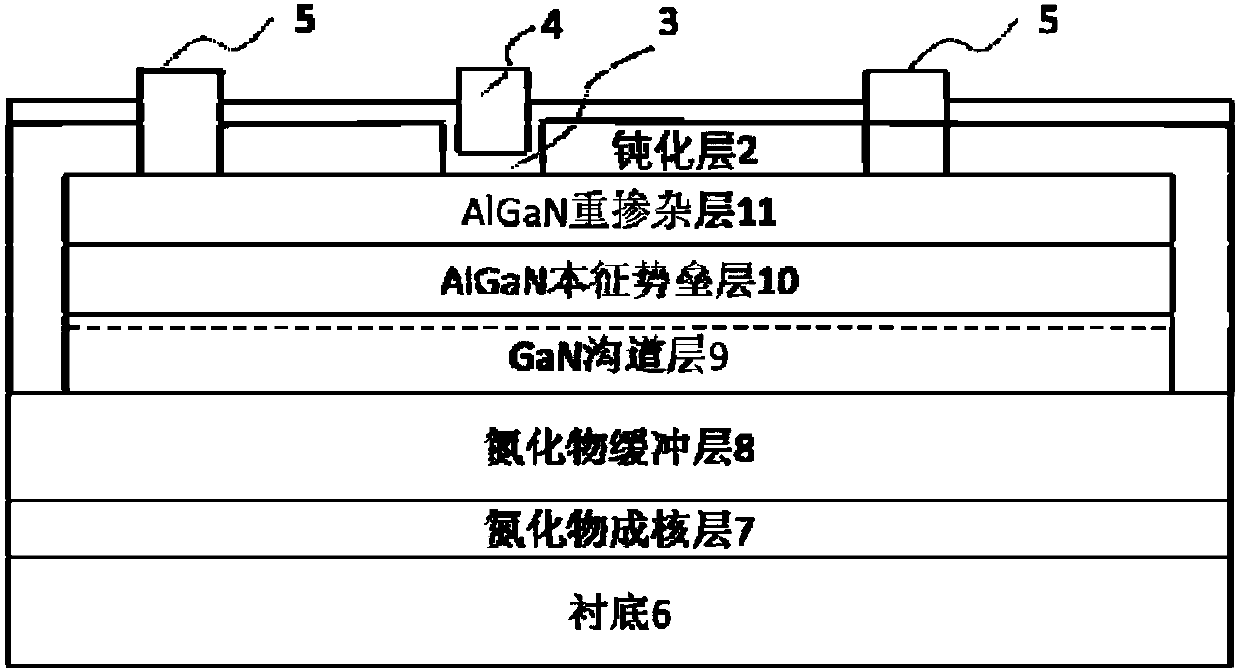

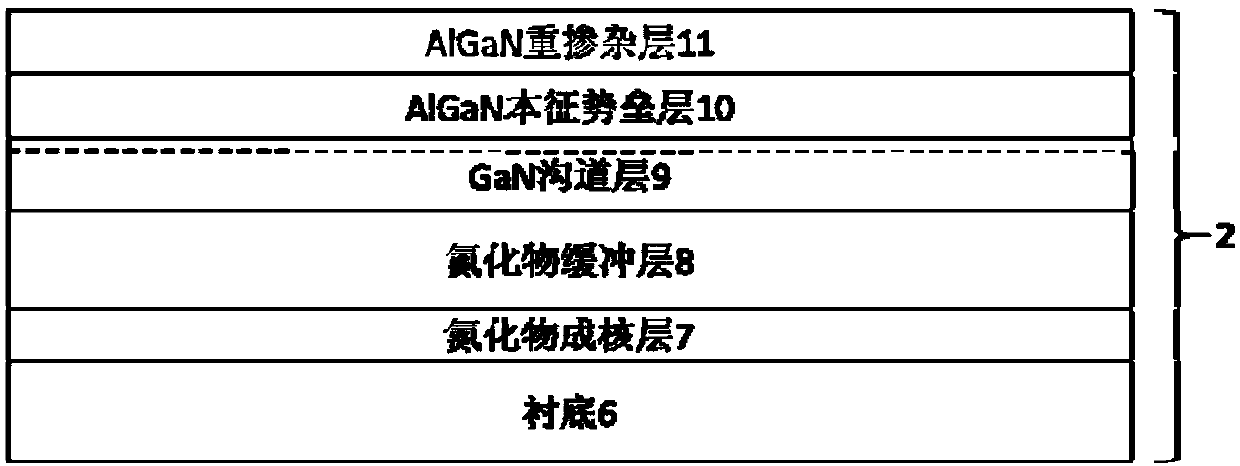

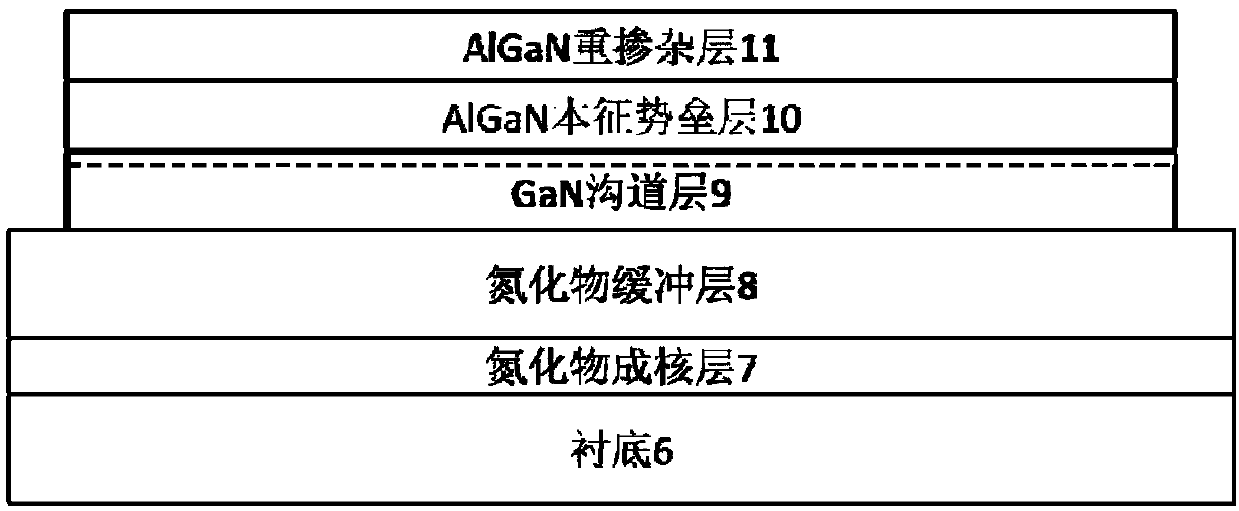

[0037] refer to figure 1 , an AlGaN / GaN heterojunction HEMT device compatible with Si-CMOS technology and its manufacturing method, the device includes: AlGaN / GaN heterojunction epitaxial layer 1, passivation layer 2, gate dielectric layer 3, gold-free gate electrode 4. No gold source and drain electrodes5. The AlGaN / GaN heterojunction epitaxial layer sequentially includes a substrate 6, a nitride nucleation layer 7, a nitride buffer layer 8, a GaN channel layer 9, an AlGaN intrinsic barrier layer 10, and an AlGaN heavily doped layer from bottom to top. Miscellaneous layer 11.

[0038] The substrate 6 of the AlGaN / GaN heterojunction epitaxial layer 1 is made of silicon, the nitride nucleation layer 7 i...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More